一种SARADC及其回踢噪声影响的降低方法与流程

本发明涉及微电子,更具体地,涉及一种saradc及其回踢噪声影响的降低方法。

背景技术:

1、通常高速saradc的回踢发生在比较器的输入端,该点是整个adc模拟信号的交汇点,对噪声非常敏感,如果pn两端的阻抗不同,则回踢会非均匀的耦合到电容阵列的参考端,即saradc的参考驱动上,进而共模的噪声转化为差模的噪声,引入非线性。

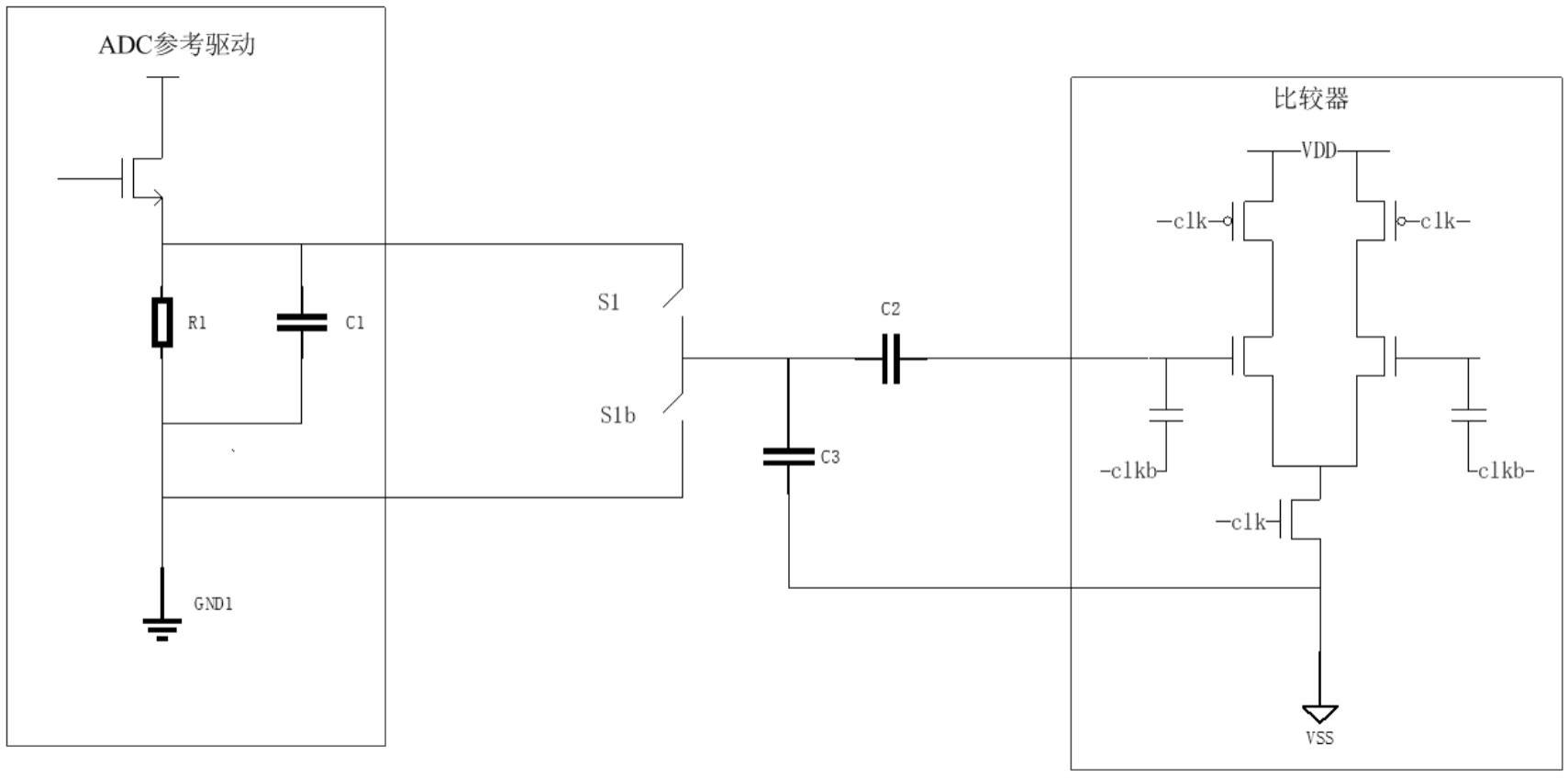

2、针对两级比较器,目前通常的解决办法是在比较器的输入端加入回踢抵消电容,通过反向的回踢将由于回踢造成的电荷损失补偿回来,如图所示,是一个比较器的第一级,两个接在比较器输入的电容容值与输入管的cgd一致。

3、时钟下降沿时候,比较起reset,由输入管cgd引入较大的回踢噪声,输入挂接的两颗电容容值与cgd一致,通过反向注入电荷,抵消了一部分回踢噪声。

4、现有技术的缺点

5、第一个缺点是,高速比较器往往速度极快,为了保证比较器的延迟与分辨率,输入管通常较大,为了实现回踢噪声的抵消,接在clkb上的电容通常要求与输入对管引入的寄生电容一致,该电容较大,由于工作时该电容接在电容阵列顶板上,故会造成额外的增益误差。

6、第二个缺点来源于版图,由于比较器输入级的面积通常较大,该架构又要求额外的绕线连接反相时钟,故该架构的面积较大。

7、因此,如何提供一种saradc及其回踢噪声影响的降低方法成为本领域亟需解决的技术难题。

技术实现思路

1、本发明的目的是提供一种saradc及其回踢噪声影响的降低方法。

2、根据本发明的第一方面,提供了一种saradc回踢噪声影响的降低方法,包括,在adc参考驱动的偏置电阻两端并联第一滤波电容;第二滤波电容的一端连接在adc参考驱动的第一开关与第二开关之间和电容阵列上,所述第二滤波电容的另一端连接在比较器的接地端,所述电容阵列的一端连接在adc参考驱动的第一开关与第二开关之间,所述电容阵列的另一端连接在所述比较器的输入端。

3、可选地,第一滤波电容应当满足:

4、1/(2×π×r1×c1)= fsw

5、其中,c1为第一滤波电容,r1为adc参考驱动的偏置电阻,fsw为第一开关s1与第二开关s1b的动作频率。

6、可选地,所述第二滤波电容与电容阵列的底板之间小于预设距离。

7、可选地,所述第二滤波电容的电容值等于第一滤波电容的电容值。

8、可选地,所述第二滤波电容布置方法包括:

9、1. 在原本的电容阵列c2底板处增加额外的版图走线结构,等效于增加c2底板对地的电容,如图2所示。

10、2. 在c2的底板与地之间增加滤波电容。

11、根据本发明的第二方面,提供了一种saradc,包括本发明第一方面任一项所述的saradc回踢噪声影响的降低方法。

12、根据本发明公开的技术内容,具有如下有益效果:通过简单有效的方法,减弱回踢噪声对参考驱动的影响,进而提升整体saradc的sfdr。

13、通过以下参照附图对本发明的示例性实施例的详细描述,本发明的其它特征及其优点将会变得清楚。

技术特征:

1.一种saradc回踢噪声影响的降低方法,其特征在于,包括:在adc参考驱动的偏置电阻两端并联第一滤波电容;第二滤波电容的一端连接在adc参考驱动的第一开关与第二开关之间,所述第二滤波电容的另一端连接在比较器的接地端,电容阵列的一端连接在adc参考驱动的第一开关与第二开关之间,所述电容阵列的另一端连接在所述比较器的输入端。

2.根据权利要求1所述的saradc回踢噪声影响的降低方法,其特征在于,第一滤波电容应当满足:

3.根据权利要求1所述的saradc回踢噪声影响的降低方法,其特征在于,所述第二滤波电容与电容阵列的底板之间小于预设距离。

4.根据权利要求1所述的saradc回踢噪声影响的降低方法,其特征在于,所述第二滤波电容的电容值等于第一滤波电容的电容值。

5.根据权利要求1所述的saradc回踢噪声影响的降低方法,其特征在于,所述第二滤波电容紧贴所述电容阵列放置。

6.一种saradc,其特征在于,包括权利要求1-5任一项所述的saradc回踢噪声影响的降低方法。

技术总结

本发明公开了一种SARADC及其回踢噪声影响的降低方法,包括:在ADC参考驱动的偏置电阻两端并联第一滤波电容;第二滤波电容的一端连接在ADC参考驱动的第一开关与第二开关之间,所述第二滤波电容的另一端连接在比较器的接地端,所述电容阵列的一端连接在ADC参考驱动的第一开关与第二开关之间,所述电容阵列的另一端连接在所述比较器的输入端。本发明公开的技术内容,通过简单有效的方法,减弱回踢噪声对参考驱动的影响,进而提升整体SARADC的SFDR。

技术研发人员:胡国盛

受保护的技术使用者:芯迈微半导体(上海)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!