PLL电路及相位噪声测量方法与流程

本申请涉及锁相环(phase-locked loops,简称pll)电路,具体地涉及一种pll电路及相位噪声测量方法。

背景技术:

1、pll电路是一种利用反馈控制原理实现频率及相位同步的技术,其作用是将电路输出的时钟与外部参考时钟保持同步。当参考时钟的频率或者相位发生改变时,pll电路可以检测到该种变化,并且可以通过内部的反馈系统来调节输出频率,直到两者重新同步,这种同步称为“锁相”。

2、相位噪声是指在各种噪声的作用下所引起的电路输出信号相位的随机变化。相位噪声是衡量pll电路频率稳定性的一项重要指标。相关技术中测量pll电路相位噪声的方法普遍存在一些问题,如未充分考虑pll电路各模块之间的串扰导致测量的相位噪声不准确;又例如,测量pll电路的相位噪声之前需要控制pll电路进入指定的稳定状态,但整个pll电路进入指定稳定状态或者难以实现或者需要较长时间,影响测量pll电路相位噪声的测量效率。

技术实现思路

1、有鉴于此,本申请提供一种pll电路及相位噪声测量方法,有助于提高pll电路相位噪声测量的稳定性和准确性。

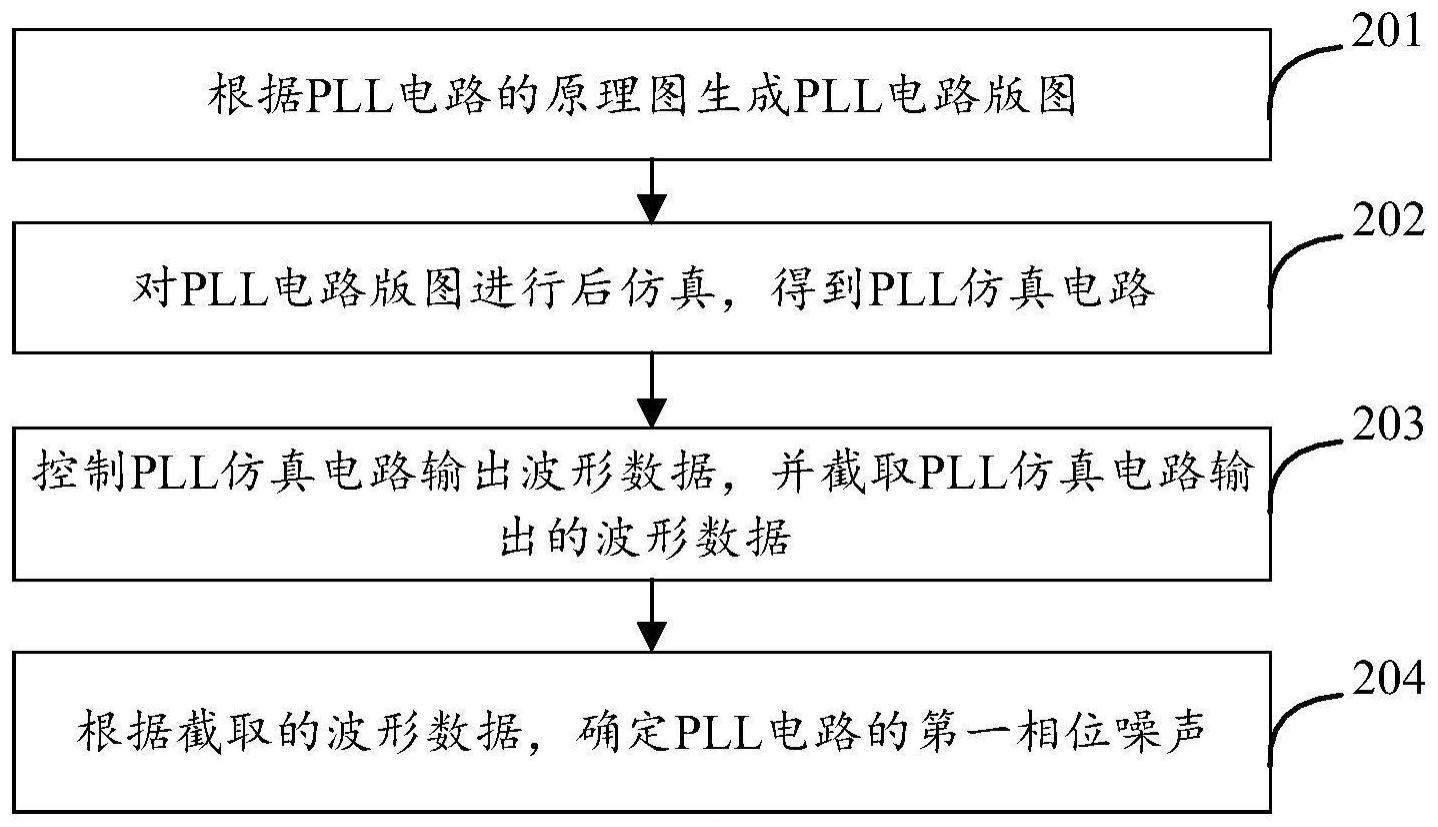

2、第一方面,本发明实施例提供了一种pll电路的相位噪声测量方法,包括:

3、生成pll电路版图;

4、对所述pll电路版图进行后仿真,得到pll仿真电路;

5、控制所述pll仿真电路输出波形数据,并截取所述波形数据;

6、根据截取的所述波形数据,确定pll电路的第一相位噪声。

7、在一些实施例中,所述控制所述pll仿真电路输出波形数据,并截取所述波形数据,包括:

8、检测到所述pll仿真电路输出的波形数据的频率和/或振幅幅度为稳定数值时,截取所述pll仿真电路输出的波形数据。

9、在一些实施例中,所述根据截取的所述波形数据,确定所述pll电路的相位噪声,包括:

10、采用差拍法、鉴频法、直接数字化法或者鉴相法对截取的所述波形数据进行计算,得到所述pll电路的所述第一相位噪声。

11、在一些实施例中,所述pll电路版图包括多个电路模块;所述方法还包括:

12、在所述pll仿真电路中,提取每个所述电路模块的相位噪声;

13、根据各个所述电路模块的相位噪声拟合出所述pll电路的第二相位噪声;

14、将所述第一相位噪声与所述第二相位噪声进行比对,得到第一噪声差值;

15、根据所述第一噪声差值确定所述多个电路模块之间的串扰噪声。

16、在一些实施例中,所述方法还包括:

17、在所述pll电路版图中设置悬空的金属引脚;

18、在悬空的所述金属引脚上施加干扰噪声;

19、控制施加干扰噪声的pll仿真电路输出波形数据,并重新截取波形数据;

20、根据重新截取的波形数据,确定所述pll电路的第三相位噪声;

21、将所述第一相位噪声与所述第三相位噪声进行比对,得到第二噪声差值;

22、根据所述第二噪声差值,确定pll电路中的噪声敏感位置。

23、在一些实施例中,所述在悬空的所述金属引脚行施加干扰噪声,包括:

24、分多次施加干扰噪声,其中,每次分别在不同的金属引脚上施加干扰噪声,每次施加干扰噪声后,均重新计算第三相位噪声,并根据第三相位噪声确定第二噪声差值;

25、所述根据所述第二噪声差值,确定pll电路中的噪声敏感位置,包括:

26、根据历次获取的所述第二噪声差值,确定pll电路中的噪声敏感位置。

27、第二方面,本发明实施例提供了一种pll电路,包括:

28、pll电路版图,用于经过后仿真生成pll仿真电路,所述pll仿真电路用于输出可供截取的波形数据,其中,截取的所述波形数据用于确定pll电路的第一相位噪声。

29、在一些实施例中,截取的所述波形数据的频率和/或幅度为稳定数值。

30、在一些实施例中,所述pll电路版图包括多个电路模块,通过提取每个所述电路模块的相位噪声拟合出pll电路的第二相位噪声,根据所述第一相位噪声和所述第二相位噪声确定所述多个电路模块之间的串扰噪声。

31、在一些实施例中,所述pll电路版图中包含悬空的金属引脚,当在所述金属引脚上施加干扰噪声时,重新截取pll仿真电路的波形数据,重新截取的波形数据用于确定pll电路的第三相位噪声,根据所述第一相位噪声和所述第三相位噪声确定pll电路中的噪声敏感位置。

32、本发明实施例中,根据pll电路版图生成pll仿真电路。通过对pll仿真电路输出的波形数据的逻辑分析,得到pll电路的相位噪声。该方法中,控制pll仿真电路输出波形数据比较容易实现,且根据波形数据计算出的pll相位噪声更加符合真实pll电路的相位噪声。因此,基于本发明实施例方法能够提高pll电路相位噪声测量的稳定性和准确性。

技术特征:

1.一种锁相环pll电路的相位噪声测量方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述控制所述pll仿真电路输出波形数据,并截取所述波形数据,包括:

3.根据权利要求1所述的方法,其特征在于,所述根据截取的所述波形数据,确定所述pll电路的相位噪声,包括:

4.根据权利要求1所述的方法,其特征在于,所述pll电路版图包括多个电路模块;所述方法还包括:

5.根据权利要求1所述的方法,其特征在于,所述方法还包括:

6.根据权利要求5所述的方法,其特征在于,所述在悬空的所述金属引脚行施加干扰噪声,包括:

7.一种pll电路,其特征在于,包括:

8.根据权利要求7所述的电路,其特征在于,截取的所述波形数据的频率和/或幅度为稳定数值。

9.根据权利要求7所述的电路,其特征在于,所述pll电路版图包括多个电路模块,通过提取每个所述电路模块的相位噪声拟合出pll电路的第二相位噪声,根据所述第一相位噪声和所述第二相位噪声确定所述多个电路模块之间的串扰噪声。

10.根据权利要求7所述的电路,其特征在于,所述pll电路版图中包含悬空的金属引脚,当在所述金属引脚上施加干扰噪声时,重新截取pll仿真电路的波形数据,重新截取的波形数据用于确定pll电路的第三相位噪声,根据所述第一相位噪声和所述第三相位噪声确定pll电路中的噪声敏感位置。

技术总结

本申请涉及锁相环(Phase‑Locked Loops,简称PLL)电路技术领域,具体地涉及一种PLL电路及相位噪声测量方法。所述方法包括:生成PLL电路版图;对所述PLL电路版图进行后仿真,得到PLL仿真电路;控制所述PLL仿真电路输出波形数据,并截取所述波形数据;根据截取的所述波形数据,确定PLL电路的第一相位噪声。本发明实施例方案,有助于提高PLL电路相位噪声测量的稳定性和准确性。

技术研发人员:霍显杰

受保护的技术使用者:成都极海科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!