半导体结构及其形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、随着电子消费产品需求的增长,双扩散功率mosfet(dmos)以其高工作电流密度、低导通电阻和良好的开关特性,在高压集成电路(hvic)和功率集成电路(pic)中得到了广泛的应用。

2、功率场效应管主要包括垂直双扩散场效应管vdmos(vertical double-diffusedmosfet)和横向双扩散场效应管ldmos(lateral double-diffused mosfet)两种类型。

3、目前,在技术节点不断缩小的情况下,利用垂直沟道和与晶片厚度相关的vdmos是减小芯片面积的良好方法。

4、然而,vdmos的结构及其性能仍有待提高。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构及其形成方法,以提高半导体结构的性能。

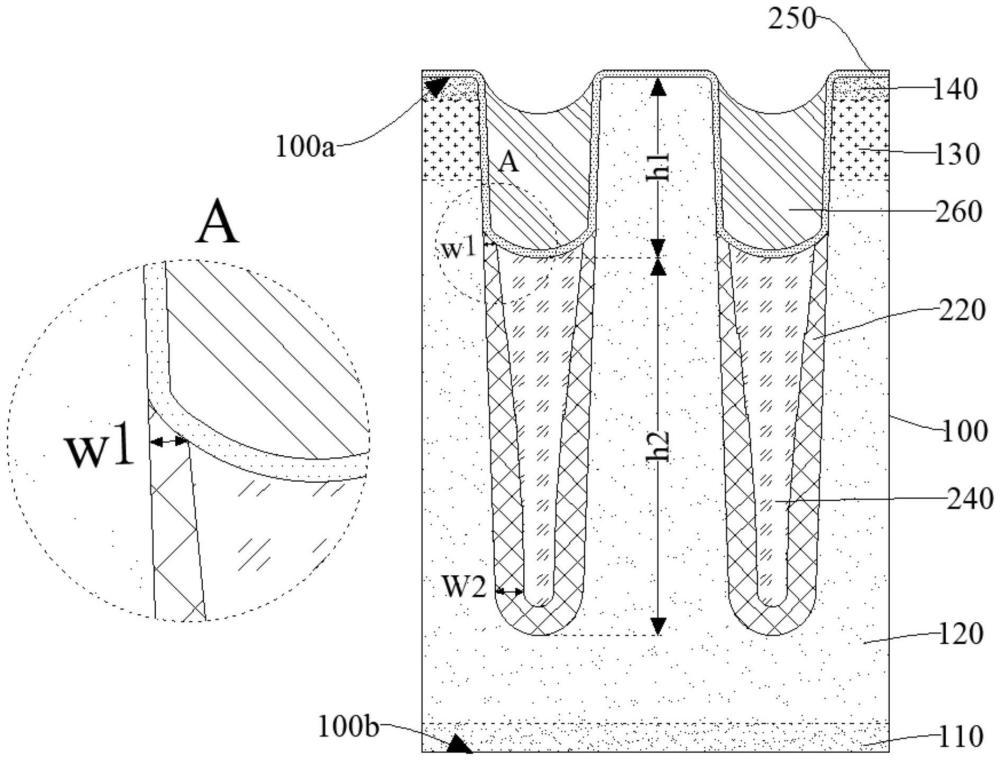

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:衬底;漏极,位于所述衬底中,所述漏极中的离子具有第一导电类型;漂移区,位于所述衬底中且位于所述漏极上方,所述漂移区中的离子具有第一导电类型;控制栅极结构,位于所述衬底中且位于第一部分厚度的漂移区中;分离栅极结构,位于所述控制栅极结构底部的第二部分厚度的漂移区中;介电层,位于所述分离栅极结构和漂移区之间,且所述介电层顶部的宽度,小于所述介电层底部的宽度;源极,位于所述控制栅极结构侧部的漂移区中,且位于靠近所述衬底顶部位置处,所述源极中的离子具有第一导电类型。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底中形成有漏极,所述漏极中的离子具有第一导电类型;在所述衬底中形成位于所述漏极上方的漂移区,所述漂移区中的离子具有第一导电类型;在所述衬底中形成凹槽,所述凹槽包括相互贯通的第一凹槽和第二凹槽,所述第一凹槽位于第一部分厚度的漂移区中,所述第二凹槽位于第一凹槽底部的第二部分厚度的漂移区中;在所述第二凹槽的内壁上形成介电层,所述介电层顶部的宽度,小于所述介电层底部的宽度;在所述第二凹槽的剩余空间中形成覆盖所述介电层的分离栅极结构;在所述第一凹槽中形成控制栅极结构;在所述控制栅极结构侧部的漂移区中形成靠近所述衬底顶部位置处的源极,所述源极中的离子具有第一导电类型。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供的半导体结构中,包括位于所述衬底中且位于所述漏极上方的漂移区,位于所述分离栅极结构和漂移区之间的介电层,且所述介电层顶部的宽度,小于所述介电层底部的宽度,以及位于所述控制栅极结构底部的第二部分厚度的漂移区中的分离栅极结构。所述分离栅极结构、所述介电层和所述漂移区构成电容,所述分离栅极结构作为电容的场板。由于所述漂移区的电荷量(qd),与所述分离栅极结构与漂移区所构成的电容的电量(csgo),以及与介电层与漂移区交界面上的电势(vsurf)成正比,即qd=csgo×vsurf;而且,所述分离栅极结构与漂移区所构成的电容的电量(csgo)与介电层的厚度成反比,即csgo=εoxa/tox,其中ε是指介电层的介电常数,a是指所述分离栅极结构与漂移区的正对面积,tox是指所述分离栅极结构与漂移区之间的距离(也即所述介电层的宽度)。当对所述漏极施加电压时,虽然所述介电层与漂移区交界面上的电势从所述分离栅极结构底部位置处至所述分离栅极结构顶部位置处逐渐减小,但是所述介电层顶部的宽度,小于所述介电层底部的宽度,使得靠近所述分离栅极结构底部位置处的电容,小于靠近分离栅极结构顶部位置处的电容,相应减小了靠近所述分离栅极结构底部位置处的电荷量,与靠近所述分离栅极结构顶部位置处的电荷量差异,提高了所述漂移区中的电荷量分布的均一性,相应提高了所述漂移区中的电场强度的均一性,从而提高了介电层的击穿电压(bv),进而提高了半导体结构的击穿电压。

6、本发明实施例提供的半导体结构的形成方法中,在所述衬底中形成位于所述漏极上方的漂移区,在所述衬底中形成相互贯通的第一凹槽和第二凹槽,在所述第二凹槽的内壁上形成介电层,所述介电层顶部的宽度,小于所述介电层底部的宽度,在所述第二凹槽的剩余空间中形成覆盖所述介电层的分离栅极结构,所述分离栅极结构、所述介电层和所述漂移区构成电容,所述分离栅极结构作为电容的场板;由于所述漂移区的电荷量(qd),与所述分离栅极结构与漂移区所构成的电容的电量(csgo),以及与介电层与漂移区交界面上的电势(vsurf)成正比,即qd=csgo×vsurf;而且,所述分离栅极结构与漂移区所构成的电容的电量(csgo)与介电层的厚度成反比,即csgo=εoxa/tox,其中ε是指介电层的介电常数,a是指所述分离栅极结构与漂移区的正对面积,tox是指所述分离栅极结构与漂移区之间的距离(也即所述介电层的宽度)。当对所述漏极施加电压时,虽然所述介电层与漂移区交界面上的电势从所述分离栅极结构底部位置处至所述分离栅极结构顶部位置处逐渐减小,但是所述介电层顶部的宽度,小于所述介电层底部的宽度,使得分离栅极结构底部位置处的电容,小于靠近所述分离栅极结构顶部位置处的电容,相应减小了分离栅极结构底部位置处的电荷量,与靠近分离栅极结构顶部位置处的电荷量差异,提高了所述漂移区中的电荷量分布的均一性,相应提高了所述漂移区中的电场强度的均一性,从而提高了介电层的击穿电压,进而提高了半导体结构的击穿电压。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述介电层的宽度,从顶部至底部逐渐减小。

3.如权利要求2所述的半导体结构,其特征在于,所述介电层与分离栅极结构的交界面呈阶梯状,且所述阶梯的数量为多个。

4.如权利要求3所述的半导体结构,其特征在于,所述阶梯的数量至少为5个。

5.如权利要求1所述的半导体结构,其特征在于,所述介电层顶部的宽度,与所述介电层底部的宽度的差值范围为500埃米至2000埃米。

6.如权利要求1所述的半导体结构,其特征在于,沿与所述分离栅极结构侧壁相垂直的方向,所述介电层的宽度范围为150埃米至2000埃米。

7.如权利要求1所述的半导体结构,其特征在于,所述介电层的材料包括氧化硅和氮化硅中的一种或两种。

8.如权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括:栅介质层,位于所述控制栅极结构和分离栅极结构之间,以及所述控制栅极结构的侧壁上。

9.如权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括:体区,位于所述源极底部的漂移区中,所述体区中的离子具有第二导电类型,所述第一导电类型和第二导电类型不同。

10.一种半导体结构的形成方法,其特征在于,包括:

11.如权利要求10所述的半导体结构的形成方法,其特征在于,在所述第二凹槽的内壁上形成介电层的步骤中,所述介电层的宽度,从顶部至底部逐渐减小。

12.如权利要求11所述的半导体结构的形成方法,其特征在于,在所述第二凹槽的内壁上形成介电层的步骤包括:

13.如权利要求12所述的半导体结构的形成方法,其特征在于,去除部分高度的所述牺牲层的工艺包括各向异性的刻蚀工艺。

14.如权利要求12所述的半导体结构的形成方法,其特征在于,去除部分宽度的所述初始介电层的工艺包括各向同性的刻蚀工艺。

15.如权利要求14所述的半导体结构的形成方法,其特征在于,所述各向同性的刻蚀工艺包括各向异性的湿法刻蚀工艺,所述湿法刻蚀工艺的刻蚀溶液包括盐酸溶液。

16.如权利要求12所述的半导体结构的形成方法,其特征在于,所述初始介电层减薄处理的次数大于或等于5次。

17.如权利要求12所述的半导体结构的形成方法,其特征在于,在所述第二凹槽的内壁上形成初始介电层的步骤包括:

18.如权利要求12或17所述的半导体结构的形成方法,其特征在于,在所述第二凹槽的剩余空间中填充牺牲层的步骤包括:

19.如权利要求10所述的半导体结构的形成方法,其特征在于,在所述形成分离栅极结构之后,在形成所述控制栅极结构之前,所述形成方法还包括:在所述第一凹槽的内壁上形成栅介质层;

技术总结

一种半导体结构及其形成方法,半导体结构包括衬底;漏极,位于衬底中,漏极中的离子具有第一导电类型;漂移区,位于衬底中且位于漏极上方,漂移区中的离子具有第一导电类型;控制栅极结构,位于衬底中且位于第一部分厚度的漂移区中;分离栅极结构,位于控制栅极结构底部的第二部分厚度的漂移区中;介电层,位于分离栅极结构和漂移区之间,且介电层顶部的宽度,小于介电层底部的宽度;源极,位于控制栅极结构侧部的漂移区中,且位于靠近衬底顶部位置处,源极中的离子具有第一导电类型。本发明实施例减小了分离栅极结构底部位置处的电荷量与分离栅极结构顶部位置处的电荷量差异,提高了漂移区中的电场强度的均一性,从而提高了介电层的击穿电压。

技术研发人员:张小燕,杨林宏,李智,林新元,陈亮

受保护的技术使用者:中芯国际集成电路制造(天津)有限公司

技术研发日:

技术公布日:2025/3/27

- 还没有人留言评论。精彩留言会获得点赞!