一种可动态调整计算速度的FIR滤波器的制作方法

本发明涉及fir滤波器,更具体地说,它涉及一种可动态调整计算速度的fir滤波器。

背景技术:

1、fir滤波器即有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,fir滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

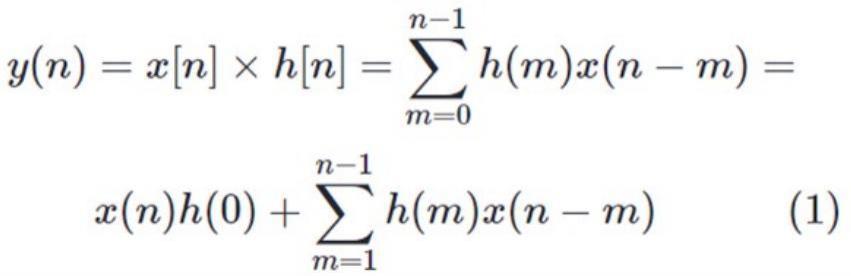

2、相关技术中,对比文件1(基于alterafpga的部分串行 fir 滤波器,郭雨梅等,沈阳工业大学学报,2009年05期,第577-581页)公开了一种部分串行结构 fir 滤波器,并具体公开了以下的技术特征(参见对比文件 1 的以下内容):对于n 阶fir滤波器,在n时刻的差分方程可以表示为:

3、

4、由上述方程可知,其第2项可以在 x(n)未输入时通过对延迟链中已有的数据移位并与对应的 h(n)做乘累加得到,其主要是从fpga的角度考虑将延迟链中的数据进行位移相乘累加的,而这种方式,不仅计算速度缓慢,还会造成极大的资源开销,而且,其计算方式固定,并不具备动态可调整功能,不利于处理越来越多样化且复杂的数据信号类型。因此需要提供一种计算时间短、数据处理速度快、消耗资源小的具备可动态调整功能的fir滤波器。

技术实现思路

1、针对现有技术存在的不足,本发明的目的在于提供一种可动态调整计算速度的fir滤波器。

2、为实现上述目的,本发明提供了如下技术方案,包括:

3、控制器,用于产生读写控制信号和运算控制信号;

4、数据存储模块,用于存储输入的数据样本和运算中间结果的数据;

5、总线模块,用于对输入和输出的信号进行模数转换;

6、fir运算模块,用于读出数据样本并进行fir滤波运算,所述fir运算模块包括乘法器运算单元、累加器运算单元、副乘法器运算单元和副累加器运算单元;

7、其中,所述乘法器运算单元用于将从所述数据存储模块中读取的数据进行数据相乘处理;所述累加器运算单元用于对运算的中间结果进行累加或累减处理;所述副乘法器运算单元和所述副累加器运算单元用于在计算前数据y[n]的同时,提前对未来m个y值进行运算。

8、优选地,所述副累加器运算单元和所述副乘法器运算单元在进行运算时的具体过程为:根据求卷积在硬件中实现的特性,求y[n]需要用到的x的范围为(x[n-n],x[n]),其中(x[n-n+1],x[n])会在下次求y[n+1]时被用到,以此类推,(x[n-n+2],x[n])会在求y[n+2]时被使用,因此,当使用乘法器运算单元进行x[n]与h[0]进行乘法运算时,通过副累加器运算单元提前将x[n]与h[1]运算好并进入所述累加器运算单元中等待与下一拍数x[n-1]h[2]进行累加,在计算完成y[n]后,只需要在下一节拍中利用所述副累加器运算单元累加上x[n+1]h[0],即可完成对y[n+1]的计算。

9、优选地,所述副乘法器运算单元和所述副累加器运算单元的数量是通过所述数据存储模块进行动态选择配置。

10、优选地,所述数据存储模块为存储器,所述存储器包括数据样本和运算中间结果两个不同的存储区域。

11、优选地,所述总线模块包括信号输入单元、信号输出单元,所述信号输入单元设置为a/d信号转换器件,所述信号输出单元设置为d/a信号转换器件。

12、与现有技术相比,本发明具备以下有益效果:

13、本发明通过设置fir运算模块,主要是利用复用芯片内部的乘法器以及累加器资源,并在面积不变的前提下,通过设置副累加器运算单元和副乘法器运算单元,并利用数据存储模块动态调整副乘法器运算单元以及副累加器运算单元的数量,能够有效的缩短节拍数量,从而实现缩短计算时间,加快数据的处理速度的目的。

技术特征:

1.一种可动态调整计算速度的fir滤波器,其特征在于,包括:

2.根据权利要求1所述的可动态调整计算速度的fir滤波器,其特征在于,所述数据存储模块为存储器,所述存储器包括数据样本和运算中间结果两个不同的存储区域。

3.根据权利要求1所述的可动态调整计算速度的fir滤波器,其特征在于,所述总线模块包括信号输入单元、信号输出单元,所述信号输入单元设置为a/d信号转换器件,所述信号输出单元设置为d/a信号转换器件。

技术总结

本发明公开了一种可动态调整计算速度的FIR滤波器,涉及FIR滤波器领域,其技术方案要点包括:控制器,用于产生读写控制信号和运算控制信号;数据存储模块,用于存储输入的数据样本和运算中间结果的数据。一种可动态调整计算速度的FIR滤波器,本发明通过设置FIR运算模块,主要是利用复用芯片内部的乘法器以及累加器资源,并在面积不变的前提下,通过设置副累加器运算单元和副乘法器运算单元,并利用数据存储模块动态调整副乘法器运算单元以及副累加器运算单元的数量,能够有效的缩短节拍数量,从而实现缩短计算时间,加快数据的处理速度的目的。

技术研发人员:钟晨峰,吴树伟,庄志青,胡红明,张希鹏,周玉镇

受保护的技术使用者:灿芯半导体(苏州)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!