3D芯片封装结构的制作方法

本申请涉及一种半导体封装结构,尤其涉及一种3d芯片封装结构。

背景技术:

1、随着资料量的需求越来越高,常见的存储器已无法满足高资料量传输的要求,因此一种具有体积更小、消耗功率更低以及更高频宽的高频宽存储器被提出。

2、为了实现高频宽存储器的高频宽,高频宽存储器须具备更多的信道来执行资料交换,而目前高频宽存储器可支援到4gb的信道。因此,相对的,用以控制每一信道的控制器数量也相应增加。

3、一般来说,控制器是对应高频宽存储器中的信道连接点位置而布满整个逻辑电路区,控制器并通过导电体与信道连接点电性连接,因此,高频宽存储器与逻辑电路区之间将布满所述导电体。然而,此配置方式将导致逻辑电路区的芯片电路设计困难。举例来说,为了维持控制器与高频宽存储器之间的配置,逻辑电路区的芯片电路需要闪避导电体及控制器的位置进行设计。而硅智财(silicon intellectual property,ip)芯片为已订定内部设计的芯片类型,在其设计更改不易的情况,将难以直接应用于逻辑电路区的芯片电路设计,造成积体电路芯片设计不便。

技术实现思路

1、为了解决上述技术问题,本申请提出一种3d芯片封装结构,适用于现有硅智财组件,有效简化电路设计难度,并降低积体电路(integrated circuit,ic)芯片整体设计成本,达到提升积体电路芯片设计便利性的目的。

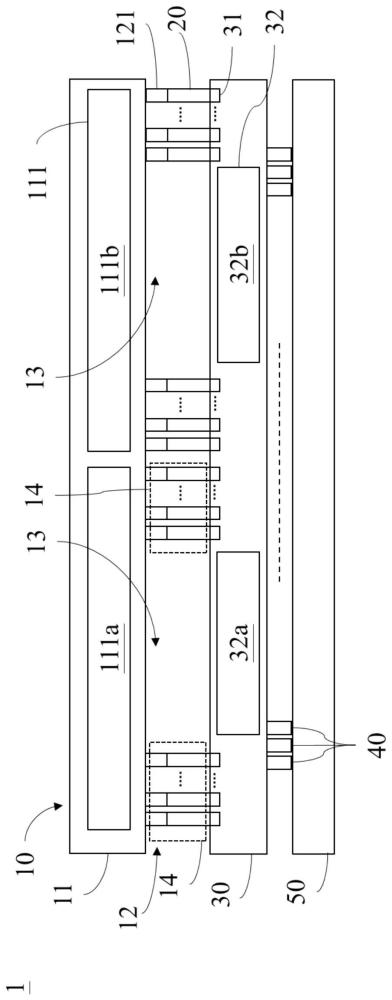

2、为了达成上述的目的,本申请提出一种3d芯片封装结构,其包括存储器装置。所述存储器装置包括存储器晶体层以及连接层。所述存储器晶体层包括至少一存储器分区。所述连接层位于所述存储器晶体层的一侧,且配置有至少一连接垫。其中,对应于所述至少一存储器分区的连接层定义有至少一连接净空区以及至少一连接区,所述至少一连接净空区与所述至少一连接区相邻,所述至少一连接净空区的面积等于或大于所述至少一连接区。所述至少一连接垫仅配置于所述至少一连接区。

3、基于上述内容,本申请提供的3d芯片封装结构通过将连接垫配置于预定义的连接区,并形成不配置导电柱体的连接净空区,使电路组件可在不更动其内部设计的前提下对应连接净空区配置而直接应用于3d芯片封装结构中,简化电路设计难度,并以现有电路组件降低积体电路芯片整体设计成本,达到提升积体电路芯片设计便利性的目的。

技术特征:

1.一种3d芯片封装结构,其特征在于,包括:

2.如权利要求1所述的3d芯片封装结构,其特征在于,更包括至少一导电柱体,所述至少一导电柱体与所述至少一连接垫连接并相应于所述至少一连接区配置。

3.如权利要求1所述的3d芯片封装结构,其特征在于,所述至少一连接区邻近所述至少一存储器分区的侧边。

4.如权利要求1所述的3d芯片封装结构,其特征在于,对应于所述至少一存储器分区的所述连接层定义有复数连接区,且两个连接区之间配置有一个连接净空区。

5.如权利要求1所述的3d芯片封装结构,其特征在于,所述连接层定义有复数个连接净空区,每一所述连接净空区的面积彼此为相同或不相同。

6.如权利要求4所述的3d芯片封装结构,其特征在于,每一所述连接区的面积彼此为相同或不相同。

7.如权利要求2所述的3d芯片封装结构,其特征在于,包括:

8.如权利要求7所述的3d芯片封装结构,其特征在于,所述逻辑电路层更包括至少一存储器控制器,所述至少一存储器控制器与所述至少一导电柱体电性连接。

9.如权利要求1所述的3d芯片封装结构,其特征在于,所述存储器装置包括至少一重布层,所述至少一重布层配置于所述存储器晶体层以及所述连接层之间。

10.如权利要求9所述的3d芯片封装结构,其特征在于,所述至少一重布层的厚度为0.7至0.9微米。

技术总结

本申请公开了一种3D芯片封装结构,其包括存储器装置。存储器装置包括存储器晶体层以及连接层。存储器晶体层包括至少一存储器分区。连接层配置于存储器晶体层的一侧,且配置有至少一连接垫。其中,对应于至少一存储器分区的连接层定义有至少一连接净空区以及至少一连接区,至少一连接净空区与至少一连接区相邻,至少一连接净空区的面积等于或大于至少一连接区,至少一连接垫仅配置于至少一连接区。

技术研发人员:李昆宪,李致贤

受保护的技术使用者:鲸链科技股份有限公司

技术研发日:

技术公布日:2025/3/27

- 还没有人留言评论。精彩留言会获得点赞!