具有解调制耦合的双数字锁相环的制作方法

背景技术:

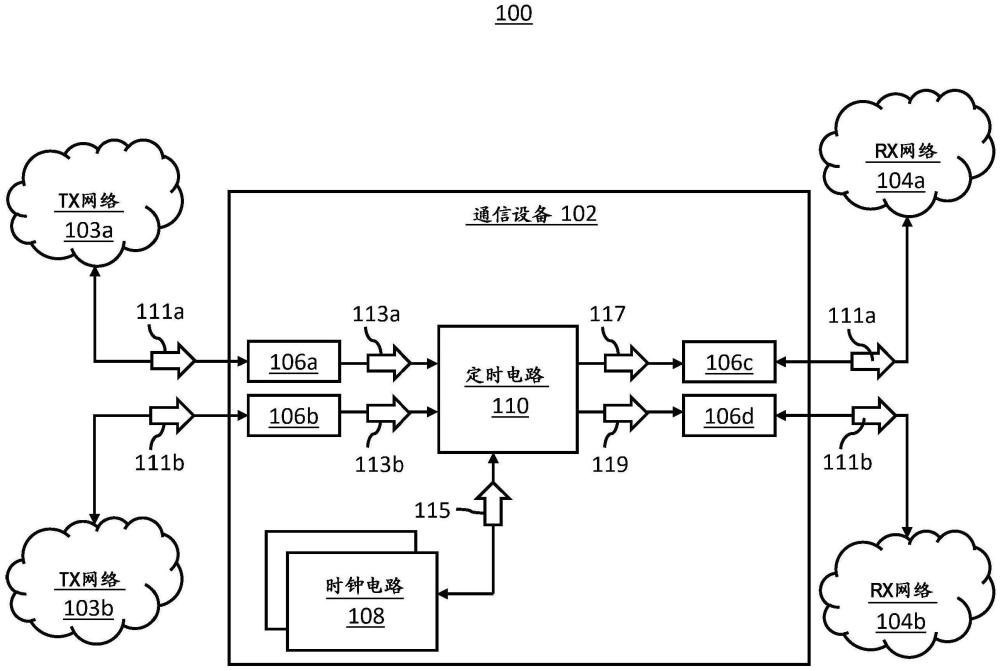

1、本公开总体上涉及半导体器件,并且更具体地涉及可以实现双数字锁相环的解调制耦合的定时电路。

2、包括收发器和时钟电路的定时电路可以连接到多个网络以同步多个网络。定时电路可以包括多个锁相环,诸如模拟锁相环(apll)和数字锁相环(dpll)。apll可以包括模拟相位检测器、电荷泵、环路滤波器、和反馈环路中的压控振荡器(vco)。dpll可以包括数字相位检测器和环路滤波器、以及数字控制振荡器(dco)。由于包括数字相位检测器和环路滤波器,因此数字锁相环通常比模拟pll小。apll和dpll的组合可以形成混合信号锁相环,该混合信号锁相环可以减少由定时电路输出的信号中的抖动。

技术实现思路

1、在一个实施例中,总体上描述了一种用于同步网络的半导体器件。半导体器件可以包括被配置为输出第一信号的模拟锁相环(apll)。半导体器件还可以包括被配置为输出第二信号的第一数字锁相环(dpll)。半导体器件还可以包括被配置为输出第三信号的第二dpll。第一信号和第二信号的组合可以用于生成第一输出时钟信号。从第三信号中减去第二信号得到的差可以用于生成第二输出时钟信号。

2、在一个实施例中,总体上描述了一种用于同步网络的装置。该装置可以包括多个收发器和定时电路。定时电路可以被配置为从多个收发器中的第一收发器接收第一参考信号。定时电路还可以被配置为从多个收发器中的第二收发器接收第二参考信号。定时电路还可以被配置为向多个收发器中的第二收发器输出第一输出时钟信号。定时电路还可以被配置为向多个时钟电路中的第二时钟电路输出第二输出时钟信号。第一输出时钟信号可以基于由定时电路中的模拟锁相环(apll)生成的第一信号和由定时电路中的数字锁相环(dpll)生成的第二信号的组合。第二输出时钟信号可以基于从由定时电路的第二dpll生成的第三信号中减去第二信号而得到的差。

3、在一个实施例中,一种用于操作定时电路以同步多个网络的方法。该方法可以包括操作模拟锁相环(apll)以输出第一信号。该方法还可以包括操作第一数字锁相环(dpll)以输出第二信号。该方法还可以包括操作第二dpll以输出第三信号。该方法还可以包括组合第一信号和第二信号以生成第一输出时钟信号。该方法还可以包括从第三信号中减去第二信号以生成第二输出时钟信号。第二输出时钟信号可以独立于第一dpll的操作。

4、上述概述仅为说明性内容,而非旨在以任何方式进行限制。除了上述说明性方面、实施例和特征之外,通过参考附图和以下详细描述,其他的方面、实施例和特征将变得很清楚。在附图中,相似的附图标记表示相同或功能相似的元素。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,还包括:

3.根据权利要求1所述的半导体器件,还包括多个分数输出分频器,其中所述多个分数输出分频器中的每个分数输出分频器被配置为输出所述第二输出时钟信号的副本。

4.根据权利要求1所述的半导体器件,还包括低通滤波器,所述低通滤波器被配置为在从所述第三信号中减去所述第二信号之前对所述第二信号进行过滤,其中所述低通滤波器的带宽基于所述apll的带宽。

5.根据权利要求1所述的半导体器件,还包括缩放器,所述缩放器被配置为在所述第二输出时钟信号的生成之前缩放所述差。

6.根据权利要求1所述的半导体器件,还包括频率输出分频器,其中频率输出分频器包括:

7.根据权利要求1所述的半导体器件,其中所述第一dpll的带宽与所述第二dpll的带宽之间的差小于预定义阈值。

8.根据权利要求1所述的半导体器件,其中所述第二输出时钟信号独立于所述第一dpll的操作。

9.一种装置,包括:

10.根据权利要求9所述的装置,其中所述定时电路包括:

11.根据权利要求9所述的装置,其中所述定时电路包括多个分数输出分频器,并且所述多个分数输出分频器中的每个分数输出分频器被配置为输出所述第二输出时钟信号的副本。

12.根据权利要求9所述的装置,其中所述定时电路包括低通滤波器,所述低通滤波器被配置为在从所述第三信号中减去所述第二信号之前对所述第二信号进行过滤,其中所述低通滤波器的带宽基于所述apll的带宽。

13.根据权利要求9所述的装置,其中所述定时电路包括缩放器,所述缩放器被配置为在所述第二输出时钟信号的生成之前缩放所述差。

14.根据权利要求9所述的装置,其中所述定时电路包括频率输出分频器,其中频率输出分频器包括:

15.根据权利要求9所述的装置,其中所述第一dpll的带宽与所述第二dpll的带宽之间的差小于预定义阈值。

16.根据权利要求9所述的装置,其中所述第二输出时钟信号独立于所述第一参考信号。

17.一种用于操作定时电路以同步多个网络的方法,所述方法包括:

18.根据权利要求17所述的方法,还包括:

19.根据权利要求17所述的方法,还包括操作低通滤波器以在从所述第三信号中减去所述第二信号之前对所述第二信号进行过滤,其中所述低通滤波器的带宽基于所述apll的带宽。

20.根据权利要求17所述的方法,其中所述第一dpll的带宽与所述第二dpll的带宽之间的差小于预定义阈值。

技术总结

本公开涉及一种具有解调制耦合的双数字锁相环。描述了一种用于同步网络的半导体器件。半导体器件可以包括被配置为输出第一信号的模拟锁相环APLL。半导体器件还可以包括被配置为输出第二信号的第一数字锁相环DPLL。半导体器件还可以包括被配置为输出第三信号的第二DPLL。第一信号和第二信号的组合可以用于生成第一输出时钟信号。从第三信号中减去第二信号得到的差可以用于生成第二输出时钟信号。

技术研发人员:M·T·斯皮克

受保护的技术使用者:瑞萨电子美国有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!