非易失铁电半导体存储器及制备方法

本发明涉及存储器,更为具体地,涉及一种非易失铁电半导体存储器及制备方法。

背景技术:

1、非易失性(nonvolatile)存储器件具有掉电后数据不丢失的特点,在当代信息社会中随处可见。随着半导体工业的发展与专用化硬件、物联网等嵌入式应用的普及,工业对非易失性存储器功耗、速度、存储密度、可靠性、耐擦写能力等性能也提出了更高的要求。

2、目前,铁电场效应晶体管(fefet)用铁电薄膜替代mosfet结构中的栅氧化物,以利用铁电薄膜的极化调节沟道导通、关断状态;通过在栅极施加不同极性的电压,可控制铁电层剩余极化在两种方向间切换,达到存储“0”与“1”的目的,具有擦写速度快、工作电压低、存储密度高、非破坏性读出和反复擦写能力强等优点。然而,传统结构的fefet仍存在一些问题。

3、首先,传统1t结构的fefet存储器由于存在写串扰,导致存在存储密度与可靠性问题。传统存储阵列编程操作需栅极(字线)、漏极(位线)同时施加电压,因此在交叉阵列结构中可单独选中并编程特定字线、位线交叉处的存储单元。相比之下,1t结构的fefet由于编程操作仅受栅极相对沟道的电压控制,自身无法实现交叉选中,构建交叉阵列结构时需要额外的选通器件,导致集成密度降低。

4、其次,潜在的泄漏电流使存储器数据可靠性降低、功耗增大。由于fefet阈值电压波动性较强且铁电层极化方向向下时器件阈值电压较低;阈值电压偏移可能导致极化方向向下的fefet阈值电压低于0v,在未被选中时保持开启状态,显著增大泄漏电流,造成可靠性变差、功耗增加。为减轻泄漏电流影响,fefet存储器设计中常采用较高的阈值电压。然而,较高阈值电压使得读取数据时栅极电压同样较高,这会在铁电层中引起较强电场,干扰铁电层极化状态;即读取数据时相应存储单元将被弱编程。因此,采用较高阈值电压也无法有效提升存储器可靠性。

技术实现思路

1、鉴于上述问题,本发明提供一种非易失铁电半导体存储器及制备方法,以解决现有fefet存储器件所存在的存储密度受限、可靠性低及功耗大等问题。

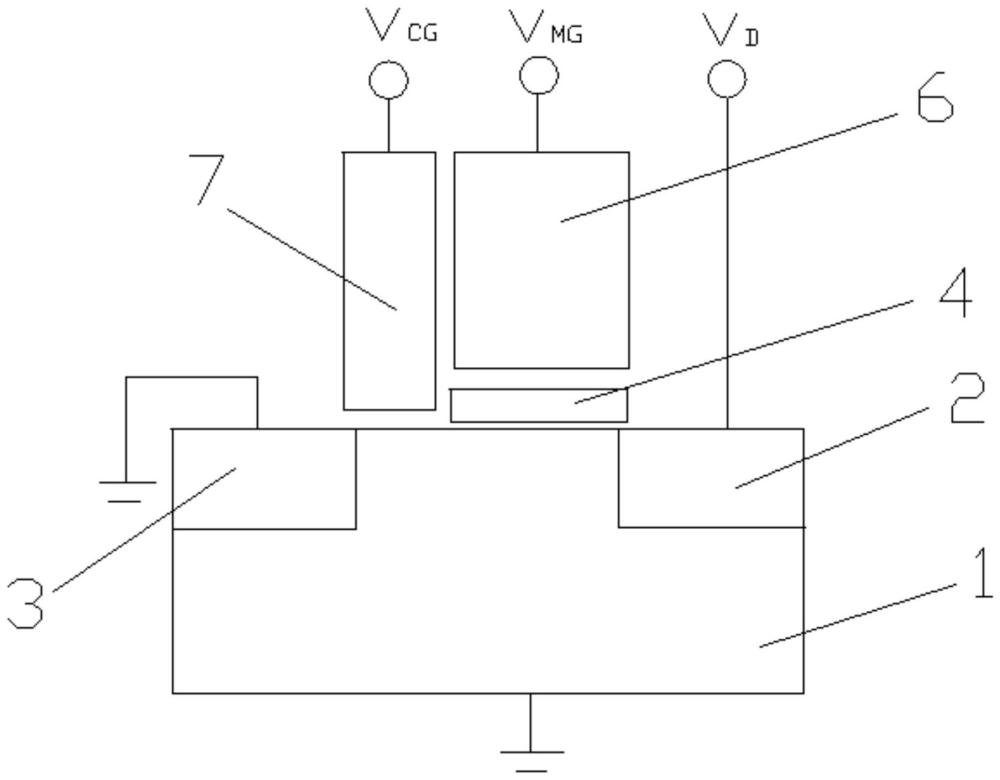

2、本发明提供的非易失铁电半导体存储器,包括衬底、依次设置在衬底上方的控制栅和存储栅;其中,在衬底上设置有源极和漏极,位于源极和漏极之间的衬底区域形成隔离源极和漏极的沟道;在沟道和存储栅之间设置有铁电层,存储栅用于向铁电层的上表面施加电压,以改变铁电层的极化状态;控制栅用于控制沟道导通或关闭;通过控制存储栅、源极、控制栅以及漏极的电压,实现数据的写入、读取以及擦除。

3、此外,可选的技术方案是,衬底为第一掺杂类型,源极和漏极为与第一掺杂类型相反的第二掺杂类型。

4、此外,可选的技术方案是,沟道包括控制栅下沟道和存储栅下沟道;衬底的材料包括硅、锗、氮化镓、砷化镓、砷化铟、磷化铟、碳化硅、锑化铟、铟镓锌氧、铟铝锌氧、铟锡锌氧、铟锡氧中的至少一种;沟道在衬底上的形成方式包括:浅槽隔离或场氧化物隔离。

5、此外,可选的技术方案是,铁电层覆盖沟道的部分区域,铁电层的材料包括氧化铪、氧化锆、铪锆氧、铪铝氧、铪镧氧、钛酸铅、pzt、sbt、blt,由上述任意一种材料的单层或多种材料组合的多层构成,并且,铁电层在衬底上的形成方式包括:原子层淀积、物理汽相淀积、低压化学气相淀积、等离子体化学淀积。

6、此外,可选的技术方案是,在铁电层的上下表面分别设置有缓冲介质;缓冲介质包括至少一层二氧化硅或碳化硅或氧化铝或氧化铪或hfalo或hfsio或ta2o5或tasio的介质层。

7、此外,可选的技术方案是,存储栅的横截面与铁电层相一致,控制栅覆盖沟道除铁电层外的区域部分;存储栅的材料包括:掺杂的多晶硅、钽、钕、氮化钛、氮化钨、氮化钽、金属硅化物;存储栅与所控制栅之间设置有绝缘介质。

8、此外,可选的技术方案是,在实现数据的写入时,向待写入的存储单元的存储栅与漏极施加大于极化翻转阈值的正电压,向控制栅施加大于阈值电压的正电压;存储单元的沟道完全开启,漏极的正电压降落在沟道的漏端,除去与漏极相交接的位置,沟道的表面电势为源极电压0v;铁电层的上表面的电压为存储栅的正电压,下表面的电压为沟道表面的电势0v,存储栅的正电压降落在铁电层中,铁电层中存在方向向下的电场,极化状态改变;待电压撤去后,铁电层具有方向向下的剩余极化,存储单元被写入“1”。

9、此外,可选的技术方案是,在实现数据的擦除时,向待擦除存储单元的存储栅施加幅度大于极化翻转阈值的负电压;此时,铁电层的上表面电势为存储栅施加的负电压,下表面的电压为衬底电压0v,铁电层中存在方向向上的电场;待电压撤去后,铁电层保留方向向上的剩余极化,单元被擦除为“0”。

10、此外,可选的技术方案是,在实现数据的读取时,向控制栅施加大于阈值电压的电压,存储栅施加读电压,读电压介于铁电层的两种极化状态所对应的阈值电压之间;若铁电层的极化方向向下,存储栅的电压大于阈值电压,沟道导通,读出“1”;否则沟道关断,读出“0”。

11、另一方面,本发明还提供一种非易失铁电半导体存储器制备方法,包括:通过热氧化或化学气相沉积的方式,在衬底上形成栅介质及铁电层下的缓冲介质;在缓冲介质上形成铁电层以及位于铁电层上的存储栅,并通过反应离子刻蚀或湿法刻蚀图形化;在栅介质上沉积绝缘层材料,并通过干法刻蚀或反应离子刻蚀至栅介质暴露,形成绝缘层;在绝缘层上沉积控制栅材料,并通过干法刻蚀或反应离子刻蚀图形化至衬底暴露,形成控制栅;通过轻掺杂注入或斜向注入在衬底上形成源漏外延,在源漏外延上沉积侧墙隔离材料,并刻蚀至衬底暴露,形成控制栅的侧墙;通过离子注入或扩散在衬底上形成重掺杂源极和漏极区域。

12、利用上述非易失铁电半导体存储器及制备方法,设置控制栅和存储栅,并在存储栅和衬底之间设置铁电层,通过控制栅与存储栅的电压改变铁电层的极化状态,能够实现nor型阵列结构交叉选中,消除写串扰,消除泄漏电流,降低阈值电压、操作电压与读电压,提高存储密度,增强存储器的可靠性及耐擦写能力,提高数据保持时间,增大存储窗口及擦写速度,减小泄漏电流及功耗,提高存储器的整体性能及可靠性。

13、为了实现上述以及相关目的,本发明的一个或多个方面包括后面将详细说明的特征。下面的说明以及附图详细说明了本发明的某些示例性方面。然而,这些方面指示的仅仅是可使用本发明的原理的各种方式中的一些方式。此外,本发明旨在包括所有这些方面以及它们的等同物。

技术特征:

1.一种非易失半导体存储器,其特征在于,包括衬底、依次设置在所述衬底上方的控制栅和存储栅;其中,

2.根据权利要求1所述的非易失铁电半导体存储器,其特征在于,

3.根据权利要求1所述的非易失铁电半导体存储器,其特征在于,

4.根据权利要求1所述的非易失铁电半导体存储器,其特征在于,

5.根据权利要求1或4所述的非易失铁电半导体存储器,其特征在于,

6.根据权利要求1所述的非易失铁电半导体存储器,其特征在于,

7.根据权利要求1所述的非易失铁电半导体存储器,其特征在于,在实现数据的写入时,向待写入的存储单元的存储栅与漏极施加大于极化翻转阈值的正电压,向所述控制栅施加大于阈值电压的正电压;

8.根据权利要求1所述的非易失铁电半导体存储器,其特征在于,在实现数据的擦除时,向待擦除存储单元的存储栅施加幅度大于极化翻转阈值的负电压;此时,所述铁电层的上表面电势为所述存储栅施加的负电压,下表面的电压为所述衬底电压0v,所述铁电层中存在方向向上的电场;

9.根据权利要求1所述的非易失铁电半导体存储器,其特征在于,在实现数据的读取时,向所述控制栅施加大于阈值电压的电压,所述存储栅施加读电压,所述读电压介于所述铁电层的两种极化状态所对应的阈值电压之间;

10.一种非易失铁电半导体存储器制备方法,其特征在于,所述方法包括:

技术总结

本发明提供一种非易失铁电半导体存储器非易失铁电半导体存储器及制备方法,其中的存储器包括衬底、依次设置在衬底上方的控制栅和存储栅;其中,在衬底上设置有源极和漏极,位于源极和漏极之间的衬底区域形成隔离源极和漏极的沟道;在沟道和存储栅之间设置有铁电层,存储栅用于向铁电层的上表面施加电压,以改变铁电层的极化状态;控制栅用于控制沟道导通或关闭;通过控制存储栅、源极、控制栅以及漏极的电压,实现数据的写入、读取以及擦除。利用上述发明能够提高存储密度,降低功耗,增强可靠性。

技术研发人员:王宗巍,王浩然,蔡一茂,黄如

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!