射频超宽带CMOS低噪声放大器的制造方法与流程

本发明涉及低噪声放大器的领域,尤其是涉及射频超宽带cmos低噪声放大器的制造方法。

背景技术:

1、超宽带低噪声放大器是超宽带接收机的重要组成部分。对于超宽带低噪声放大器来说,一般带宽都比较宽,且大多工作在高频区域,这样就会致使电路寄生电容作用增强,使增益降低,噪声增高。因此,当我们设计超宽带低噪声放大器电路时也需要将寄生电容的影响考虑进去,为了解决超宽带低噪声放大器设计中的这些问题。

2、发明人体从一种射频超宽带cmos低噪声放大器的制造方法。

技术实现思路

1、为了解决上述技术问题,本发明提供射频超宽带cmos低噪声放大器的制造方法。

2、本发明提供的射频超宽带cmos低噪声放大器的制造方法采用如下的技术方案:

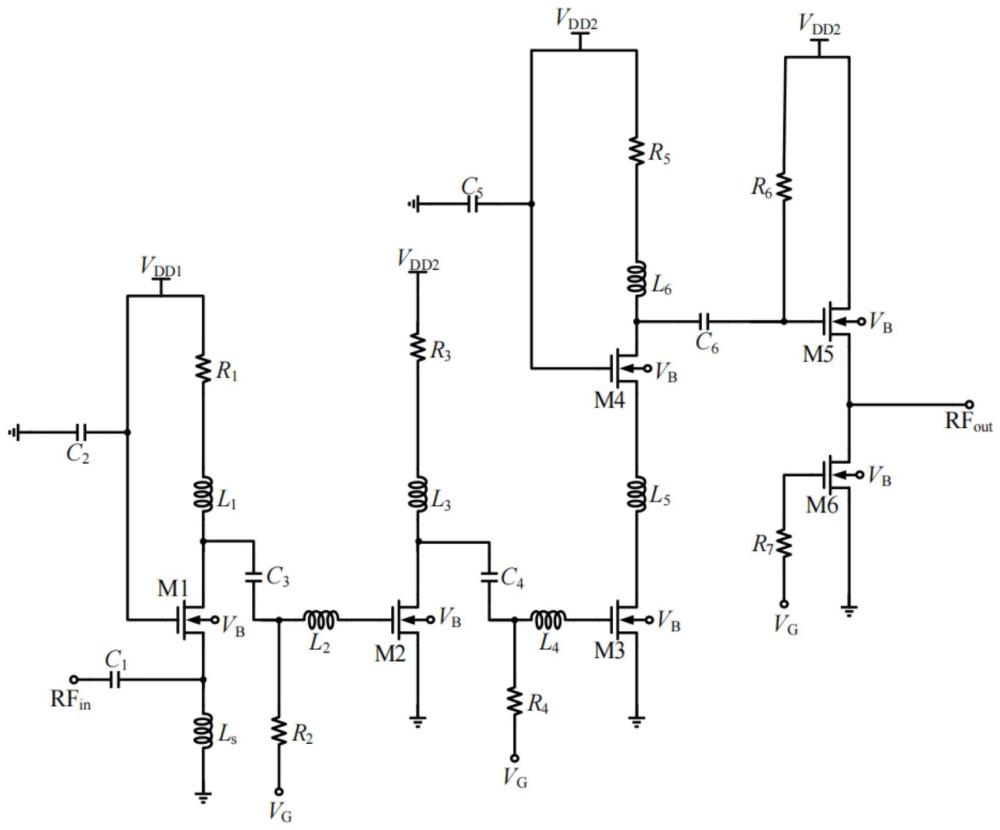

3、射频超宽带cmos低噪声放大器的制造方法,包括双谐振负载网络结构、共栅极结构和负载r-l-c结构,放大级采用三谐振网络匹配技术,其中m1、m2、m3均为nmos管。

4、可选的,电路的输出级采用源跟随器结构。

5、可选的,电路在整个带宽范围内实现输入阻抗匹配。

6、可选的,双谐振负载网络结构的输入阻抗为:在放大器的输入端口需要实现输入阻抗的匹配。

7、可选的,通过减小m1的跨导来降低m1管的偏置电压,使电路功耗减少。

8、可选的,当电路频率达到3ghz时,m1输入端并联结构ls-cgs1与m1输出负载l1-cd1同时发生谐振,电路呈纯阻性,电路增益上升。

9、可选的,在中频处,电感l1和串联结构l2-cgs2-c3共同作用使电路阻抗增大。

10、可选的,当电路处于高频时,m2输出端并联结构l3-cd2与串联结构l4-c4-cgs3同时发生谐振,减小了电路高频时寄生电容对电路的影响。

11、综上所述,本发明包括以下至少一种有益技术效果:

12、1.放大级采用三谐振网络匹配技术,利用这一技术在电路中实现了较高的增益,并拓展了带宽;电路的输出级采用源跟随器结构,此外,在电路中通过引入衬底偏置技术,使电路的功耗显著降低;

13、2.使电路的输入阻抗可以通过负载阻抗zl(s)部分电容与电感的谐振作用实现,不需要再仅仅取决于nmos管m1的跨导,从而可以通过减小m1的跨导来降低m1管的偏置电压,使电路功耗减少;

14、3.在低频ωlow处,输入端并联结构ls-cgs1与m1输出负载l1-cd1同时发生谐振;在中高频处,电感l1和串联结构l2-cgs2共同作用来使电路负载阻抗增大,实现输入阻抗的匹配。

技术特征:

1.射频超宽带cmos低噪声放大器的制造方法,其特征在于:包括双谐振负载网络结构、共栅极结构和负载r-l-c结构,放大级采用三谐振网络匹配技术,其中m1、m2、m3均为nmos管。

2.根据权利要求1所述的射频超宽带cmos低噪声放大器的制造方法,其特征在于:电路的输出级采用源跟随器结构。

3.根据权利要求1所述的射频超宽带cmos低噪声放大器的制造方法,其特征在于:电路在整个带宽范围内实现输入阻抗匹配。

4.根据权利要求1所述的射频超宽带cmos低噪声放大器的制造方法,其特征在于:双谐振负载网络结构的输入阻抗为:在放大器的输入端口需要实现输入阻抗的匹配。

5.根据权利要求4所述的射频超宽带cmos低噪声放大器的制造方法,其特征在于:通过减小m1的跨导来降低m1管的偏置电压,使电路功耗减少。

6.根据权利要求1所述的射频超宽带cmos低噪声放大器的制造方法,其特征在于:当电路频率达到3ghz时,m1输入端并联结构ls-cgs1与m1输出负载l1-cd1同时发生谐振,电路呈纯阻性,电路增益上升。

7.根据权利要求1所述的射频超宽带cmos低噪声放大器的制造方法,其特征在于:在中频处,电感l1和串联结构l2-cgs2-c3共同作用使电路阻抗增大。

8.根据权利要求1所述的射频超宽带cmos低噪声放大器的制造方法,其特征在于:当电路处于高频时,m2输出端并联结构l3-cd2与串联结构l4-c4-cgs3同时发生谐振,减小了电路高频时寄生电容对电路的影响。

技术总结

本发明涉及射频超宽带CMOS低噪声放大器的制造方法,包括双谐振负载网络结构、共栅极结构和负载R‑L‑C结构,放大级采用三谐振网络匹配技术,其中M1、M2、M3均为NMOS管,电路的输出级采用源跟随器结构,电路在整个带宽范围内实现输入阻抗匹配,双谐振负载网络结构的输入阻抗为:在放大器的输入端口需要实现输入阻抗的匹配,通过减小M1的跨导来降低M1管的偏置电压,使电路功耗减少,放大级采用三谐振网络匹配技术,利用这一技术在电路中实现了较高的增益,并拓展了带宽;电路的输出级采用源跟随器结构,此外,在电路中通过引入衬底偏置技术,使电路的功耗显著降低。

技术研发人员:师健,茆飞

受保护的技术使用者:无锡达晶晟集成电路有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!