一种脉冲展宽系统的制作方法

本发明涉及芯片电路设计,特别是涉及一种脉冲展宽系统。

背景技术:

1、跨时钟域问题(clock domain crossing,cdc)是芯片设计过程中经常会遇到的问题,主要指两个不同频率或相位不固定的时钟系统中信号的相互传递。其中,从慢时钟域到快时钟域的信号处理较为常见简便,而从快时钟域到慢时钟域的信号相对而言要更加复杂,如图2所示。对于从快时钟域送往慢时钟域的单bit信号,常见的处理方式为实现将快时钟域的脉冲用快时钟展宽后送到慢时钟域再结合握手协议处理。尽管这种方式较为通用,但是需要两个时钟域同时对信号进行处理,时钟域之间的交互更为频繁,增加了设计的复杂度。

技术实现思路

1、本发明的目的是提供一种脉冲展宽系统,通过仅在慢时钟域处理窄脉冲的方式,以满足更灵活的设计需求。

2、为实现上述目的,本发明提供了如下方案:

3、一种脉冲展宽系统,所述脉冲展宽系统包括:

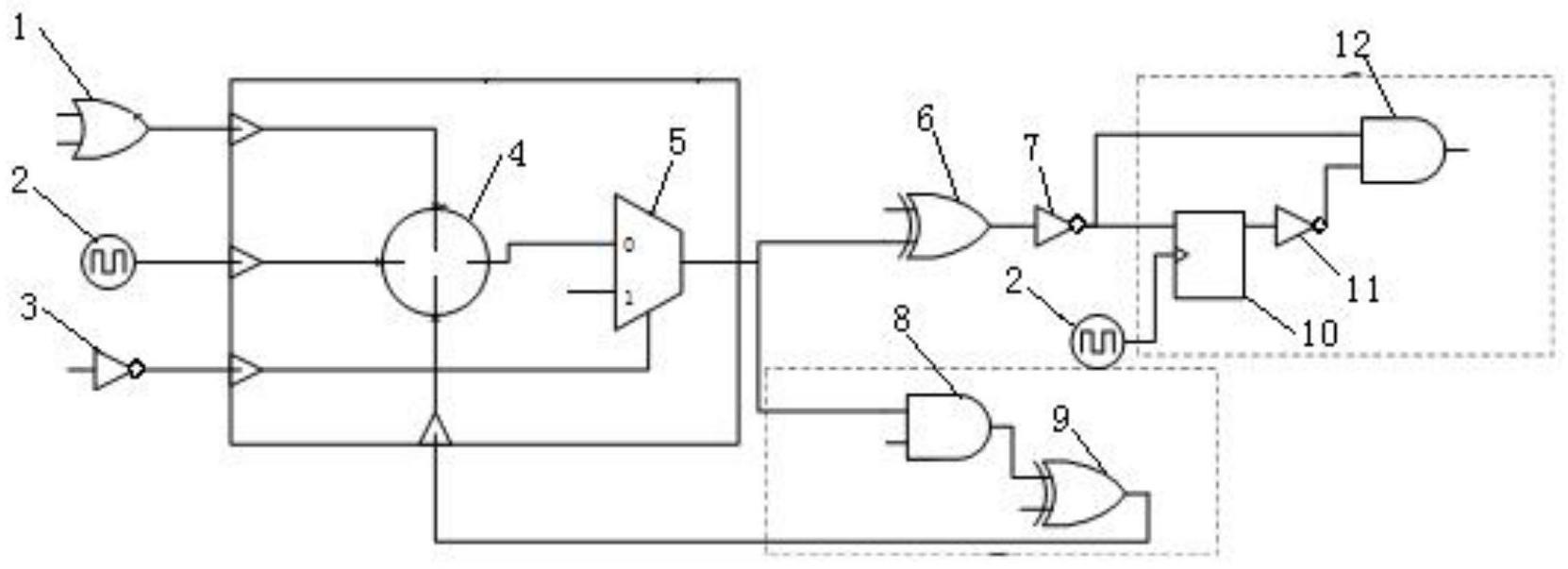

4、计数模块、比较逻辑模块和展宽电路;

5、所述计数模块的第一输入端用于接收窄脉冲,所述计数模块的第二输入端用于接收低频时钟信号,所述计数模块的第三输入端与所述比较逻辑模块的输出端连接;所述计数模块的第一输出端与所述比较逻辑电路的第一输入端连接;所述计数模块的第二输出端与所述展宽电路的输入端连接;所述比较逻辑模块的第二输入端用于接收预设阈值;

6、所述计数模块用于基于所述低频时钟信号,对所述窄脉冲的上升沿进行计数,并将所述计数结果传输至所述展宽电路和所述比较逻辑电路;

7、所述比较逻辑电路用于根据所述计数结果和所述预设阈值控制所述计数模块是否继续计数;

8、所述展宽电路用于基于所述计数结果对所述窄脉冲展宽,得到展宽信号。

9、可选地,所述计数模块包括计数器和比较器;

10、所述计数器的第一输入端用于接收所述窄脉冲,所述计数器的第二输入端用于接收低频时钟信号,所述计数器的第三输入端与所述比较逻辑模块的输出端连接;所述计数器的输出端与所述比较器的第一输入端连接;所述比较器的第二输入端用于接收计数器位数,所述比较器的第三输入端用于接收使能信号;所述比较器的第一输出端与所述所述比较逻辑电路的输入端连接,所述比较器的第二输出端与所述展宽电路的输入端连接;

11、所述比较器用于根据所述使能信号控制所述计数模块是否开始对窄脉冲的上升沿进行计数;

12、所述计数器用于:

13、基于所述低频时钟信号,在接收到所述窄脉冲的上升沿时产生结束信号,并将所述结束信号传输至所述展宽电路;

14、基于所述低频时钟信号,在接收到所述窄脉冲的上升沿时复位计数器的计数值重新开始计数,并将所述计数结果传输至所述展宽电路和所述比较逻辑电路;

15、所述结束信号用于使所述展宽电路产生下降沿的展宽信号。

16、可选地,所述比较逻辑电路用于根据所述计数结果和所述预设阈值控制所述计数模块是否继续计数,具体包括:

17、所述比较逻辑电路用于当所述计数结果等于预设阈值时,产生保持信号,并将所述保持信号传输至所述计数模块;

18、所述保持信号用于控制所述计数模块停止计数。

19、可选地,所述脉冲展宽系统还包括:

20、展宽脉冲采样模块;

21、所述展宽脉冲采样模块的第一输入端与所述展宽电路的输出端连接;所述展宽脉冲采样模块的第二输入端用于接收低频时钟信号;

22、所述展宽脉冲采样模块用于基于所述低频时钟信号,采集所述展宽信号的上升沿,得到单时钟周期长度的宽脉冲。

23、可选地,所述比较逻辑电路包括:第一与门和第一异或门;

24、所述第一与门的第一输入端与所述计数模块的输出端连接,所述第一与门的第二输入端用于接收所述预设阈值;所述第一与门的输出端与所述第一异或门的第一输入端连接;所述第一异或门的第二输入端用于接收预设阈值,所述第一异或门的输出端与所述计数模块的第三输入端连接;

25、所述第一与门用于根据所述预设阈值对所述计数结果进行处理,得到第一处理结果;

26、所述第一异或门用于根据所述预设阈值和所述第一处理结果,控制所述计数模块是否继续计数。

27、可选地,所述展宽脉冲采样模块包括:d触发器、第一非门和第二与门;

28、所述d触发器的时钟端用于接收低频时钟信号,所述d触发器的输入端与所述展宽电路连接,所述d触发器的输出端与所述第一非门的输入端连接;所述第一非门的输出端与所述第二与门的第一输入端连接;所述第二与门的第二输入端与所述展宽电路连接;

29、所述d触发器用于基于所述低频时钟信号,采集所述展宽信号的上升沿,得到待处理的单时钟周期长度的宽脉冲,并将待处理的单时钟周期长度的宽脉冲传输至所述第一非门;

30、所述第一非门用于对待处理的单时钟周期长度的宽脉冲进行处理,得到处理后的单时钟周期长度的宽脉冲,并将处理后的单时钟周期长度的宽脉冲传输至所述第二与门;

31、所述第二与门用于基于处理后的单时钟周期长度的宽脉冲和所述展宽信号,得到单时钟周期长度的宽脉冲。

32、根据本发明提供的具体实施例,本发明公开了以下技术效果:

33、本发明公开一种脉冲展宽系统,该系统包括:所述计数模块用于基于所述低频时钟信号,对所述窄脉冲的上升沿进行计数,并将所述计数结果传输至所述展宽电路和所述比较逻辑电路;所述比较逻辑电路用于根据所述计数结果和所述预设阈值控制所述计数模块是否继续计数;所述展宽电路用于基于所述计数结果对所述窄脉冲展宽,得到展宽信号。本发明通过仅在慢时钟域处理窄脉冲的方式,以满足更灵活的设计需求。

技术特征:

1.一种脉冲展宽系统,其特征在于,所述脉冲展宽系统包括:

2.根据权利要求1所述的脉冲展宽系统,其特征在于,所述计数模块包括计数器和比较器;

3.根据权利要求1所述的脉冲展宽系统,其特征在于,所述比较逻辑电路用于根据所述计数结果和所述预设阈值控制所述计数模块是否继续计数,具体包括:

4.根据权利要求1所述的脉冲展宽系统,其特征在于,所述脉冲展宽系统还包括:

5.根据权利要求1所述的脉冲展宽系统,其特征在于,所述比较逻辑电路包括:第一与门和第一异或门;

6.根据权利要求4所述的脉冲展宽系统,其特征在于,所述展宽脉冲采样模块包括:d触发器、第一非门和第二与门;

技术总结

本发明公开一种脉冲展宽系统,涉及芯片电路设计技术领域;该系统包括:所述计数模块用于基于所述低频时钟信号,对所述窄脉冲的上升沿进行计数,并将所述计数结果传输至所述展宽电路和所述比较逻辑电路;所述比较逻辑电路用于根据所述计数结果和所述预设阈值控制所述计数模块是否继续计数;所述展宽电路用于基于所述计数结果对所述窄脉冲展宽,得到展宽信号。本发明通过仅在慢时钟域处理窄脉冲的方式,以满足更灵活的设计需求。

技术研发人员:陈志刚,徐红如,陶长来

受保护的技术使用者:南京英锐创电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!