一种抗干扰的电平转换电路和方法与流程

本发明涉及开关电源,特别涉及一种抗干扰的电平转换电路和方法。

背景技术:

1、在开关电源领域,随着高压大电流需求的逐渐发展,dcdc芯片承担的电压电流能力越来越高。在设计高压大电流dcdc芯片时,dv/dt、di/dt的挑战越来越明显。

2、例如,在异步dcdc芯片的换流过程中,上管关断后,功率转换点sw的电位由高翻低,接下来由片外肖特基二极管完成续流,但由于pcb走线的寄生电感和肖特基二极管的寄生电感的原因,片外肖特基二极管并不能立刻开始续流,功率电感则会将功率转换点sw的电荷抽走,使得功率转换点sw向负电压过冲。同样的,在同步dcdc芯片换流过程中,上管关闭后下管开启前的死区时间内,功率转换点sw的电位也可能过负。过负的电压点会使芯片出现异常,甚至损坏。

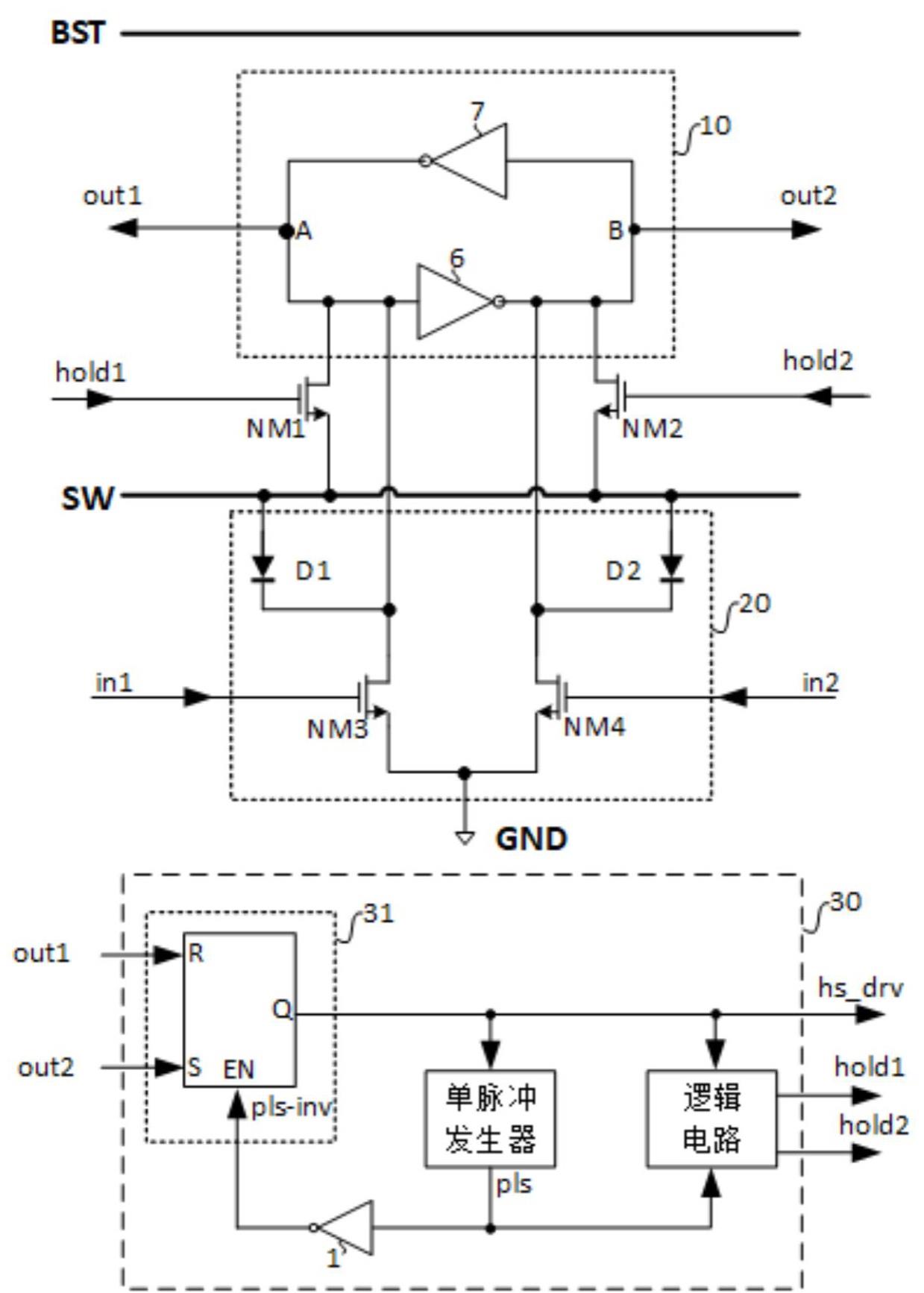

3、dcdc芯片中,电平转换电路负责将低电压域(gnd-sw)的逻辑控制信号转换到高电压域(bst-sw)并锁存,随后送至驱动电路用于控制上管的开关,电路示意图见图1。其中,bst为自举电压点位,通常,bst电压为sw点电压叠加一个自举电容上的电压,一般bst-sw之间的压差设计为5v。

4、在功率转换点sw电平以极高的速度上升下降过程中,或遇上其他噪声干扰的情况,锁存电路则可能发生跳变,信号out2和信号out1出现错误,导致驱动电路输出的驱动信号hs_drv出现错误,功率管出现误开关,造成极大风险,严重情况可导致上下管对通,芯片烧毁。

技术实现思路

1、针对现有技术中存在的问题,提供了一种抗干扰的电平转换电路和方法,通过在bst-sw电压域设置两个开关管以及采用相应的控制电路配合完成bst-sw电压域内的逻辑电平时序控制,提高电平转换电路抗噪声的能力。

2、本发明一方面提供了一种抗干扰的电平转换电路,包括:反相单元,设置在高电压域内,所述高电压域具有高电压位和低电压位,所述反相单元具有第一输出端和第二输出端,所述反相单元根据其第一输出端和第二输出端的电位输出位于高电压域的第一逻辑电平信号和第二逻辑电平信号,其中,所述反相单元的第一输出端的电位和所述反相单元的第二输出端的电位为高电压域内的逻辑互补电位;开关单元,用于接收低电压域内的控制信号,并根据所述控制信号下拉所述反相单元的第一输出端的电位或所述反相单元的第二输出端的电位至高电压域内的低电压位,其中,低电压域具有高电压位和低电压位,高电压域的高电压位大于低电压域的高电压位,高电压域的低电压位大于低电压域的低电压位;第一开关管,具有第一端、第二端及控制端,所述第一开关管的第一端耦接所述反相单元的第一输出端,所述第一开关管的第二端耦接高电压域的低电压位,所述第一开关管的控制端接收第一保持信号;第二开关管,具有第一端、第二端及控制端,所述第二开关管的第一端耦接所述反相单元的第二输出端,所述第二开关管的第二端耦接高电压域的低电压位,所述第二开关管的控制端接收第二保持信号;以及控制单元,接收所述第一逻辑电平信号和第二逻辑电平信号,并根据所述第一逻辑电平信号和第二逻辑电平信号产生功率开关管驱动信号、所述第一保持信号和所述第二保持信号,其中,所述功率开关管驱动信号用于控制待控功率开关管的导通和关断。

3、本发明另一方面提供了一种电平转换电路的抗干扰方法,该电平转换电路包括反相单元、开关单元和锁存电路,所述反相单元设置在高电压域内用于输出高电压域内的第一逻辑电平信号和第二逻辑电平信号;所述开关单元用于接收低电压域内的控制信号,并根据控制信号下拉所述第一逻辑电平信号或所述第二逻辑电平信号至高电压域内的低电压位;所述锁存电路根据所述第一逻辑电平信号或所述第二逻辑电平信号产生功率开关管驱动信号;所述抗干扰方法包括:根据功率开关管驱动信号产生具有固定脉冲宽度的脉冲信号;在所述固定脉冲宽度对应的时间窗口期内,控制所述锁存电路不工作以使所述功率开关管驱动信号的逻辑状态不变;以及在所述固定脉冲宽度对应的时间窗口期内,根据所述功率开关管驱动信号的逻辑状态对第一逻辑电平信号和第二逻辑电平信号的逻辑状态进行校准和保持。

4、与现有技术相比,采用上述技术方案的有益效果为:本发明通过对bst-sw电压域内的逻辑电平时序控制,有效提高电平转换电路的抗噪声能力,保证了输出逻辑电平的准确性,避免因输出逻辑电平出错而导致驱动信号错误引起的功率管误开启、芯片烧毁的风险。

技术特征:

1.一种抗干扰的电平转换电路,其特征在于,包括:

2.根据权利要求1所述的抗干扰的电平转换电路,其特征在于,所述控制单元包括:

3.根据权利要求2所述的抗干扰的电平转换电路,其特征在于,所述逻辑电路包括第二非门、第三非门、第四非门、第五非门、第一或非门以及第二或非门;

4.根据权利要求2或3所述的抗干扰的电平转换电路,其特征在于,所述锁存电路包括rs触发器,所述rs触发器具有第一输入端、第二输入端、使能端与输出端,所述rs触发器的第一输入端接收所述第一逻辑电平信号,所述rs触发器的第二输入端接收所述第二逻辑电平信号,所述rs触发器的输出端输出所述功率开关管驱动信号,所述rs触发器的使能端接收所述脉冲信号的反相信号。

5.根据权利要求2所述的抗干扰的电平转换电路,其特征在于,所述锁存电路在由所述脉冲信号的脉冲宽度对应的时间窗口期内保持输出的所述功率开关管驱动信号的逻辑状态不变。

6.根据权利要求2所述的抗干扰的电平转换电路,其特征在于,所述第一开关管与第二开关管在由所述脉冲信号的脉冲宽度对应的时间窗口期内,根据所述第一保持信号和所述第二保持信号保持所述反相单元输出的所述第一逻辑电平信号和所述第二逻辑电平信号的逻辑状态不变。

7.根据权利要求2所述的抗干扰的电平转换电路,其特征在于,在由所述脉冲信号的脉冲宽度对应的时间窗口期外,所述第一开关管和所述第二开关管保持关断。

8.根据权利要求3所述的抗干扰的电平转换电路,其特征在于,所述单脉冲发生器在所述功率开关管驱动信号每次从第一逻辑电平转变为第二逻辑电平时产生具有第一脉冲宽度的脉冲信号。

9.根据权利要求1所述的抗干扰的电平转换电路,其特征在于,所述控制信号包括第一控制信号和第二控制信号,第一控制信号和第二控制信号逻辑互补,所述开关单元包括:

10.一种用于电平转换电路的抗干扰方法,其特征在于,该电平转换电路包括反相单元、开关单元和锁存电路,所述反相单元设置在高电压域内用于输出高电压域内的第一逻辑电平信号和第二逻辑电平信号;所述开关单元用于接收低电压域内的控制信号,并根据控制信号下拉所述第一逻辑电平信号或所述第二逻辑电平信号至高电压域内的低电压位;所述锁存电路根据所述第一逻辑电平信号或所述第二逻辑电平信号产生功率开关管驱动信号;所述抗干扰方法包括:

技术总结

本发明提供了一种抗干扰的电平转换电路和方法。该电平转换电路包括反相单元、开关单元、第一开关管、第二开关管。反相单元输出位于高电压域的第一逻辑电平信号和第二逻辑电平信号;开关单元用于根据接收的控制信号下拉反相单元的第一输出端或第二输出端的电位至高电压域内的低电压位;第一开关管耦接在反相单元的第一输出端和高电压域的低电压位之间;第二开关管耦接在反相单元的第二输出端和高电压域的低电压位之间;控制单元根据第一逻辑电平信号和第二逻辑电平信号产生驱动功率开关管的功率开关管驱动信号以及控制第一开关管、第二开关管的保持信号。本发明有效提高电平转换电路的抗噪声能力,保证了功率开关管驱动信号的逻辑电平的准确性。

技术研发人员:周枭

受保护的技术使用者:晶艺半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!