一种锁相环带宽自适应并网逆变器校准方法及电路结构与流程

本发明涉及锁相环电路,尤其涉及一种锁相环带宽自适应并网逆变器校准方法及电路结构。

背景技术:

1、近年来,在并网逆变器系统中,锁相环(phase-locked loop,pll)被广泛应用于实现与电网的频率和相位同步。传统的pll带宽校准方法通常是针对影响带宽的独立参数进行校准,例如,vco(voltage-controlled oscillator)增益、滤波器参数、charge pump(电荷泵)电流等。通过独立参数的校准,可以调整锁相环的带宽以满足特定的锁定要求。

2、然而,这种独立参数校准方式存在一个重要问题,即无法保证不同锁定频点下的带宽一致性。由于不同频率范围内的锁定要求不同,独立参数的校准可能导致在不同频率下的带宽不一致。

3、例如,当校准参数针对较低频率范围进行优化时,锁相环的带宽可能被调整得较窄,以提高锁定性能。然而,在较高频率范围内,由于参数校准没有针对该频率范围进行优化,带宽可能过窄,导致锁相环无法迅速跟踪频率变化。

4、因此,现有的独立参数校准方法无法保证不同锁定频点的带宽一致性。这可能导致并网逆变器在不同频率范围内的性能存在差异,影响逆变器与电网的稳定性和能量注入质量。

技术实现思路

1、鉴于上述现有存在的问题,提出了本发明。

2、因此,本发明提供了一种锁相环带宽自适应并网逆变器校准方法及电路结构解决现有锁相环带宽校准不能保证不同锁定频点的带宽一致性的问题。

3、为解决上述技术问题,本发明提供如下技术方案:

4、第一方面,本发明提供了一种锁相环带宽自适应并网逆变器校准方法,包括:

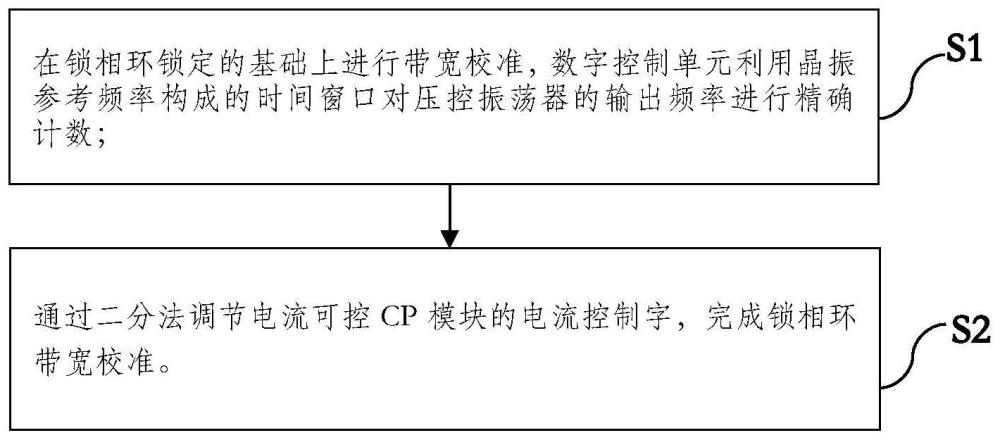

5、在锁相环锁定的基础上进行带宽校准,数字控制单元利用晶振参考频率构成的时间窗口对压控振荡器的输出频率进行精确计数;

6、通过二分法调节电流可控cp模块的电流控制字,完成锁相环带宽校准。

7、作为本发明所述的锁相环带宽自适应并网逆变器校准方法的一种优选方案,其中:

8、所述锁相环带宽校准中控制电路的校准过程,包括如下步骤:

9、将icp<n:0>设置在中心值,即2n;

10、当第一控制开关闭合、第二控制开关断开时,控制锁相环在所需的频点上进行正常锁定,锁定频率记为f0,锁定之后压控振荡器的调谐电压记为vtune0,数字控制单元利用晶振参考频率作为计数窗口,对f0信号进行计数,记录下分频比ndiv;

11、当第一控制开关断开,第二控制开关闭合时,电荷泵up/dn电流的控制信号控制电流可控cp模块输出持续的up电流;输出电流经过电阻产生压降,流入电压跟随器;压控振荡器的调谐电压产生变化,变化值记为vtune1;带动压控振荡器的输出频率变化,变化值记为f1;

12、数字控制单元计算出f1和f0的频率差值,将频率差值除以分频比ndiv,得到锁相环的环路带宽;

13、数字控制单元通过调节icp电流,使得锁相环的环路带宽收敛到预定值,完成锁相环的带宽校准。

14、作为本发明所述的锁相环带宽自适应并网逆变器校准方法的一种优选方案,其中:

15、所述锁相环的环路带宽表示为:

16、

17、其中,r1为滤波器,rs为采样电阻,kvco是vco的增益,比例系数为kr=rs/r1,iup为电荷泵的up电流。

18、作为本发明所述的锁相环带宽自适应并网逆变器校准方法的一种优选方案,其中:

19、所述电流可控cp模块中的up电流和dn电流是可控的,电流值由icp<n:0>进行控制。

20、作为本发明所述的锁相环带宽自适应并网逆变器校准方法的一种优选方案,其中:

21、所述锁相环带宽校准中控制电路的校准过程是以调节电流可控cp模块中的up电流进行校准,校准得到的icp<n:0>控制字作为实际工作时的电流控制字。

22、第二方面,本发明提供了一种锁相环带宽自适应并网逆变器校准电路结构,包括电流可控cp模块和数字控制单元组成的锁相环带宽校准控制电路;

23、所述数字控制单元分别与压控振荡器vco和电流可控cp模块相连接。

24、作为本发明所述的锁相环带宽自适应并网逆变器校准电路结构的一种优选方案,其中:

25、所述锁相环带宽校准控制电路,还包括控制开关,控制开关分为第一控制开关和第二控制开关;

26、所述第一控制开关和第二控制开关分别位于不同的支路上。

27、作为本发明所述的锁相环带宽自适应并网逆变器校准电路结构的一种优选方案,其中:

28、所述锁相环带宽校准控制电路,还包括采样保持电容cs,采样电阻rs和节点电压v;

29、所述节点电压v包括第一节点电压vcs和第二节点电压vbuf;

30、所述第一控制开关,第一节点电压vcs和采样保持电容cs位于同一侧;

31、所述第二控制开关,第二节点电压vbuf和采样电阻rs位于同一侧。

32、作为本发明所述的锁相环带宽自适应并网逆变器校准电路结构的一种优选方案,其中:

33、所述锁相环带宽校准控制电路,还包括电压跟随器buffer;

34、所述电压跟随器buffer正极通过第一节点电压vcs连接第一控制开关,电压跟随器buffer负极通过第二节点电压vbuf连接第二控制开关;所述电压跟随器buffer驱动第二节点电压vbuf跟随第一节点电压vcs。

35、作为本发明所述的锁相环带宽自适应并网逆变器校准电路结构的一种优选方案,其中:

36、所述采样保持电容cs为低漏电采样保持电容。

37、本发明的有益效果:本发明利用数模混合电路和锁相环带宽自适应并网逆变器校准方法,能大幅提升锁相环带宽的一致性。在基于锁相环的频率调制应用中,能发挥出良好的技术优势。

技术特征:

1.一种锁相环带宽自适应并网逆变器校准方法,其特征在于:

2.如权利要求1所述的锁相环带宽自适应并网逆变器校准方法,其特征在于:所述锁相环带宽校准中控制电路的校准过程,包括如下步骤:

3.如权利要求1或2所述的锁相环带宽自适应并网逆变器校准方法,其特征在于:所述锁相环的环路带宽表示为:

4.如权利要求3所述的锁相环带宽自适应并网逆变器校准方法,其特征在于:所述电流可控cp模块中的up电流和dn电流是可控的,电流值由icp<n:0>进行控制。

5.如权利要求4所述的锁相环带宽自适应并网逆变器校准方法,其特征在于:所述锁相环带宽校准中控制电路的校准过程是以调节电流可控cp模块中的up电流进行校准,校准得到的icp<n:0>控制字作为实际工作时的电流控制字。

6.一种锁相环带宽自适应并网逆变器校准电路结构,其特征在于,包括电流可控cp模块和数字控制单元组成的锁相环带宽校准控制电路;

7.如权利要求6所述的锁相环带宽自适应并网逆变器校准电路结构,其特征在于,所述锁相环带宽校准控制电路,还包括控制开关,控制开关分为第一控制开关和第二控制开关;

8.如权利要求7所述的锁相环带宽自适应并网逆变器校准电路结构,其特征在于,

9.如权利要求8所述的锁相环带宽自适应并网逆变器校准电路结构,其特征在于,所述锁相环带宽校准控制电路,还包括电压跟随器buffer;

10.如权利要求9所述的锁相环带宽自适应并网逆变器校准电路结构,其特征在于,

技术总结

本发明涉及锁相环电路技术领域,公开了一种锁相环带宽自适应并网逆变器校准方法及电路结构,包括:在锁相环锁定的基础上进行带宽校准,数字控制单元利用晶振参考频率构成的时间窗口对压控振荡器的输出频率进行精确计数;通过二分法调节电流可控CP模块的电流控制字,完成锁相环带宽校准。该校准电路,在PLL锁定的基础上进行校准,从而达到频率自适应的效果。

技术研发人员:王锐,帅柏林,李建军

受保护的技术使用者:广芯微电子(苏州)有限公司

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!