一种基于数字相位发生器和选择器的CDR电路的制作方法

本发明涉及集成电路,特别涉及一种基于数字相位发生器和选择器的cdr电路。

背景技术:

1、在串行数据接口系统中,接收器接收到的数据流是不同步而且有噪声。为了后续处理,定时信息、时钟必须从数据中提取,以便同步工作。而且数据必须“重定时”,以便去除传输过程中的抖动和噪声干扰。

2、时钟提取和数据重定时被称为“时钟和数据的恢复”(cdr)。cdr电路有多种实现方式,一般常见的基于pll的cdr电路如图1所示,cdrloop里包含一模拟pll来实现时钟恢复和数据恢复,但是电路结构相对复杂,需要较大的功耗和面积。

技术实现思路

1、本发明的目的在于提供一种基于数字相位发生器和选择器的cdr电路,以解决背景技术中的问题。

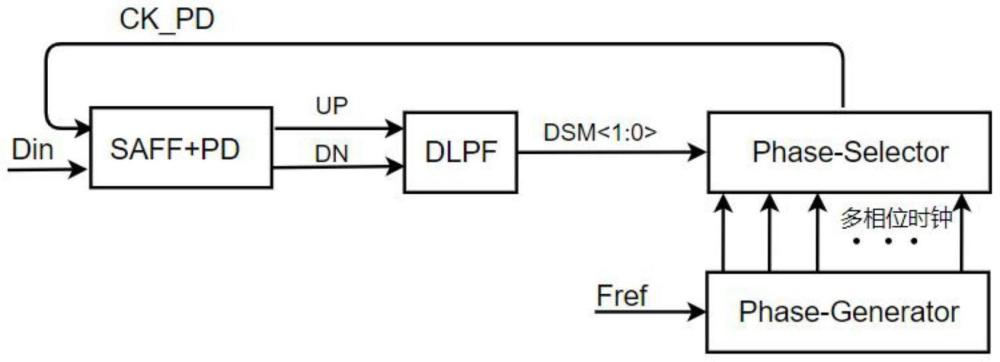

2、为解决上述技术问题,本发明提供了一种基于数字相位发生器和选择器的cdr电路,包括读出放大器触发器、bang-bang型鉴相器、滤波器、相位发生器及相位选择器;其中,

3、在同一时钟周期内,时钟ck_pd通过放大器触发器对数据din的中心和沿分别进行一次采集,bang-bang鉴相器输出信号up/dn至滤波器进行滤波后输出dsm<1:0>;

4、相位发生器的输入端接入锁相环提供的时钟fref,产生多相位时钟至相位选择器;相位选择器产生时钟ck_pd至bang-bang型鉴相器;

5、所述bang-bang型鉴相器判断时钟ck_pd与数据din之间的相位关系,当时钟ck_pd滞后于数据din时,信号up=1且信号dn=0;当时钟ck_pd超前数据din时,信号up=0且信号dn=1。

6、在一种实施方式中,所述相位发生器采用数字的相位shifter方式,其中来自锁相环的输入时钟fref被n倍分频后产生时钟ck_div,fref连续shifter n个fref时钟周期,每shifter一个周期,时钟ck_div的相位后移360°/n,以此产生n个阶段的时钟,且相邻相位时钟的相位差为360°/n。

7、在一种实施方式中,所述相位选择器受滤波器输出dsm<1:0>控制,根据反馈时钟ck_pd和数据din的相位关系,从相位发生器生成的n个相位时钟中选出其中一个,再反馈给读出放大器触发器和bang-bang型pd。

8、在一种实施方式中,所述相位选择器包括n个单元shf,所述单元shf选择是将输出相位前移一位、后移一位还是保持不变。

9、本发明提供的一种基于数字相位发生器和选择器的cdr电路,采用数字低通滤波器、数字的相位发生和选择器,模拟部分的电路占比很小,简化了电路架构,极大节省了版图面积。相位生成电路基于pll输入高频时钟,采用时钟shifter的方式,电路规模小。相位选择器采用全数字方式实现,配合数字滤波器,实现了对输入数据的相位跟踪、数据和时钟的恢复。

技术特征:

1.一种基于数字相位发生器和选择器的cdr电路,其特征在于,包括读出放大器触发器、bang-bang型鉴相器、滤波器、相位发生器及相位选择器;其中,

2.如权利要求1所述的基于数字相位发生器和选择器的cdr电路,其特征在于,所述相位发生器采用数字的相位shifter方式,其中来自锁相环的输入时钟fref被n倍分频后产生时钟ck_div,fref连续shifter n个fref时钟周期,每shifter一个周期,时钟ck_div的相位后移360°/n,以此产生n个阶段的时钟,且相邻相位时钟的相位差为360°/n。

3.如权利要求2所述的基于数字相位发生器和选择器的cdr电路,其特征在于,所述相位选择器受滤波器输出dsm<1:0>控制,根据反馈时钟ck_pd和数据din的相位关系,从相位发生器生成的n个相位时钟中选出其中一个,再反馈给读出放大器触发器和bang-bang型pd。

4.如权利要求3所述的基于数字相位发生器和选择器的cdr电路,其特征在于,所述相位选择器包括n个单元shf,所述单元shf选择是将输出相位前移一位、后移一位还是保持不变。

技术总结

本发明公开一种基于数字相位发生器和选择器的CDR电路,属于集成电路领域,包括读出放大器触发器、bang‑bang型鉴相器、滤波器、相位发生器及相位选择器;在同一时钟周期内,时钟CK_PD通过放大器触发器对数据Din的中心和沿分别进行一次采集,bang‑bang鉴相器输出信号UP/DN至滤波器进行滤波后输出DSM<1:0>;相位发生器的输入端接入锁相环提供的时钟Fref,产生多相位时钟至相位选择器;相位选择器产生时钟CK_PD至bang‑bang型鉴相器;bang‑bang型鉴相器判断时钟CK_PD与数据Din之间的相位关系。本发明可应用在低速数据接收器,用来对接收数据和时钟的恢复。电路结构简单,易于实现,使用方便。

技术研发人员:吴光林,程剑平

受保护的技术使用者:上海芯炽科技集团有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!