一种半导体存储单元及其阵列结构

本发明属于半导体(semiconductor)和cmos混合集成电路,具体涉及一种兼容现有cmos工艺并与cmos集成的一种半导体存储单元及其阵列结构。

背景技术:

1、近年来,信息技术的发展使得存储需求不断增长,新型半导体存储器如阻变存储器(rram)、相变存储器(pram)、磁阻存储器(mram)和铁电存储器(feram)受到广泛研究和关注。新型存储器阵列具有潜在的高密度、低功耗、高速度等特点,有可能应对日益增多的信息处理和存储需求。

2、新型半导体存储器阵列通常受到严重的写串扰和泄露通路限制,通常需要在存储单元上串联晶体管来消除串扰,形成一晶体管一存储器件(1t1r)阵列,图1展示了传统共源1t1r阵列的电路结构原理图,图中画出了8个存储器件,其中每个存储器件与一个晶体管连接,可以认为图1中的存储阵列是由左上角的位于虚线框101的存储单元经过4次重复而构成,其中每个存储单元包括第一存储器件r1、第一nmos管n1、第二存储器件r2、第二nmos管n2。在重复单元中,n1、n2的栅极分别连接到wl1与wl2,n1和n2源极相连,并且连接到公共源线sl,n1、n2的漏极分别与r1、r2连接,形成两个独立的1t1r结构,进一步地,r1与r2连接到bl以形成完整的电路结构,通过控制wl1、wl2、bl、sl上的电压即可写入或读取存储器。

3、技术的发展要求不断降低存储单元的面积,然而在图1所示的存储阵列要求相邻的存储单元之间必须具有如虚线框102所示的间隔,否则会影响存储阵列正常的读写功能,该间隔严重降低了存储单元的面积利用率,从而限制了存储阵列密度的提升。图2是图1中存储阵列的版图示意图,其中画出了16个存储器件,该版图包括4个层次,分别是有源区、栅极、存储器件和源极,其中有源区201对应于101的存储单元。图1中102的间隔对应于图2中的虚线框202,其宽度与工艺相关,一般与工艺下的晶体管栅长近似。由此可见,图1中的传统阵列结构并没有充分利用版图面积。

技术实现思路

1、针对以上现有技术中存在的问题,本发明提出了一种半导体存储单元及其阵列结构,利用公共晶体管的存储单元及阵列设计,在保持存储电路的正常读写功能和选通晶体管驱动能力的条件下,减少诸如阻变存储器(rram)、相变存储器(pram)、磁阻存储器(mram)和铁电存储器(feram)等新型存储器的阵列面积,从而提升存储阵列密度。

2、本发明的技术方案如下:

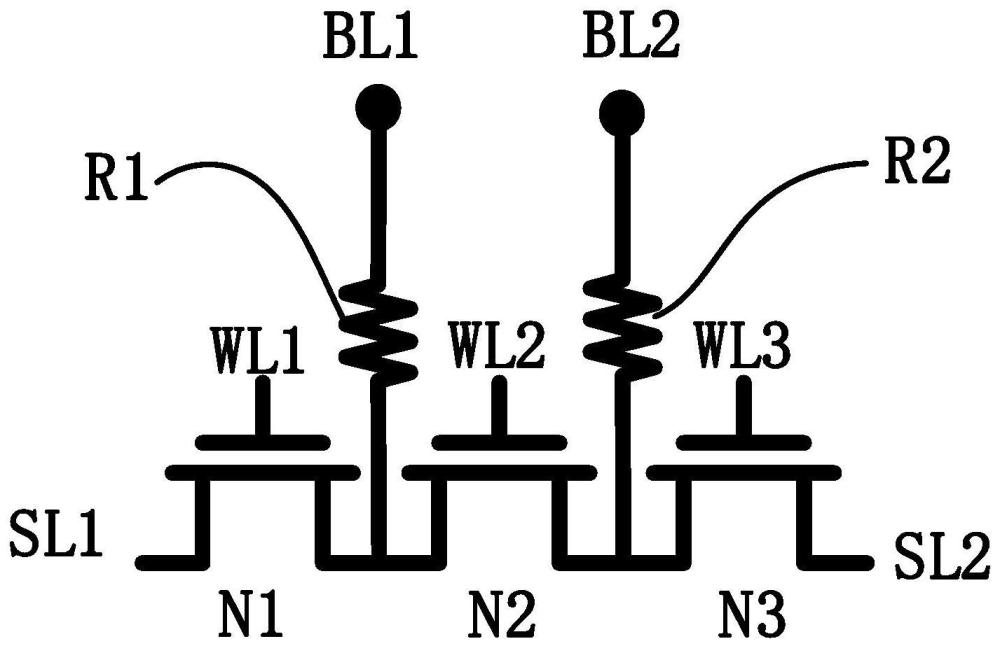

3、一种半导体存储单元,其特征在于,包括第一nmos管n1、第二nmos管n2、第三nmos管n3、第一存储器r1和第二存储器r2,第一存储器件r1、第二存储器件r2分别为二端新型存储器件,该半导体存储单元连接字线wl1、字线wl2、字线wl3、源线sl1、源线sl2、位线bl1和位线bl2;其中,所述第一nmos管n1的源极接源线sl1、其栅极接字线wl1、其漏极接所述第二nmos管n2一端的源极/漏极,所述第二nmos管n2另一端源极/漏极接所述第三nmos管n3的漏极,第一nmos管n1、第二nmos管n2和第三nmos管n3连成串联结构,所述第二nmos管n2栅极接字线wl2,所述第三nmos管n3源极接源线sl2、其栅极接字线wl3;所述第一存储器r1一端接在第一nmos管n1和第二nmos管n2的连接处、其另一端接位线bl1,所述第二存储器r2一端接在第三nmos管n3和第二nmos管n2的连接处、其另一端接位线bl2。

4、进一步,诉述第一存储器r1、第二存储器件r2分别为阻变存储器、相变存储器、磁阻存储器或者铁电存储器。

5、为了进一步说明本发明相对于传统结构的优势,本发明还提供了由上述存储单元构成的存储阵列,其特征在于,为所述存储单元沿着横向、纵向排列成的矩阵结构,其中,同一列的存储单元间共享字线wl1、字线wl2、字线wl3,即每列中各存储单元的字线wl1相连、字线wl2相连、字线wl3相连,同一行的存储单元间共享位线bl1与位线bl2,即每行中各存储单元的位线bl1相连、位线bl2相连,同一行的存储单元间通过源线相连,即每行中前一个存储单元的源线sl2与后一个存储单元的源线sl1相连,依次连接形成串联结构,且同一行中各存储单元的源线sl1、源线sl2均连接至该行的统一源线sl上。

6、综上所述,本发明利用公共晶体管的存储单元及阵列设计,用以降低新型存储器的存储阵列面积,从而提升存储阵列密度。与现有的存储单元不同,本发明的存储单元在操作时能够打开单元内的三个晶体管,从而有两条操作电流通路,能够降低存储电路中对于晶体管尺寸的要求。同时,本发明提出的存储阵列中同一行的存储单元之间采用相互连接的串联结构,从而消除了原有阵列结构中相邻存储单元之间的隔离区域,提高了存储电路的面积利用率。综合以上两点,本发明能够有效地降低单个存储单元的面积,从而提升存储阵列的密度。

技术特征:

1.一种半导体存储单元,其特征在于,包括第一nmos管n1、第二nmos管n2、第三nmos管n3、第一存储器r1和第二存储器r2,第一存储器件r1、第二存储器件r2分别为二端新型存储器件,该半导体存储单元连接字线wl1、字线wl2、字线wl3、源线sl1、源线sl2、位线bl1和位线bl2;其中,所述第一nmos管n1的源极接源线sl1、其栅极接字线wl1、其漏极接所述第二nmos管n2一端的源极/漏极,所述第二nmos管n2另一端源极/漏极接所述第三nmos管n3的漏极,第一nmos管n1、第二nmos管n2和第三nmos管n3连成串联结构,所述第二nmos管n2栅极接字线wl2,所述第三nmos管n3源极接源线sl2、其栅极接字线wl3;所述第一存储器r1一端接在第一nmos管n1和第二nmos管n2的连接处、其另一端接位线bl1,所述第二存储器r2一端接在第三nmos管n3和第二nmos管n2的连接处、其另一端接位线bl2。

2.如权利要求1所述的一种半导体存储单元,其特征在于,诉述第一存储器r1、第二存储器件r2分别为阻变存储器、相变存储器、磁阻存储器或者铁电存储器。

3.一种存储阵列,其特征在于,为如权利要求1所述的存储单元沿着横向、纵向排列成的矩阵结构,其中,同一列的存储单元间共享字线wl1、字线wl2、字线wl3,即每列中各存储单元的字线wl1相连、字线wl2相连、字线wl3相连,同一行的存储单元间共享位线bl1与位线bl2,即每行中各存储单元的位线bl1相连、位线bl2相连,同一行的存储单元间通过源线相连,即每行中前一个存储单元的源线sl2与后一个存储单元的源线sl1相连,依次连接形成串联结构,且同一行中各存储单元的源线sl1、源线sl2均连接至该行的统一源线sl上。

技术总结

本发明一种半导体存储单元及其阵列结构,该存储单元包括第一NMOS管N1、第二NMOS管N2、第三NMOS管N3、第一存储器R1和第二存储器R2;第一NMOS管N1的源极接源线SL1、其栅极接字线WL1、其漏极接第二NMOS管N2一端的源极/漏极,第二NMOS管N2栅极接字线WL2、其另一端源极/漏极接第三NMOS管N3的漏极,第三NMOS管N3源极接源线SL2、其栅极接字线WL3;第一存储器R1一端接第一NMOS管N1和第二NMOS管N2的连接处、其另一端接位线BL1,第二存储器R2一端接第三NMOS管N3和第二NMOS管N2的连接处、其另一端接位线BL2;有效降低存储单元面积、提升阵列密度。

技术研发人员:王宗巍,杨宇航,蔡一茂,黄如

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!