比较器失调校准装置及模数转换器的制作方法

本发明涉及模拟集成电路,具体涉及一种比较器失调校准装置及模数转换器。

背景技术:

1、比较器是模数转换器(analog-to-digital converter,adc)的重要组成部分,也是电子系统中应用较为广泛的器件之一。比较器的性能,尤其是功耗,对整个模数转换器的功耗有着至关重要的影响。

2、从功耗角度,比较器可以分为静态比较器和动态比较器两种,二者的主要区别在于:静态比较器会消耗一定的静态功耗,而动态比较器的静态功耗为零,只有动态功耗。

3、动态差分比较器,属于动态比较器中较为常用的一种。动态差分比较器具有差分输入端及差分输出端,通过差分输入端可以输入差分信号,动态差分比较器可以比较所输入的差分信号之间的电压,并通过差分输出端输出差分比较结果。

4、在实际生产过程中,由于工艺和制造等问题,动态差分比较器的两差分输入端可能会存在不同程度的偏差,导致输入的差分信号不能在相同条件下进行比较,即动态差分比较器存在失调,为了保证动态差分比较器的性能,需要对动态差分比较器的失调进行校准。

5、然而,现有对动态差分比较器失调进行校准的方案,功耗较高,难以满足功耗的要求。

技术实现思路

1、本发明要解决的问题是:降低校准功耗。

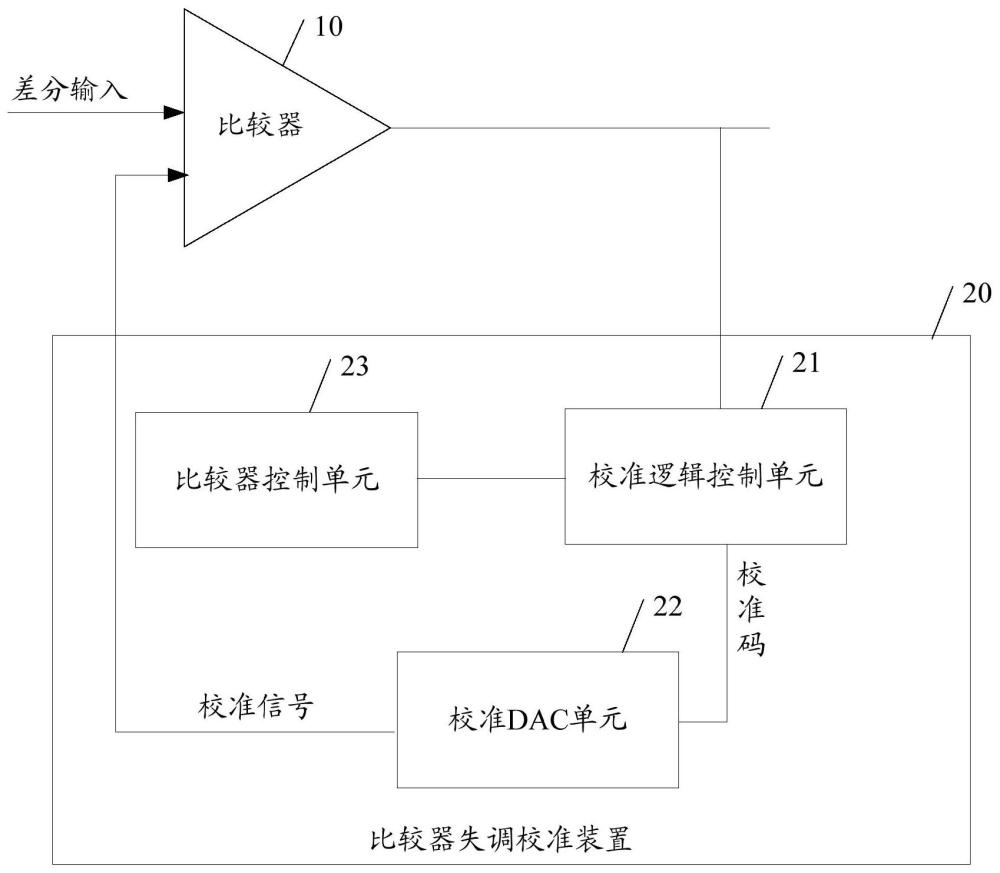

2、为解决上述问题,本发明实施例提供了一种比较器失调校准装置,用于对动态差分比较器进行失调校准;所述比较器失调校准装置包括:校准逻辑控制单元、校准dac单元及比较器控制单元;其中:所述校准逻辑控制单元,与待校准比较器连接,用于在所述待校准比较器失调时,生成校准码并存储;

3、所述校准dac单元,与所述逻辑控制单元连接,用于获取所述逻辑控制单元生成的校准码,并基于所述校准码产生校准信号,利用所述校准信号对所述待校准比较器进行校准;

4、所述比较器控制单元,与所述校准逻辑控制单元连接,用于实时检测是否满足预设校准结束条件,并在满足所述预设校准结束条件时,生成检测结果信号,以关闭所述比较器校准装置。

5、本发明实施例还提供了一种模数转换器,所述模数转换器包括上述任一种的比较器校准装置。

6、与现有技术相比,本发明实施例的技术方案具有以下优点:

7、应用本发明的方案,通过设置比较器控制单元,该比较器控制单元可以实时检测校准是否完成,进而可以在满足预设校准结束条件时,关闭所述比较器校准装置,由此可以降低所述比较器校准装置的功耗。

技术特征:

1.一种比较器失调校准装置,其特征在于,用于对动态差分比较器进行失调校准;所述比较器失调校准装置包括:校准逻辑控制单元、校准dac单元及比较器控制单元;其中:

2.如权利要求1所述的比较器失调校准装置,其特征在于,所述校准逻辑控制单元,包括:

3.如权利要求2所述的比较器失调校准装置,其特征在于,所述校准码生成电路,用于连续获取所述待校准比较器的k个差分输出结果后,并基于所述k个差分输出结果判断所述待校准比较器是否失调,以及在判定所述待校准比较器失调时,生成一对候选校准码信号;k≥2,且k为整数。

4.如权利要求3所述的比较器失调校准装置,其特征在于,所述校准码生成电路,包括:第一校准码生成子电路及第二校准码生成子电路,其中:

5.如权利要求4所述的比较器失调校准装置,其特征在于,所述第一移位寄存器及第二移位寄存器,用于在相应反相器的k个差分输出结果中,两个以上差分输出结果为高电平时,则生成高电平的候选校准码信号,否则生成低电平的候选校准码信号。

6.如权利要求3所述的比较器失调校准装置,其特征在于,所述比较器控制单元,包括:

7.如权利要求6所述的比较器失调校准装置,其特征在于,所述预设校准结束条件,包括:k个差分输出结果中,出现高电平和低电平的次数同时超过预设次。

8.如权利要求6所述的比较器失调校准装置,其特征在于,所述比较器控制单元,还包括:时钟逻辑电路及时钟产生电路;其中:

9.如权利要求8所述的比较器失调校准装置,其特征在于,所述时钟产生电路,用于在所述校准时钟信号为高电平且所述检测结果信号为低电平时,将所述内循环时钟信号与所述校准时钟信号进行叠加,得到所述待校准比较器的工作时钟信号;当所述检测结果信号为高电平时,将所述内循环时钟信号作为所述工作时钟信号;以及当所述校准时钟复位信号为高电平时,将所述校准时钟信号复位,以关闭所述待校准比较器。

10.如权利要求8所述的比较器失调校准装置,其特征在于,所述校准逻辑控制单元,还包括:

11.如权利要求10所述的比较器失调校准装置,其特征在于,所述校准启动电路,包括:

12.如权利要求3所述的比较器失调校准装置,其特征在于,所述校准码存储电路,包括:

13.如权利要求2所述的比较器失调校准装置,其特征在于,所述校准逻辑控制单元,还包括:

14.如权利要求13所述的比较器失调校准装置,其特征在于,所述存储时钟生成电路,包括:

15.如权利要求14所述的比较器失调校准装置,其特征在于,所述预设校准结束条件包括:接收到最后一位校准码存储时钟信号。

16.如权利要求1所述的比较器失调校准装置,其特征在于,所述校准dac单元,包括:

17.一种模数转换器,包括权利要求1至16任一项所述的比较器校准装置。

技术总结

一种比较器失调校准装置及模数转换器。所述比较器失调校准装置校准逻辑控制单元、校准DAC单元及比较器控制单元;其中:所述校准逻辑控制单元,与待校准比较器连接,用于在所述待校准比较器失调时,生成校准码并存储;所述校准DAC单元,与所述逻辑控制单元连接,用于获取所述逻辑控制单元生成的校准码,并基于所述校准码产生校准信号,利用所述校准信号对所述待校准比较器进行校准;所述比较器控制单元,与所述校准逻辑控制单元连接,用于实时检测是否满足预设校准结束条件,并在满足所述预设校准结束条件时,生成检测结果信号,以关闭所述比较器校准装置。采用上述方案,可以降低校准功耗。

技术研发人员:丁泽莹,吴新宇,李建忠,何蔼,王治安,李彬鸿,王云,叶甜春

受保护的技术使用者:广东省大湾区集成电路与系统应用研究院

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!