锁相环配置方法、装置、芯片及电子设备与流程

本发明实施例涉及计算机集成电路设计与制造,具体涉及一种锁相环配置方法、装置、芯片及电子设备。

背景技术:

1、pll(phase locking loop,锁相环)作为芯片内的重要模块,用于为芯片提供时钟信号。基于时钟信号为芯片运行的基础信息,因此,用于生成时钟信号的pll需要伴随着芯片的整个运行周期,即,芯片上电后即启动pll,芯片关闭时才关闭pll,相应的,pll的稳定性对芯片的稳定运行至关重要。

2、然而,在需要对pll进行参数配置时,如何在保证芯片运行稳定的前提下实现pll的参数配置,是本领域技术人员亟待解决的技术问题。

技术实现思路

1、有鉴于此,本发明实施例提供一种锁相环配置方法、装置、芯片及电子设备,在保证芯片运行稳定的前提下实现了pll的参数配置。

2、本发明实施例提供了一种锁相环配置方法,包括:

3、获取待配置至锁相环的待配置数据,其中,所述锁相环配置于芯片的全局电压域;

4、将所述待配置数据存储于锁相环参数存储部件,其中,所述锁相环参数存储部件配置于芯片的休眠电压域;

5、基于所述全局电压域的控制,执行所述锁相环的重启流程;其中,在所述锁相环的重启流程中,所述休眠电压域保持上电状态;并且,在所述锁相环的关闭流程后,启动流程前,自所述锁相环参数存储部件获取所述待配置数据,并基于所述待配置数据配置所述锁相环。

6、可选的,所述基于所述全局电压域的控制,执行所述锁相环的重启流程,包括:

7、在所述锁相环的关闭流程中,控制所述全局电压域自上电状态转换为掉电状态,以使得所述锁相环关闭;

8、在所述锁相环的启动前,控制所述全局电压域自掉电状态转换为上电状态后,执行所述自所述锁相环参数存储部件获取所述待配置数据,并基于所述待配置数据配置所述锁相环的步骤。

9、可选的,所述自所述锁相环参数存储部件获取所述待配置数据,具体为,基于总线自所述锁相环参数存储部件传输所述待配置数据,并将所述待配置数据存储至所述锁相环的配置寄存器。

10、可选的,所述自所述锁相环参数存储部件获取所述待配置数据,具体为,基于所述电压域隔离单元执行数据传输的跨电压域处理,将所述待配置数据自所述锁相环参数存储部件传输至锁相环中的配置寄存器。

11、可选的,所述基于所述待配置数据配置所述锁相环,具体为,基于所述配置寄存器中的待配置数据,配置所述锁相环。

12、可选的,所述获取待配置至锁相环的待配置数据之前,还包括:在芯片上电启动时,基于默认配置参数启动所述锁相环。

13、可选的,所述待配置参数包括参考频率、倍频因子、环带宽、锁定时间中的一项或多项。

14、本发明实施例提供了一种锁相环配置装置,包括:

15、数据获取模块,用于获取待配置至锁相环的待配置数据,其中,所述锁相环配置于芯片的全局电压域;

16、数据存储模块,用于将所述待配置数据存储于锁相环参数存储部件,其中,所述锁相环参数存储部件配置于芯片的休眠电压域;

17、数据配置模块,用于基于所述全局电压域的控制,执行所述锁相环的重启流程;其中,在所述锁相环的重启流程中,所述休眠电压域保持上电状态;并且,在所述锁相环的关闭流程后,启动流程前,自所述锁相环参数存储部件获取所述待配置数据,并基于所述待配置数据配置所述锁相环。

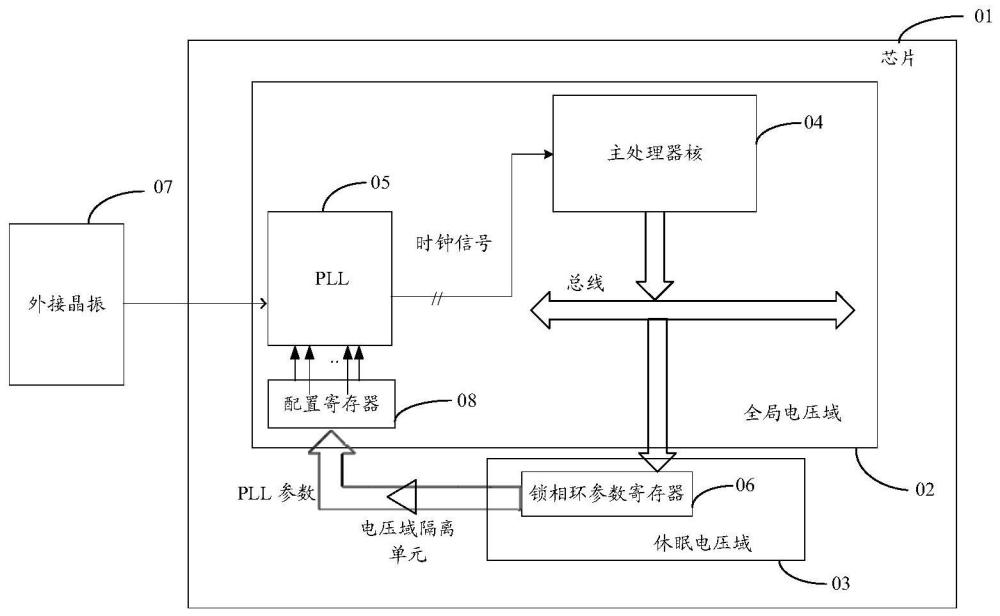

18、本发明实施例提供了一种芯片,所述芯片包括主处理器核、锁相环、锁相环参数存储部件和只读存储部件;

19、其中,所述芯片配置有全局电压域和休眠电压域;芯片中的主处理器核和锁相环配置于所述全局电压域,芯片中的锁相环参数存储部件配置于所述休眠电压域;

20、所述只读存储部件存储有程序,所述程序用于被调用以执行本发明实施例提供的锁相环配置方法。

21、可选的,所述锁相环中包括配置寄存器,所述配置寄存器在芯片上电启动前存储默认配置参数。

22、本发明实施例提供了一种电子设备,包括本发明实施例提供的芯片。

23、可选的,所述电子设备还包括外接晶振,所述外接晶振用于在芯片上电且锁相环未启动时为芯片提供参考时钟信号。

24、为实现上述目的,本发明实施例提供如下技术方案:

25、本发明实施例提供了一种锁相环配置方法、装置、芯片及电子设备,所述方法包括:获取待配置至锁相环的待配置数据,其中,所述锁相环配置于芯片的全局电压域;将所述待配置数据存储于锁相环参数存储部件,其中,所述锁相环参数存储部件配置于芯片的休眠电压域;基于所述全局电压域的控制,执行所述锁相环的重启流程;其中,在所述锁相环的重启流程中,所述休眠电压域保持上电状态;并且,在所述锁相环的关闭流程后,启动流程前,自所述锁相环参数存储部件获取所述待配置数据,并基于所述待配置数据配置所述锁相环。

26、可以看出,本发明实施例提供的锁相环配置方案,其中,所述锁相环配置于芯片的全局电压域;相应的,在锁相环的配置流程中,能够在获取锁相环的待配置数据后,将待配置数据存储于休眠电压域的锁相环参数存储部件,该休眠电压域在锁相环的重启流程中保持为上电状态,从而能够保存对应的待配置数据,进而在锁相环的重启流程中能够使得待配置数据为可获取的状态,从而可以自所述锁相环参数存储部件获取所述待配置数据,并基于所述待配置数据配置所述锁相环,实现对锁相环的参数配置。也就是说,本发明实施例中所述锁相环配置方案,可以基于芯片中全局电压域和休眠电压域的控制实现对锁相环数据的配置,从而在保证芯片运行稳定性的前提下实现pll的参数配置。

技术特征:

1.一种锁相环配置方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述基于所述全局电压域的控制,执行所述锁相环的重启流程,包括:

3.根据权利要求1所述的方法,其特征在于,所述自所述锁相环参数存储部件获取所述待配置数据,具体为,基于总线自所述锁相环参数存储部件传输所述待配置数据,并将所述待配置数据存储至所述锁相环的配置寄存器。

4.根据权利要求1所述的方法,其特征在于,所述自所述锁相环参数存储部件获取所述待配置数据,具体为,基于所述电压域隔离单元执行数据传输的跨电压域处理,将所述待配置数据自所述锁相环参数存储部件传输至锁相环中的配置寄存器。

5.根据权利要求3或4所述的方法,其特征在于,所述基于所述待配置数据配置所述锁相环,具体为,基于所述配置寄存器中的待配置数据,配置所述锁相环。

6.根据权利要求1所述的方法,其特征在于,所述获取待配置至锁相环的待配置数据之前,还包括:在芯片上电启动时,基于默认配置参数启动所述锁相环。

7.根据权利要求1所述的方法,其特征在于,所述待配置参数包括参考频率、倍频因子、环带宽、锁定时间中的一项或多项。

8.一种锁相环配置装置,其特征在于,包括:

9.一种芯片,其特征在于,所述芯片包括主处理器核、锁相环、锁相环参数存储部件和只读存储部件;

10.根据权利要求9所述的芯片,其特征在于,所述锁相环中包括配置寄存器,所述配置寄存器在芯片上电启动前存储默认配置参数。

11.一种电子设备,其特征在于,包括如权利要求9或10所述的芯片。

12.根据权利要求11所述的电子设备,其特征在于,还包括外接晶振,所述外接晶振用于在芯片上电且锁相环未启动时为芯片提供参考时钟信号。

技术总结

本发明实施例提供一种锁相环配置方法、装置、芯片及电子设备,所述方法包括:获取待配置至锁相环的待配置数据,其中,所述锁相环配置于芯片的全局电压域;将所述待配置数据存储于锁相环参数存储部件,其中,所述锁相环参数存储部件配置于芯片的休眠电压域;基于所述全局电压域的控制,执行所述锁相环的重启流程;其中,在所述锁相环的重启流程中,所述休眠电压域保持为上电状态;并且,在所述锁相环的关闭流程后,启动流程前,自所述锁相环参数存储部件获取所述待配置数据,并基于所述待配置数据配置所述锁相环。所述锁相环配置方案能够在保证芯片运行稳定性的前提下实现PLL的参数配置。

技术研发人员:张淑芬

受保护的技术使用者:海光信息技术股份有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!