一种延时可控的异步SAR型ADC时序发生电路

本发明属于集成电路,涉及一种延时可控的异步sar型adc时序发生电路。

背景技术:

1、在模拟-数字转换(adc)电路中,successive approximation register(sar)型adc是一种常见且广泛应用的技术。sar型adc以其高精度、低功耗和快速转换速度而受到青睐,特别适用于各种应用场景,如通信系统、传感器接口和嵌入式系统等。

2、高精度高速sar型adc需要很快的时钟以触发比较器进行比较,比如一个分辨率为16bit,速度为5ms/s的sar型adc,比较器需要的时钟至少为80m,如此高的频率需要消耗很大的功耗,同时在应用中难以从io输入,需要低频时钟进行相应的倍频和分频才能完成。为了避免高频时钟的需求,很多高速的比较器都采用自定时的比较器时钟,通过比较器比较完成信号做延时后再次成为比较器本身的触发信号,但是此延时的发生往往是通过延时单元实现,比如反相器链。但是在cmos工艺中,由于反相器链的延时受到温度,工艺和电源电压的影响极大,同一个延时单元在最坏和最好的情况下,其延时的变化很大,这将会极大影响比较器时钟的周期,降低sar型adc的性能。比如在典型情况下的延时设计合理,该sar型adc需要的时钟周期数与需求刚好对应,但是在温度,电压和工艺发生变化后,延时的增大将导致实际的比较周期数减小,使得某些bit位没有得到相应的比较结果;或者延时变小导致产生的时钟周期数变多,周期变短,使得可以使用的时间变短,导致电容上电压建立的时间变短,最终导致比较结果错误,降低了adc的性能。如果延时可以由adc自行控制,会根据工作环境自行调整所需要的延时,这将会使得时间得到充分的应用,极大的增强sar型adc时序的可靠性,降低adc的设计成本,提升adc的性能。

技术实现思路

1、为了解决现有技术中存在的上述技术问题,本发明提出了一种延时可控的异步sar型adc时序发生电路,可保证adc能产生合适的比较器时钟周期,同时可以充分利用转换时间,保证adc具有良好的性能,其具体技术方案如下:

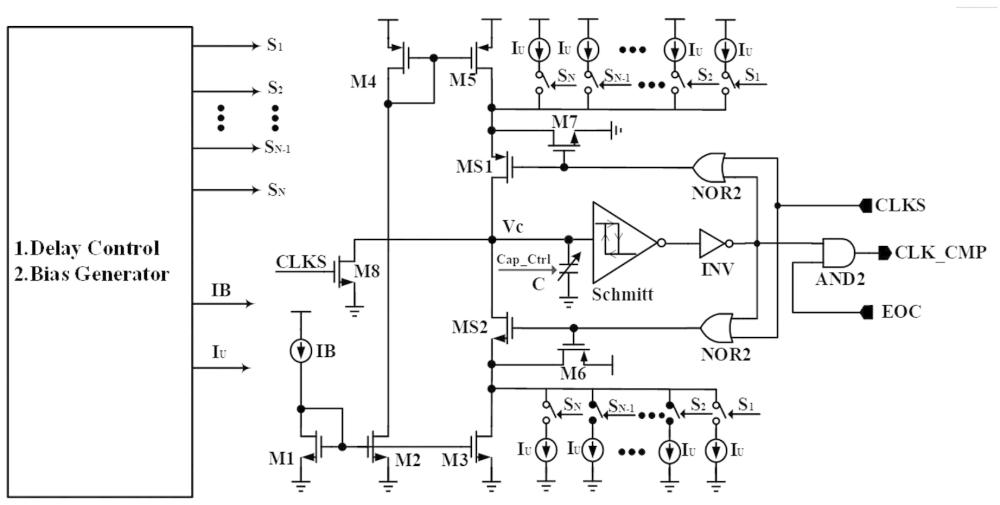

2、一种延时可控的异步sar型adc时序发生电路,包括:控制器、偏置电流产生单元、延时产生单元和时钟发生单元;所述控制器根据sar型adc比较器触发动作的要求,通过计数检测出延时大小并根据延时大小产生相应控制信号;所述偏置电流产生单元根据控制信号产生延时产生单元所需充放电电流,所述延时产生单元通过上述充放电电流对其中的电容进行充放电,或同时根据控制信号对电容大小进行调整,以产生所需电容端的电压输出模拟信号;所述时钟发生单元将所述电压输出模拟信号通过施密特触发器进行波形整形输出,并将输出结果反馈控制实现对电容的充电或放电,最终产生符合sar型adc的比较器触发动作的时钟周期。

3、进一步的,所述的控制器根据由sar型adc采样获得的时钟信号的上升沿个数是否符合sar型adc比较器触发动作的要求来判断延时的快慢,以检测出延时大小,从而根据延时大小产生相应的控制信号。

4、进一步的,所述控制器采用有限状态机,当延时过大时,则通过有限状态机切换状态来调节加大所述充放电电流的大小;当延时过小时,则通过有限状态机切换状态来调节加大电容的大小。

5、进一步的,所述偏置电流产生单元根据控制信号产生的充放电电流包括预设电流和基于预设电流等比调整的单位电流。

6、进一步的,所述偏置电流产生单元包括:运算放大器、mos管m0~mos管m6、电阻r1~电阻r3,所述mos管m1的源极与电阻r1的一端相连接,mos管m1的漏极与mos管m3的漏极、mos管m3的栅极、mos管m4的栅极、mos管m5的栅极相连接,mos管m3的源极、mos管m4的源极、mos管m5的源极均接入控制信号,mos管m4的漏极与mos管m2的漏极、mos管m2的栅极、mos管m1的栅极相连接,mos管m5的漏极与电阻r2的一端、运算放大器的同相输入端相连接,电阻r2的另一端与mos管m0的栅极、mos管m0的漏极相连接,运算放大器的反相输入端与mos管m6的源极、电阻r3的一端相连接,运算放大器的输出端与mos管m6的栅极相连接;所述电阻r1的另一端、mos管m2的源极、mos管m0的源极、电阻r3的另一端均接地。

7、进一步的,所述时钟发生单元还包括:反相器、第一或门、第二或门、与门,所述施密特触发器的输入端接所述电容的一端,电容另一端接地,施密特触发器的的输出端接反相器输入端,反相器的输出端与第一或门的第一输入端、第二或门的第一输入端、与门的第一输入端相连接,与门的第二输入端外接电源,第一或门的第二输入端与第二或门的第二输入端相连接,第一或门的输出端与第二或门的输出端分别接入延时产生单元的两个反馈控制端。

8、进一步的,所述延时产生单元为电容型dac,还包括:开关管ms1、开关管ms2、晶体管m1~晶体管m8、第一开关组和第二开关组;所述晶体管m8的栅极采样连接第一或门的第二输入端,晶体管m8的源极接地,晶体管m8的漏极与电容的一端、开关管ms1的漏极、开关管ms2的漏极相连接;开关管ms1的源极与晶体管m7的漏极、晶体管m5的漏极、第一开关组的一端相连接,所述第一开关组的一端为第一开关组中各个开关的一端并联后的连接端,所述第一开关组中各个开关的另一端则分别接入所述单位电流,开关管ms1的栅极与晶体管m7的栅极、第一或门的输出端相连接,晶体管m7的源极接地,晶体管m5的栅极与晶体管m4的栅极、晶体管m4的漏极、晶体管m2的漏极相连接,晶体管m5的源极与晶体管m4的源极分别外接接入电源信号,晶体管m2的栅极与晶体管m3的栅极、晶体管m1的栅极、晶体管m1的漏极相连接后接入所述预设电流,晶体管m3的漏极与晶体管m6的漏极、开关管ms2的源极、第二开关组的一端相连接,所述开关管ms2的栅极与晶体管m6的栅极、第二或门的输出端相连接,所述第二开关组的一端为第二开关组中各个开关的一端并联后的连接端,所述第二开关组中各个开关的另一端则分别接地,晶体管m1的源极与晶体管m2的源极、晶体管m3的源极均接地。

9、进一步的,所述第一开关组和第二开关组中的各个开关由所述控制器的有限状态机控制使能进行开闭。

10、本发明的优点:

11、1、控制逻辑简单明了,电路实现简单;

12、2、延时控制精确,可以保证时间的充分利用;

13、3、具有自适应功能,可以根据工作条件的不同进行自适应调整,具有抗工艺,电源,温度波动影响的特性。

技术特征:

1.一种延时可控的异步sar型adc时序发生电路,其特征在于,包括:控制器、偏置电流产生单元、延时产生单元和时钟发生单元;所述控制器根据sar型adc比较器触发动作的要求,通过计数检测出延时大小并根据延时大小产生相应控制信号;所述偏置电流产生单元根据控制信号产生延时产生单元所需充放电电流,所述延时产生单元通过上述充放电电流对其中的电容进行充放电,或同时根据控制信号对电容大小进行调整,以产生所需电容端的电压输出模拟信号;所述时钟发生单元将所述电压输出模拟信号通过施密特触发器进行波形整形输出,并将输出结果反馈控制实现对电容的充电或放电,最终产生符合sar型adc的比较器触发动作的时钟周期。

2.如权利要求1所述的一种延时可控的异步sar型adc时序发生电路,其特征在于,所述的控制器根据由sar型adc采样获得的时钟信号的上升沿个数是否符合sar型adc比较器触发动作的要求来判断延时的快慢,以检测出延时大小,从而根据延时大小产生相应的控制信号。

3.如权利要求2所述的一种延时可控的异步sar型adc时序发生电路,其特征在于,所述控制器采用有限状态机,当延时过大时,则通过有限状态机切换状态来调节加大所述充放电电流的大小;当延时过小时,则通过有限状态机切换状态来调节加大电容的大小。

4.如权利要求3所述的一种延时可控的异步sar型adc时序发生电路,其特征在于,所述偏置电流产生单元根据控制信号产生的充放电电流包括预设电流和基于预设电流等比调整的单位电流。

5.如权利要求4所述的一种延时可控的异步sar型adc时序发生电路,其特征在于,所述偏置电流产生单元包括:运算放大器、mos管m0~mos管m6、电阻r1~电阻r3,所述mos管m1的源极与电阻r1的一端相连接,mos管m1的漏极与mos管m3的漏极、mos管m3的栅极、mos管m4的栅极、mos管m5的栅极相连接,mos管m3的源极、mos管m4的源极、mos管m5的源极均接入控制信号,mos管m4的漏极与mos管m2的漏极、mos管m2的栅极、mos管m1的栅极相连接,mos管m5的漏极与电阻r2的一端、运算放大器的同相输入端相连接,电阻r2的另一端与mos管m0的栅极、mos管m0的漏极相连接,运算放大器的反相输入端与mos管m6的源极、电阻r3的一端相连接,运算放大器的输出端与mos管m6的栅极相连接;所述电阻r1的另一端、mos管m2的源极、mos管m0的源极、电阻r3的另一端均接地。

6.如权利要求4所述的一种延时可控的异步sar型adc时序发生电路,其特征在于,所述时钟发生单元还包括:反相器、第一或门、第二或门、与门,所述施密特触发器的输入端接所述电容的一端,电容另一端接地,施密特触发器的的输出端接反相器输入端,反相器的输出端与第一或门的第一输入端、第二或门的第一输入端、与门的第一输入端相连接,与门的第二输入端外接电源,第一或门的第二输入端与第二或门的第二输入端相连接,第一或门的输出端与第二或门的输出端分别接入延时产生单元的两个反馈控制端。

7.如权利要求6所述的一种延时可控的异步sar型adc时序发生电路,其特征在于,所述延时产生单元为电容型dac,还包括:开关管ms1、开关管ms2、晶体管m1~晶体管m8、第一开关组和第二开关组;所述晶体管m8的栅极采样连接第一或门的第二输入端,晶体管m8的源极接地,晶体管m8的漏极与电容的一端、开关管ms1的漏极、开关管ms2的漏极相连接;开关管ms1的源极与晶体管m7的漏极、晶体管m5的漏极、第一开关组的一端相连接,所述第一开关组的一端为第一开关组中各个开关的一端并联后的连接端,所述第一开关组中各个开关的另一端则分别接入所述单位电流,开关管ms1的栅极与晶体管m7的栅极、第一或门的输出端相连接,晶体管m7的源极接地,晶体管m5的栅极与晶体管m4的栅极、晶体管m4的漏极、晶体管m2的漏极相连接,晶体管m5的源极与晶体管m4的源极分别外接接入电源信号,晶体管m2的栅极与晶体管m3的栅极、晶体管m1的栅极、晶体管m1的漏极相连接后接入所述预设电流,晶体管m3的漏极与晶体管m6的漏极、开关管ms2的源极、第二开关组的一端相连接,所述开关管ms2的栅极与晶体管m6的栅极、第二或门的输出端相连接,所述第二开关组的一端为第二开关组中各个开关的一端并联后的连接端,所述第二开关组中各个开关的另一端则分别接地,晶体管m1的源极与晶体管m2的源极、晶体管m3的源极均接地。

8.如权利要求7所述的一种延时可控的异步sar型adc时序发生电路,其特征在于,所述第一开关组和第二开关组中的各个开关由所述控制器的有限状态机控制使能进行开闭。

技术总结

本发明属于集成电路技术领域,涉及一种延时可控的异步SAR型ADC时序发生电路,包括:控制器、偏置电流产生单元、延时产生单元和时钟发生单元;所述控制器根据比较器触发动作的要求,通过计数检测出延时大小并产生相应控制信号;所述偏置电流产生单元根据控制信号产生延时产生单元所需的充放电电流,所述延时产生单元采用电容型DAC,产生所需的电容电压输出模拟信号;所述时钟发生单元将电压输出模拟信号通过施密特触发器进行波形整形输出,并将输出结果反馈以控制电容的充电或放电,最终产生符合比较器触发动作要求的时钟周期。本发明延时控制精确,可以保证时间的充分利用,具有自适应功能,以及抗工艺、电源、温度波动影响的特性。

技术研发人员:黄凯,王玉磊,郑丹丹,蒋小文

受保护的技术使用者:浙江大学

技术研发日:

技术公布日:2024/5/8

- 还没有人留言评论。精彩留言会获得点赞!