一种二分频电路及集成电路的制作方法

本发明属于集成电路设计,特别涉及一种模拟的二分频电路及集成电路。

背景技术:

1、常见的高速二分频器使用tspc(true single phase clock,真单相时钟分频器)、cml(current mode logic,电流模逻辑)等电路实现高速时钟的分频。tspc电路,器件数量少,可实现较小的芯片面积,采用预充电设计可达到很高的工作速度,但是由于采用单相时钟,抗噪声性能也不好。cml分频器基于全差分源极耦合电路设计,通过改变前后级的触发-锁存状态实现二分频,但其管子尺寸一般较大,并且需要尾部偏置电流的设计,进一步增加了面积。而普通的锁存结构的分频器由于电路结构会产生竞争冒险现象,在高频下并不适用。

2、如何在集成电路设计中提供一种简便高速的二分频电路是目前亟待解决的一个问题。

技术实现思路

1、有鉴于此,本发明提供了一种二分频电路及集成电路用于解决现有技术的不足。

2、为达到上述目的,本发明采用如下技术方案:

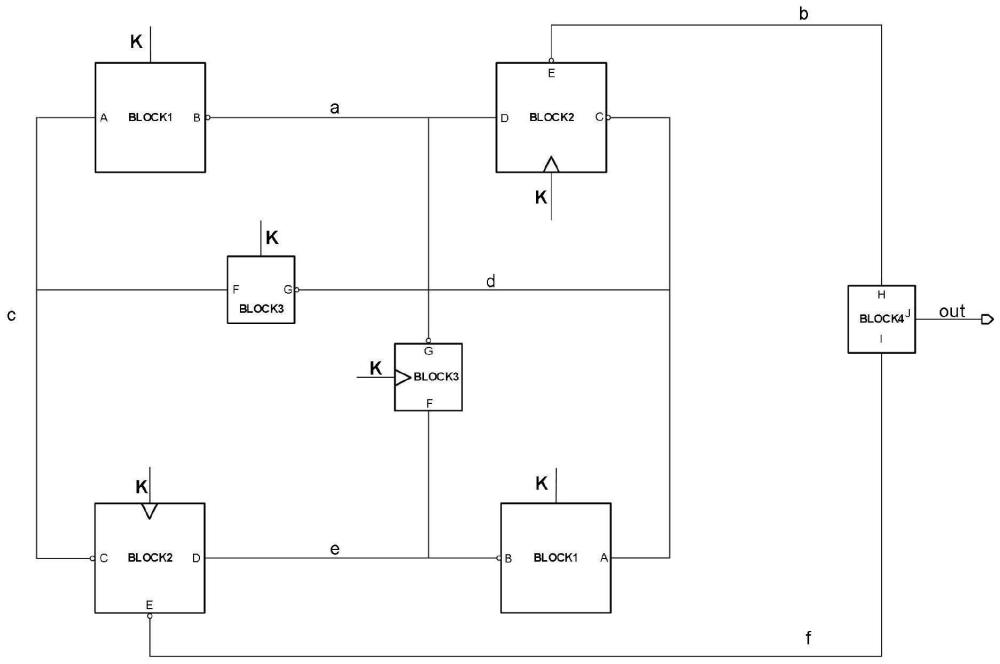

3、本发明实施例提供了一种二分频电路,包括:两个第一逻辑控制单元、两个第二逻辑控制单元、两个控制端使能电平不同的电平保持与开关切换单元和一个逻辑综合输出驱动单元;

4、所述第一逻辑控制单元为三端abk结构,a端为输入,b端为输出,k端为控制端;当k为低电平时,将b端从电路中断开,k为高电平时,将b端接入电路,并有逻辑关系b=~a;

5、所述第二逻辑控制单元为四端cdek结构,d端为输入,c端与e端为输出,k端为控制端;当k为低电平时,将c端接入电路,并有逻辑关系c=e=~d;当k为高电平时,将c端从电路中断开,并有逻辑关系e=~d;

6、所述电平保持与开关切换单元为三端fgk结构,g端与f端互为输入输出,k端为控制端;当k输入为使能电平信号时,将g与f端接入电路,并有逻辑关系g=~f;当k为非使能电平信号时,将g与f端从电路中断开;

7、所述逻辑综合输出驱动单元为三端hij结构,h端和i端为输入,j端为输出,并有逻辑关系j=~h=i;并增加输出的驱动能力;

8、第一个第一逻辑控制单元的b端连接第一个第二逻辑控制单元的d端和第一个电平保持与开关切换单元的g端,第一个第二逻辑控制单元的c端连接第二个第一逻辑控制单元的a端和和第二个电平保持与开关切换单元的g端,第二个第一逻辑控制单元的b端连接第二个第二逻辑控制单元的d端和和第一个电平保持与开关切换单元的f端,第二个第二逻辑控制单元的c端连接第一个第一逻辑控制单元的a端和第二个电平保持与开关切换单元的f端;第一个第二逻辑控制单元的e端和第二个第二逻辑控制单元的e端分别连接所述逻辑综合输出驱动单元的两输入端;所有的控制端k端均连接时钟信号;

9、所述两个电平保持与开关切换单元的控制端使能电平信号相反,使在任一时刻只有一个电平保持与开关切换单元接入电路生效;

10、所述逻辑综合输出驱动单元输出的信号为时钟信号的二分频信号。

11、进一步地,所述第一逻辑控制单元包括:反相器和电平控制开关;所述反相器的输出端连接所述电平控制开关的输入端;所述反相器的输入端作为输入a端;所述电平控制开关的输出端作为输出b端;所述电平控制开关的电平控制端作为k端;所述电平控制开关在高电平时导通,低电平时断开。

12、进一步地,所述第二逻辑控制单元包括:反相器和电平控制开关;所述反相器的输出端连接所述电平控制开关的输入端;所述反相器的输入端作为输入d端;所述反相器的输出端作为输出e端;所述电平控制开关的输出端作为输出c端;所述电平控制开关的电平控制端作为k端;所述电平控制开关在高电平时断开,低电平时导通。

13、进一步地,所述电平控制开关为传输门。

14、进一步地,所述逻辑综合输出驱动单元包括:第一反相器、第二反相器、第三反相器、第四反相器、第五反相器;所述第一反相器的输入端和所述第二反相器的输入端作为逻辑综合输出驱动单元的两输入端;所述第一反相器的输出端与第三反相器的输出端、第四反相器的输入端、第五反相器的输入端均相连;所述第二反相器的输出端与第三反相器的输入端、第四反相器的输出端均相连;所述第五反相器的输出端作为逻辑综合输出驱动单元的二倍频信号输出端。

15、进一步地,所述电平保持与开关切换单元采用可控锁存器电路实现。

16、进一步地,所述电平保持与开关切换单元包括:第一mos管、第二mos管、第三mos管、第四mos管、第五mos管、第六mos管和传输门;第一mos管的漏极、第二mos管的漏极、第三mos管的栅极、第四mos管的栅极均与传输门的一端相连作为电平保持与开关切换单元的一输入/输出端;第一mos管的栅极、第二mos管的栅极、第三mos管的漏极、第四mos管的漏极均与传输门的另一端相连作为电平保持与开关切换单元的另一输入/输出端;第一mos管的源极、第三mos管的源极均与第五mos管的漏极相连;第二mos管的源极、第四mos管的源极均与第六mos管的漏极相连;第五mos管的源极接电源;第六mos管的源极接地;第五mos管的栅极和第六mos管的栅极作为电平保持与开关切换单元的控制端。

17、进一步地,所述电平保持与开关切换单元还包括:第七mos管和第八mos管;第七mos管的漏极连接第五mos管的源极;第七mos管的源极接电源;第八mos管的漏极连接第六mos管的源极;第八mos管的源极接地;第七mos管的栅极和第八mos管的栅极作为复位端。

18、进一步地,所述二分频电路还包括:两个电平复位单元;每个复位单元用于对第一逻辑控制单元输出b端和第二逻辑控制单元输入d端连接处的电平进行预设电平复位操作;所述两个电平复位单元复位的电平相反

19、进一步地,所述电平保持与开关切换单元还包括复位端,当复位端执行复位操作,所述电平保持与开关切换单元的输入输出两端的电平设置为相反的预设电平值。

20、本发明实施例还提供了一种集成电路,所述集成电路使用以上所述的二分频电路。

21、本发明提供的二分频电路通过改变前后级电路的状态,可有效减少竞争冒险现象,并减少信号到输出的传输延时,实现高速分频。具有结构简单,速度快的优点。

技术特征:

1.一种二分频电路,其特征在于,包括:两个第一逻辑控制单元、两个第二逻辑控制单元、两个控制端使能电平不同的电平保持与开关切换单元和一个逻辑综合输出驱动单元;

2.根据权利要求1所述的二分频电路,其特征在于,所述第一逻辑控制单元包括:反相器和电平控制开关;所述反相器的输出端连接所述电平控制开关的输入端;所述反相器的输入端作为输入a端;所述电平控制开关的输出端作为输出b端;所述电平控制开关的电平控制端作为k端;所述电平控制开关在高电平时导通,低电平时断开。

3.根据权利要求1所述的二分频电路,其特征在于,所述第二逻辑控制单元包括:反相器和电平控制开关;所述反相器的输出端连接所述电平控制开关的输入端;所述反相器的输入端作为输入d端;所述反相器的输出端作为输出e端;所述电平控制开关的输出端作为输出c端;所述电平控制开关的电平控制端作为k端;所述电平控制开关在高电平时断开,低电平时导通。

4.根据权利要求2或3任一所述的二分频电路,其特征在于,所述电平控制开关为传输门。

5.根据权利要求1所述的二分频电路,其特征在于,所述逻辑综合输出驱动单元包括:第一反相器、第二反相器、第三反相器、第四反相器、第五反相器;所述第一反相器的输入端和所述第二反相器的输入端作为逻辑综合输出驱动单元的两输入端;所述第一反相器的输出端与第三反相器的输出端、第四反相器的输入端、第五反相器的输入端均相连;所述第二反相器的输出端与第三反相器的输入端、第四反相器的输出端均相连;所述第五反相器的输出端作为逻辑综合输出驱动单元的二倍频信号输出端。

6.根据权利要求1所述的二分频电路,其特征在于,所述电平保持与开关切换单元采用可控锁存器电路实现。

7.根据权利要求1所述的二分频电路,其特征在于,所述电平保持与开关切换单元包括:第一mos管、第二mos管、第三mos管、第四mos管、第五mos管、第六mos管和传输门;第一mos管的漏极、第二mos管的漏极、第三mos管的栅极、第四mos管的栅极均与传输门的一端相连作为电平保持与开关切换单元的一输入/输出端;第一mos管的栅极、第二mos管的栅极、第三mos管的漏极、第四mos管的漏极均与传输门的另一端相连作为电平保持与开关切换单元的另一输入/输出端;第一mos管的源极、第三mos管的源极均与第五mos管的漏极相连;第二mos管的源极、第四mos管的源极均与第六mos管的漏极相连;第五mos管的源极接电源;第六mos管的源极接地;第五mos管的栅极和第六mos管的栅极作为电平保持与开关切换单元的控制端。

8.根据权利要求7所述的二分频电路,其特征在于,所述电平保持与开关切换单元还包括:第七mos管和第八mos管;第七mos管的漏极连接第五mos管的源极;第七mos管的源极接电源;第八mos管的漏极连接第六mos管的源极;第八mos管的源极接地;第七mos管的栅极和第八mos管的栅极作为复位端。

9.根据权利要求1所述的二分频电路,其特征在于,所述二分频电路还包括:两个电平复位单元;每个复位单元用于对第一逻辑控制单元输出b端和第二逻辑控制单元输入d端连接处的电平进行预设电平复位操作;所述两个电平复位单元复位的电平相反。

10.一种集成电路,其特征在于,使用权利要求1-9任一所述的二分频电路。

技术总结

本发明提供了一种二分频电路,该电路包括:两个第一逻辑控制单元、两个第二逻辑控制单元、两个控制端使能电平不同的电平保持与开关切换单元和一个逻辑综合输出驱动单元。该二分频电路通过改变前后级电路的状态,可有效减少竞争冒险现象,并减少信号到输出的传输延时,实现高速分频。具有结构简单,速度快的优点。

技术研发人员:翟云鹏,王雅君

受保护的技术使用者:深圳开阳电子股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!