本技术涉及tr组件领域,尤其是涉及一种砖式小型化tr组件的夹层馈电结构。

背景技术:

1、近几年国内的雷达技术发展迅速,雷达体积也是越来越小,特别是随着相控阵雷达的发展,射频通道数量越来越多,因此单个tr组件所集成的通道数也越来越多。

2、相控阵雷达的射频前端是由若干个辐射单元及对应的tr通道所构成,各单元之间的辐射能量和相位是可以控制的,雷达通过调整各个通道的相位实现波束扫描和波束赋形。相控阵雷达具有体积小、波束指向灵活、抗干扰能力强等优点。但由于需要对每个通道进行移相、衰减及开关等控制,且通道多、功率大,因此导致相控阵雷达的tr组件设备复杂,造价昂贵。

3、目前主流tr组件分为砖式和瓦片式两种结构,其中瓦片式的馈电技术对芯片的集成性和工艺要求高,成本高;而传统的砖式结构尺寸又难以缩小;采用多层ltcc基板的方式成本又过于高昂。目前砖式tr组件的腔体包括正反两面,其中正面为射频面,包括放大、开关、移相、衰减等芯片;背面为电源及控制印制板,为射频芯片提供所需的电源及控制信号;为了保证射频面的气密,通常采用玻璃绝缘子烧结的方式将供电及控制信号引入腔体正面的芯片处进行馈电。针对通道多、控制信号多的tr组件,采用该方式所需要的绝缘子数量多、导致tr组件体积大、成本高。

技术实现思路

1、本实用新型的目的在于,提供一种砖式小型化tr组件的夹层馈电结构,解决传统砖式tr组件的体积问题和瓦片式tr组件的成本高、工艺难度大的问题,实现tr组件的小型化,同时保证指标。

2、本实用新型的发明目的通过以下技术方案来实现:

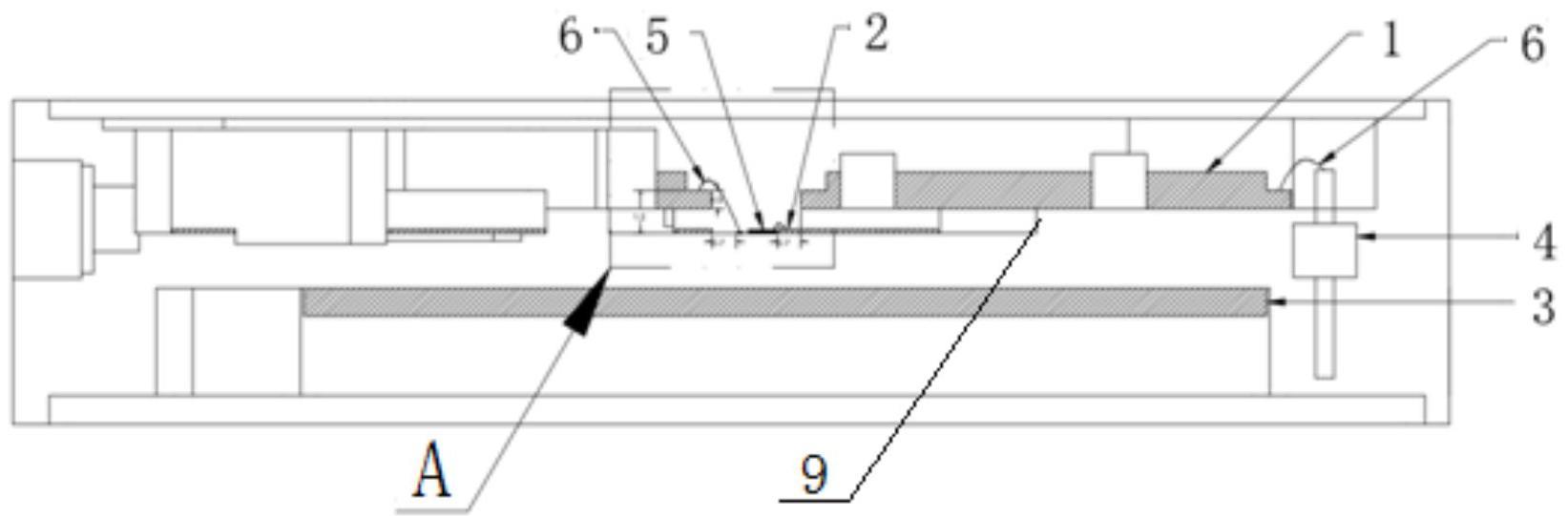

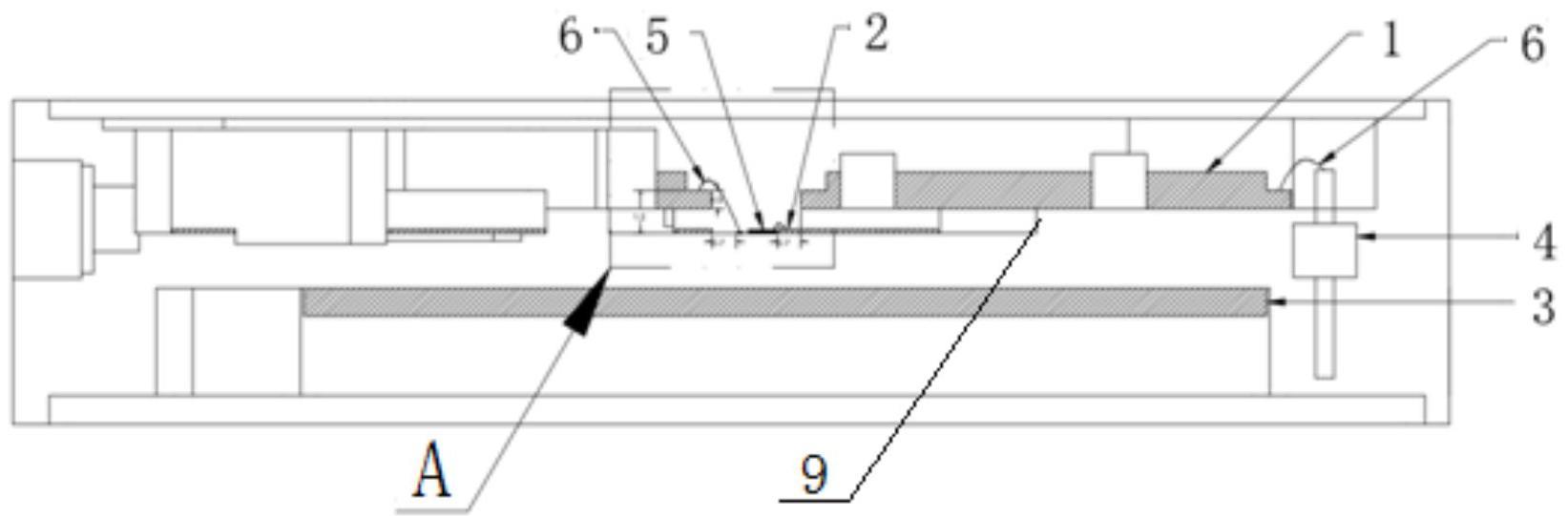

3、一种砖式小型化tr组件的夹层馈电结构,该结构包括正面腔体和背面腔体,所述正面腔体底部设置射频微带板和芯片,正面腔体内设置具有一定高度的夹层台阶,该夹层台阶上安装有多层分线印制板,该多层分线印制板在芯片对应位置处开窗,所述背面腔体内安装有电源及控制印制板,电源及控制印制板通过玻璃绝缘子将芯片所需要的电源和控制信号引入正面腔体内的多层分线印制板,多层分线印制板位于开窗位置的焊盘与芯片进行键合,进而对芯片进行馈电。

4、作为进一步的技术方案,所述玻璃绝缘子通过焊锡烧结在馈电结构内,电源及控制印制板的焊盘输出点与玻璃绝缘子进行焊接,多层分线印制板上的输入焊盘与玻璃绝缘子进行键合。

5、作为进一步的技术方案,所述多层分线印制板上的输入焊盘位于多层分线印制板的中间层,输入焊盘裸露在外并距离多层分线印制板的底层0.1mm~1mm。

6、作为进一步的技术方案,输入焊盘距离多层分线印制板的底层0.1mm~0.5mm。

7、作为进一步的技术方案,夹层台阶的高度为0.7mm~2mm。

8、作为进一步的技术方案,夹层台阶的高度为0.7mm。

9、作为进一步的技术方案,开窗尺寸比芯片边缘大0.6mm~2mm。

10、作为进一步的技术方案,开窗尺寸比芯片边缘大0.7mm。

11、作为进一步的技术方案,多层分线印制板位于开窗位置的焊盘与芯片通过金丝进行键合,多层分线印制板上的输入焊盘与玻璃绝缘子通过金丝进行键合。

12、与现有技术相比,本实用新型在射频面增加夹层,采用印制板馈电的方式,其能够解决采用多层ltcc基板进行馈电和射频传输而带来的成本高昂的问题,又能解决传统玻璃绝缘子馈电带来的体积大的问题,不仅既能减少绝缘子数量,又能将电源及控制信号引至芯片处,实现了产品的小型化、降低了成本。

技术特征:1.一种砖式小型化tr组件的夹层馈电结构,其特征在于,该结构包括正面腔体和背面腔体,所述正面腔体底部设置射频微带板和芯片,正面腔体内设置具有一定高度的夹层台阶,该夹层台阶上安装有多层分线印制板,该多层分线印制板在芯片对应位置处开窗,所述背面腔体内安装有电源及控制印制板,电源及控制印制板通过玻璃绝缘子将芯片所需要的电源和控制信号引入正面腔体内的多层分线印制板,多层分线印制板位于开窗位置的焊盘与芯片进行键合,进而对芯片进行馈电。

2.根据权利要求1所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,所述玻璃绝缘子通过焊锡烧结在馈电结构内,电源及控制印制板的焊盘输出点与玻璃绝缘子进行焊接,多层分线印制板上的输入焊盘与玻璃绝缘子进行键合。

3.根据权利要求2所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,所述多层分线印制板上的输入焊盘位于多层分线印制板的中间层,输入焊盘裸露在外并距离多层分线印制板的底层0.1mm~1mm。

4.根据权利要求3所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,输入焊盘距离多层分线印制板的底层0.1mm~0.5mm。

5.根据权利要求1所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,夹层台阶的高度为0.7mm~2mm。

6.根据权利要求5所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,夹层台阶的高度为0.7mm。

7.根据权利要求1所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,开窗尺寸比芯片边缘大0.6mm~2mm。

8.根据权利要求7所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,开窗尺寸比芯片边缘大0.7mm。

9.根据权利要求2所述的一种砖式小型化tr组件的夹层馈电结构,其特征在于,多层分线印制板位于开窗位置的焊盘与芯片通过金丝进行键合,多层分线印制板上的输入焊盘与玻璃绝缘子通过金丝进行键合。

技术总结本技术提供一种砖式小型化TR组件的夹层馈电结构,该结构包括正面腔体和背面腔体,所述正面腔体底部设置射频微带板和芯片,正面腔体内设置具有一定高度的夹层台阶,该夹层台阶上安装有多层分线印制板,该多层分线印制板在芯片对应位置处开窗,所述背面腔体内安装有电源及控制印制板,电源及控制印制板通过玻璃绝缘子将芯片所需要的电源和控制信号引入正面腔体内的多层分线印制板,多层分线印制板位于开窗位置的焊盘与芯片进行键合,进而对芯片进行馈电。本技术在射频面增加夹层,采用印制板馈电的方式,既能减少绝缘子数量、又能将电源及控制信号引至芯片处。

技术研发人员:马莞迪

受保护的技术使用者:成都辰天信息科技有限公司

技术研发日:20230307

技术公布日:2024/1/15