一种延时装置的制作方法

本技术涉及一种集成电路,具体涉及一种延时装置。

背景技术:

1、在芯片处理工作中通常需要对信号做延时处理,进而为了实现延时目的,集成电路设计过程中通常会设置有较多的延时电路,通过对电路中元器件的控制以使得芯片对产生的模拟信号和数字信号进行延时处理,从而控制电路的动作时间,同时延时电路也能保证芯片的稳定性和可靠性,避免了噪声信号对芯片的干扰。

2、现有的设计中通常普遍采用的延时电路为rc延时电路,rc延时电路的设计结构相对结构简单,但是存在精度不高的缺点、噪声大频率调节不方便,且由于没有负反馈进而导致延时输出幅度不够稳定,并且延时时间有限,要得到较长时间的延时需要面积较大的电容,会浪费大量面积从而提高成本。

技术实现思路

1、对现有技术的不足,本实用新型提供一种延时装置,具体地:

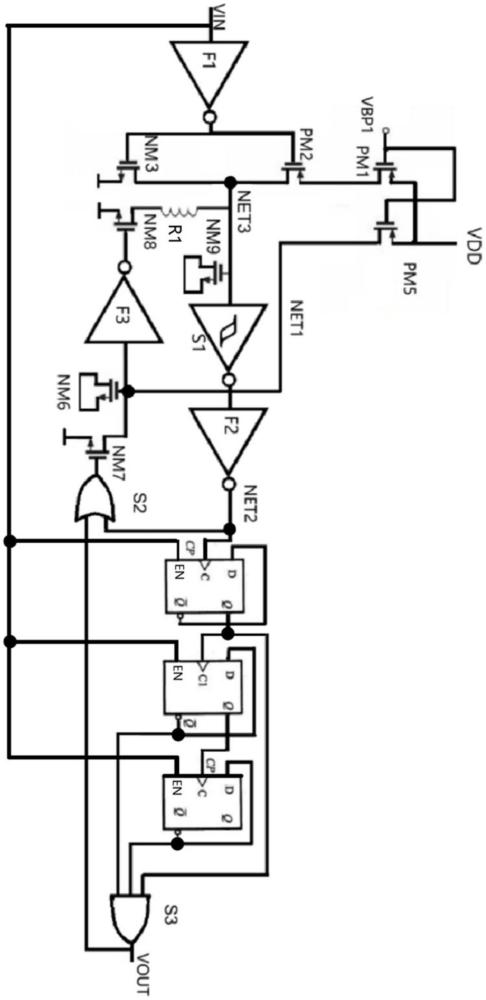

2、一方面,本实用新型提供一种延时装置,其中:包括,

3、第二电流源,输入端连接电源端,控制端连接外部偏置信号;

4、第一电流源,输入端连接所述第二电流源的输入端,控制端连接外部偏置信号;

5、第一子控制器,输入端连接所述第一电流源的输出端,控制端连接一外部信号处理装置的输出端;

6、第一储能单元,输入端分别连接所述第二电流源的输出端、第三反相器的输入端;

7、第二储能单元,分别连接所述第一子控制器的输出端、分频器的输入端;

8、第二子控制器,输入端连接所述第一子控制器的输出端,控制端连接所述第三反相器的输出端,输出端接地;

9、第一处理单元,第一输入端连接所述第二储能单元,第二输入端连接第二处理单元的输出端,输出端连接第三子控制器的控制端;

10、其中所述第二处理单元的输入端连接所述分频器的输出端,并根据接收的输入信号形成一输出信号输出。

11、优选地,上述的一种延时装置,其中:所述外部信号处理装置包括第一反相器,所述第一反相器的输入端用以接收外部输入信号,对所述外部输入信号做反相处理并输出。

12、优选地,上述的一种延时装置,其中:所述分频器由至少一个d触发器形成,所述d触发器的输出端连接所述第二处理单元的输入端。

13、优选地,上述的一种延时装置,其中:还包括第一稳定单元,所述第一稳定单元连接于所述第二储能单元与所述分频器之间,所述第一稳定单元由施密特触发器和第二反相器形成,所述施密特触发器的输入端连接所述第二储能单元,输出端连接所述第二反相器的输入端,所述第二反相器的输出端连接所述分频器。

14、优选地,上述的一种延时装置,其中:还包括第二稳定单元,所述第二稳定单元由电阻形成,所述电阻连接于所述第二储能单元与第二子控制器的控制端之间。

15、优选地,上述的一种延时装置,其中:所述第一处理单元由或门电路形成。

16、优选地,上述的一种延时装置,其中:所述第二处理单元由与门电路形成。

17、优选地,上述的一种延时装置,其中:所述第一储能单元、和/或所述第二储能单元由nmos管形成。

18、优选地,上述的一种延时装置,其中:所述第二电流源、或第一电流源、或第一子控制器由pmos管形成。

19、优选地,上述的一种延时装置,其中:还包括第四子控制器,所述第四子控制器的控制端连接所述外部信号处理装置,输入端连接所述第一子控制器的输出端,输出端接地。

20、与现有技术相比,本实用新型提供的有益效果是:旨在实现毫秒级别的延时情况下,通过d触发器的分频确立形成相对较多的延时周期数量,另外可通过调节电容容值大小对延时时间进行微调,相较于普通rc电路节省了大量电容面积。再者该电路可通过增减d触发器的个数对延时时间长短进行灵活调整,电路加入了反馈机制(将第二处理单元的输出信号作为第一处理单元的输入),使得该延时输出幅度稳定。并且该延时电路还具有低功耗的优点。

技术特征:

1.一种延时装置,其特征在于:包括,

2.根据权利要求1所述的一种延时装置,其特征在于:所述外部信号处理装置包括第一反相器,所述第一反相器的输入端用以接收外部输入信号,对所述外部输入信号做反相处理并输出。

3.根据权利要求1所述的一种延时装置,其特征在于:所述分频器由至少一个d触发器形成,所述d触发器的输出端连接所述第二处理单元的输入端。

4.根据权利要求1所述的一种延时装置,其特征在于:还包括第一稳定单元,所述第一稳定单元连接于所述第二储能单元与所述分频器之间,所述第一稳定单元由施密特触发器和第二反相器形成,所述施密特触发器的输入端连接所述第二储能单元,输出端连接所述第二反相器的输入端,所述第二反相器的输出端连接所述分频器。

5.根据权利要求1所述的一种延时装置,其特征在于:还包括第二稳定单元,所述第二稳定单元由电阻形成,所述电阻连接于所述第二储能单元与第二子控制器的控制端之间。

6.根据权利要求1所述的一种延时装置,其特征在于:所述第一处理单元由或门电路形成。

7.根据权利要求1所述的一种延时装置,其特征在于:所述第二处理单元由与门电路形成。

8.根据权利要求1所述的一种延时装置,其特征在于:所述第一储能单元、和/或所述第二储能单元由nmos管形成。

9.根据权利要求1所述的一种延时装置,其特征在于:所述第二电流源、或第一电流源、或第一子控制器由pmos管形成。

10.根据权利要求1所述的一种延时装置,其特征在于:还包括第四子控制器,所述第四子控制器的控制端连接所述外部信号处理装置,输入端连接所述第一子控制器的输出端,输出端接地。

技术总结

本技术涉及一种集成电路技术领域,具体涉及一种延时装置,包括,第二电流源,控制端连接外部偏置信号;第一电流源,输入端连接第二电流源的输入端,控制端连接外部偏置信号;第一子控制器,输入端连接第一电流源的输出端,控制端连接一外部信号处理装置的输出端;第一储能单元,连接第二电流源;第二储能单元,连接第一子控制器;第二子控制器,连接第一子控制器的输出端,控制端连接第三反相器的输出端;第一处理单元,第一输入端连接第二储能单元,第二输入端连接第二处理单元的输出端,输出端连接第三子控制器的控制端,其中第二处理单元的输入端连接分频器的输出端,并根据接收的输入信号形成一输出信号输出。

技术研发人员:张正旭

受保护的技术使用者:芯弘微电子(深圳)有限公司

技术研发日:20230912

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!