用于GAACMOS技术的集成应变SiGe沟道PMOS的制作方法

本公开内容的实施方式通常涉及半导体器件,并且更特定而言,涉及水平环栅(gate all around)器件结构以及用于形成水平环栅器件结构的方法及设备。

背景技术:

1、晶体管是大部分集成电路的关键部件。由于晶体管的驱动电流及由此速度与晶体管的栅极宽度成比例,较快的晶体管通常需要较大的栅极宽度。因此,在晶体管尺寸与速度之间存在折衷,并且已经开发“鳍式”场效晶体管(finfet)来解决具有最大驱动电流及最小尺寸的晶体管的冲突目标。finfet的特征在于鳍形沟道区域,该鳍形沟道区域大幅度增加晶体管的尺寸但不显著增加晶体管的占据面积,并且finfft目前在众多集成电路中应用。然而,finfet具有其自身的缺陷。

2、随着晶体管器件的特征尺寸持续缩小以实现更大电路密度及更高性能,需要改良晶体管器件结构以改进静电耦合并且减少副作用,诸如寄生电容及断开状态泄漏。晶体管器件结构的示例包括平面结构、鳍式场效应晶体管(finfet)结构、及水平环栅(hgaa)结构。hgaa器件结构包括以堆叠配置悬挂并且通过源极/漏极区域连接的若干晶格匹配沟道。发明人相信,hgaa结构提供了良好的静电控制并且可以在互补金属氧化物半导体(cmos)晶片制造中发现广泛采用。

3、逻辑栅极性能涉及所使用的材料的特性以及结构层的厚度及面积。然而,随着一些栅极特性经调节以适应器件缩放,出现了挑战。此外,在水平环栅(hgaa)器件上的布线之间的空间局限限制了i/o晶体管的栅极介电材料的厚度。

4、用于环栅(gaa)p型场效应晶体管(pfet)处理的p型源极/漏极锗硅(sige)外延(epi)的严重错位是保持沟道中的压应力以提升器件性能的最大瓶颈之一。为pmos集成sige沟道同时保持si沟道亦具有挑战性。

5、由此,需要用于形成pmos电子器件的改进方法。

技术实现思路

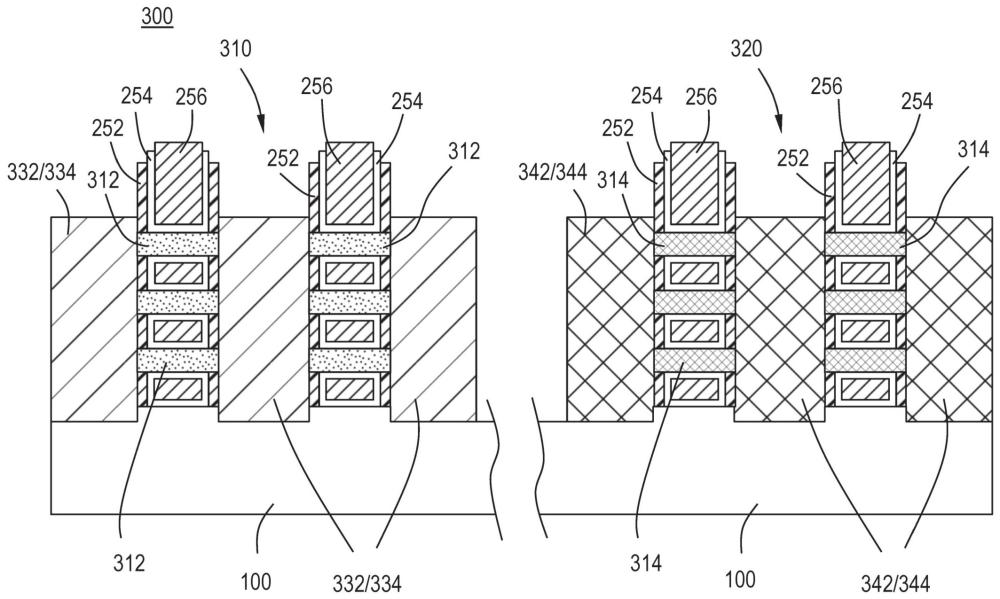

1、本案的一个或多个实施方式涉及形成半导体器件的方法。基板上的超晶格结构被选择性地蚀刻。超晶格结构包含交替布置为多个堆叠对的第一材料的多个第一层及第二材料的对应多个第二层,用于移除第二层的每一者以在超晶格结构及多个纳米薄片中形成多个空隙,这些纳米薄片包含在源极区域与漏极区域之间延伸的第一层。包覆材料在纳米薄片的多个第一层的每一者周围形成以形成具有第一材料的纳米薄片,其中包覆材料围绕第一材料。纳米薄片被干式氧化以将纳米薄片转化为具有由第一材料的氧化物围绕的包覆材料。第一材料被移除以留下包覆材料的纳米片。

2、一种电子器件包含:pmos,其包含在源极区域与漏极区域之间的sige沟道;以及nmos,其包含在源极区域与漏极区域之间的si沟道。

技术特征:

1.一种形成半导体器件的方法,包含以下步骤:

2.根据权利要求1所述的方法,其中所述第一材料包含硅干式氧化si)。

3.根据权利要求1所述的方法,其中所述第二材料包含锗硅(sige)。

4.根据权利要求1所述的方法,其中所述包覆材料包含锗硅(sige)。

5.根据权利要求4所述的方法,其中所述包覆材料在所述纳米薄片的所述多个第一层上外延地生长。

6.根据权利要求1所述的方法,其中对所述纳米薄片进行干式氧化的步骤包含以下步骤:在700℃至950℃的范围中的温度下将所述半导体器件暴露于快速热氧化处理。

7.根据权利要求1所述的方法,移除所述第一材料的所述氧化物的步骤包含以下步骤:将所述第一材料暴露于稀释hf溶液。

8.根据权利要求1所述的方法,进一步包含以下步骤:在形成所述包覆材料之前修整所述纳米薄片,以将所述纳米薄片的厚度从在6 nm至8 nm的范围中的初始厚度减小到在2 nm至3 nm的范围中的减小厚度。

9.根据权利要求8所述的方法,其中更靠近所述基板的纳米薄片相较于更远离所述基板的纳米薄片具有更大的减小厚度。

10.根据权利要求1所述的方法,进一步包含以下步骤:在干式氧化之前在所述包覆材料上形成氧化物。

11.根据权利要求10所述的方法,其中所述包覆材料上的所述氧化物是通过原子层沉积形成的。

12.根据权利要求10所述的方法,其中所述包覆材料上的所述氧化物包含由高密度等离子体形成的可流动氧化物。

13.根据权利要求10所述的方法,其中所述包覆材料上的所述氧化物是在400℃至600℃的范围中的温度下通过快速等离子体氧化形成的。

14.根据权利要求10所述的方法,进一步包含以下步骤:通过在干式氧化之前暴露于稀释的hf/h2o2溶液来移除所述氧化物。

15.根据权利要求1所述的方法,进一步包含以下步骤:通过外延生长或通过化学气相沉积在所述包覆材料的所述纳米薄片上形成硅盖。

16.根据权利要求15所述的方法,其中所述硅盖具有在2 å至20 å的范围中的厚度。

17.根据权利要求15所述的方法,进一步包含以下步骤:形成与包覆材料的所述纳米薄片接触的高介电常数金属栅极。

18.根据权利要求1所述的方法,进一步包含以下步骤:在基板的顶表面上形成所述超晶格结构,所述第一层及第二层的每一者具有独立地在3 nm至20 nm的范围中的厚度。

19.根据权利要求18所述的方法,进一步包含以下步骤:邻近所述超晶格结构的第一端形成所述源极区域并且邻近所述超晶格结构的第二相对端形成所述漏极区域。

20.一种电子器件,包含:

技术总结

描述了水平环栅器件及其制造方法。这些hGAA器件包含在器件的源极区域与漏极区域之间的半导体材料。该方法包括在第一材料上形成包覆材料,接着进行干式氧化处理,从而导致包覆材料及第一材料的重新排列。

技术研发人员:杨世海,乔迪·A·弗龙海尔,本杰明·科伦坡,B·普拉纳瑟提哈兰,埃尔·迈赫迪·巴齐兹,阿希什·派欧

受保护的技术使用者:应用材料公司

技术研发日:

技术公布日:2025/2/10

- 还没有人留言评论。精彩留言会获得点赞!