一种SiC-Si混合开关栅极驱动信号调制电路及调制方法与流程

本发明属于sic-si混合开关驱动,特别是涉及一种sic-si混合开关栅极驱动信号调制电路及调制方法。

背景技术:

1、碳化硅金属氧化物半导体场效应晶体管(silicon carbide metal-oxidesemiconductor field effect transistor,sic mosfet)作为宽禁带器件的代表,相比于发展多年的硅基绝缘栅双极型晶体管(silicon insulated gate bipolar transistor,siigbt),具备更低的开关时间和更高的热稳定性,有利于电力系统的效率和功率密度提升。但目前受制于生产工艺和器件结构的限制,在大功率场景下,sic mosfet的成本是阻碍其发展的重要原因。将sic mosfet和si igbt并联使用,构成混合开关结构(hybrid switch,hys),利用sic mosfet的低导通时间的特性,降低si igbt的开关损耗,sic/si hys结构成为一种折中效率和成本的综合解决方案。由于sic mosfet的导通速度比si igbt更快,由此sic mosfet和si igbt的控制策略和导通时间需要进行额外控制。其中最小sic mosfet导通控制模式,为了降低采用sic mosfet的电流容量,同时减小sic mosfet的导通时间,避免sic mosfet和si igbt导通过程中的热失效问题。相比于并联导通控制模式下,多出了两个关断时间尺度,控制sic mosfet额外的关断和导通时间,因此最小sic mosfet导通模式的控制信号的生成更为复杂,也会增加了控制器的计算负荷。

技术实现思路

1、本发明目的是为了解决现有技术中的问题,提出了一种sic-si混合开关栅极驱动信号调制电路及调制方法。该电路可以将单器件的控制信号调制为sic/si hys内sicmosfet和si igbt的控制信号。本发明所提出的信号调制电路,结构简单,有效输出sicmosfet和si igbt的控制信号,且针对最小sic mosfet导通模式下的四个时间尺度,仅需要调节对应的rc缓冲电路的参数,即可实现时间尺度的改变。

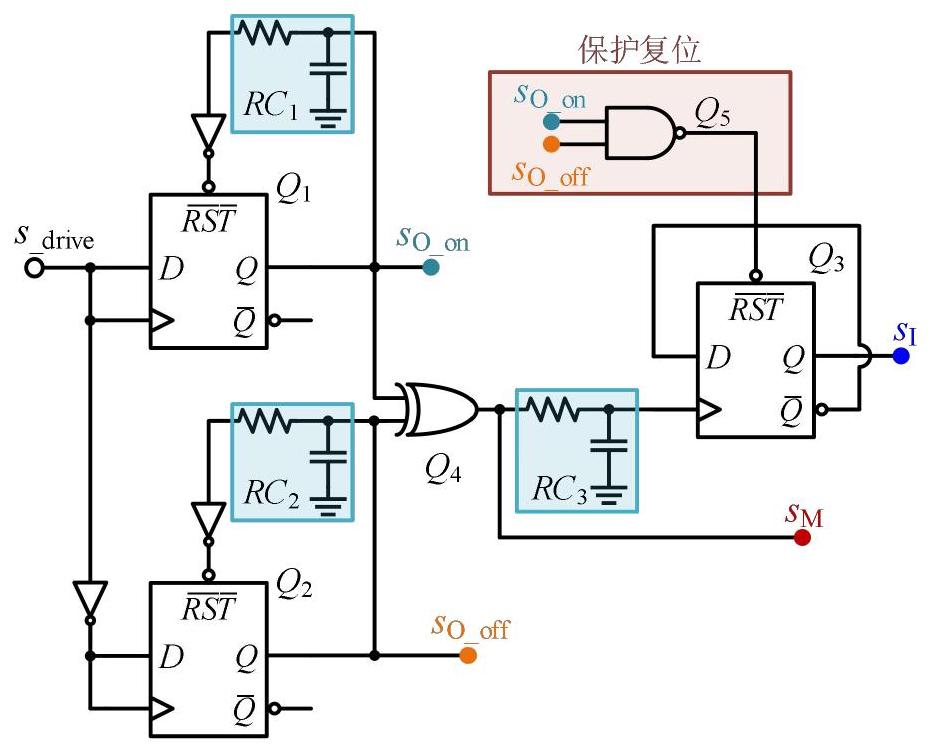

2、本发明是通过以下技术方案实现的,本发明提出一种sic-si混合开关栅极驱动信号调制电路,所述电路包括q1~q3的d触发器,或门q4,与非门q5和缓冲电路rc1~rc3组成的时间延迟单元;其中d触发器实现对sic mosfet和si igbt的信号电平转变控制,rc缓冲电路用以调节输入信号的上升沿斜率,从而控制最小sic mosfet导通模式中所对应的四个时间尺度;与非门q5对sic mosfet的两个脉冲信号进行检测,防止脉冲重叠,并重置si igbt对应的驱动信号si。

3、进一步地,所述q1的d触发器与缓冲电路rc1组成的时间延迟单元串联后与q2的d触发器和缓冲电路rc2组成的时间延迟单元串联的电路并联;两个时间延迟单元与或门q4相连;或门q4的另一端与缓冲电路rc3组成的时间延迟单元相连,所述缓冲电路rc3组成的时间延迟单元的另一端与q3的d触发器相连,所述q3的d触发器另一端与与非门q5相连。

4、本发明提出一种基于所述的sic-si混合开关栅极驱动信号调制电路的调制方法,所述方法具体为:

5、所述调制电路处于导通阶段:当输入的驱动信号s_drive由低电平转变为高电平,产生上升沿触发q1,sic mosfet的导通脉冲so_on同步由低电平转变为高电平,同时so_on开始为rc1缓冲电路进行充电,达到非门电路的触发阈值电平,将q1的rst引脚拉低,so_on同步转变为低电平;当so_on的上升沿经过rc3缓冲后,触发q3,si信号取反,由低电平转为高电平,驱动si igbt开始导通;

6、所述调制电路处于关断瞬态阶段:在s_drive转变为低电平的同时,经过非门的信号产生上升沿驱动q2,至此关断延迟脉冲信号so_off,经过rc2的延迟重置q2同时拉低so_off;后级so_off再次触发q3,对si取反,si经过rc3的延迟后转变为低电平,并驱动si igbt关断。

7、进一步地,驱动信号s_drive的上升沿和下降沿分别触发d触发产生导通脉冲so_on和关断脉冲so_off,两个脉冲经过或门进行逻辑运算,生成sic mosfet驱动信号sm。

8、进一步地,对于最小sic导通模式下的sic/si hys涉及td1~td4四个时间尺度,全都由rc缓冲电路进行设置,因此只需要配置相对应的电容容值和电阻阻值即可设置对应时间尺度。

9、进一步地,四个时间尺度对应的调节关系具体为:rc1调节td1+td2;rc2调节td3+td4,rc3调节td1和td3。

10、进一步地,所述rc缓冲电路等效为一个一阶rc充电电路,触发器输入电压,也就是电容电压可以计算表示为:

11、

12、其中vcc为供电电压。

13、进一步地,当电容电压上升至非门高电平阈值电平vt+触发后级电路,因此计算对应的延迟时间tdelay可以表示为:

14、

15、根据上式调节rc缓冲电路电阻电容值,进一步实现对sic/si hys驱动信号的四个时间尺度的设定或调节。

16、本发明的有益效果:

17、本发明提出了一种sic-si混合开关栅极驱动信号调制电路及调制方法。该电路可以将单器件的控制信号调制为sic/si hys内sic mosfet和si igbt的控制信号。本发明所提出的信号调制电路,结构简单,有效输出sic mosfet和si igbt的控制信号,且针对最小sic mosfet导通模式下的四个时间尺度,仅需要调节对应的rc缓冲电路的参数,即可实现时间尺度的改变。

技术特征:

1.一种sic-si混合开关栅极驱动信号调制电路,其特征在于,所述电路包括q1~q3的d触发器,或门q4,与非门q5和缓冲电路rc1~rc3组成的时间延迟单元;其中d触发器实现对sic mosfet和si igbt的信号电平转变控制,rc缓冲电路用以调节输入信号的上升沿斜率,从而控制最小sic mosfet导通模式中所对应的四个时间尺度;与非门q5对sic mosfet的两个脉冲信号进行检测,防止脉冲重叠,并重置si igbt对应的驱动信号si。

2.根据权利要求1所述的电路,其特征在于,所述q1的d触发器与缓冲电路rc1组成的时间延迟单元串联后与q2的d触发器和缓冲电路rc2组成的时间延迟单元串联的电路并联;两个时间延迟单元与或门q4相连;或门q4的另一端与缓冲电路rc3组成的时间延迟单元相连,所述缓冲电路rc3组成的时间延迟单元的另一端与q3的d触发器相连,所述q3的d触发器另一端与与非门q5相连。

3.一种基于权利要求1-2任一项所述的sic-si混合开关栅极驱动信号调制电路的调制方法,其特征在于,所述方法具体为:

4.根据权利要求3所述的方法,其特征在于,驱动信号s_drive的上升沿和下降沿分别触发d触发产生导通脉冲so_on和关断脉冲so_off,两个脉冲经过或门进行逻辑运算,生成sicmosfet驱动信号sm。

5.根据权利要求4所述的方法,其特征在于,对于最小sic导通模式下的sic/si hys涉及td1~td4四个时间尺度,全都由rc缓冲电路进行设置,因此只需要配置相对应的电容容值和电阻阻值即可设置对应时间尺度。

6.根据权利要求5所述的方法,其特征在于,四个时间尺度对应的调节关系具体为:rc1调节td1+td2;rc2调节td3+td4,rc3调节td1和td3。

7.根据权利要求6所述的方法,其特征在于,所述rc缓冲电路等效为一个一阶rc充电电路,触发器输入电压,也就是电容电压可以计算表示为:

8.根据权利要求7所述的方法,其特征在于,当电容电压上升至非门高电平阈值电平vt+触发后级电路,因此计算对应的延迟时间tdelay可以表示为:

技术总结

本发明提出一种SiC‑Si混合开关栅极驱动信号调制电路及调制方法。所述电路包括Q<subgt;1</subgt;~Q<subgt;3</subgt;的D触发器,或门Q<subgt;4</subgt;,与非门Q<subgt;5</subgt;和缓冲电路RC<subgt;1</subgt;~RC<subgt;3</subgt;组成的时间延迟单元。该电路可以将单器件的控制信号调制为SiC/Si HyS内SiC MOSFET和Si IGBT的控制信号。本发明所提出的信号调制电路,结构简单,有效输出SiC MOSFET和Si IGBT的控制信号,且针对最小SiC MOSFET导通模式下的四个时间尺度,仅需要调节对应的RC缓冲电路的参数,即可实现时间尺度的改变。

技术研发人员:江海洋,王智超,左峰,姚瑶,刘刚,王鹏,杨铎,王盼宝,徐殿国

受保护的技术使用者:国网黑龙江省电力有限公司

技术研发日:

技术公布日:2024/5/12

- 还没有人留言评论。精彩留言会获得点赞!