半导体器件及其制造方法与流程

实施方式涉及半导体器件及其制造方法。

背景技术:

1、dram器件包括:栅极结构,每个栅极结构在第一方向上延伸穿过有源图案的上部;位线结构,在有源图案的中心部分上在第二方向上延伸;接触插塞结构,分别在有源图案的相反的端部上;以及电容器,分别设置在接触插塞结构上。

2、在dram器件中,存储容量取决于每个电容器的面积和每个电容器中包括的电介质层的介电常数。因此,需要一种增加半导体器件的存储容量的新方法。

技术实现思路

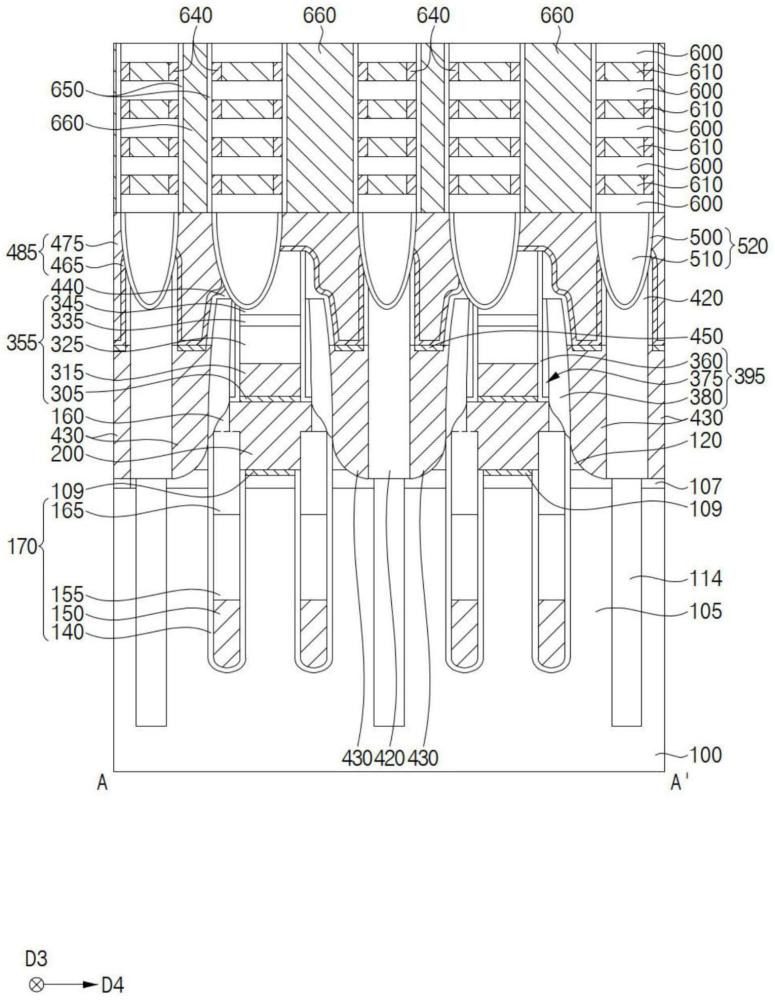

1、实施方式针对一种半导体器件,该半导体器件包括:在第一基板上的栅极结构;在栅极结构上的位线结构;在第一基板上的接触插塞结构,该接触插塞结构与位线结构间隔开;在位线结构和接触插塞结构上的堆叠结构,该堆叠结构包括在基本上垂直于第一基板的上表面的垂直方向上交替堆叠的绝缘层和板电极;电容器,包括延伸穿过堆叠结构并接触接触插塞结构的第二电极、在第二电极的侧壁上的铁电图案以及在铁电图案的侧壁上的第一电极,第一电极分别接触板电极的侧壁并在垂直方向上彼此间隔开。

2、实施方式还针对一种半导体器件,该半导体器件包括:在第一基板上的栅极结构,该栅极结构在基本上平行于第一基板的上表面的第一方向上延伸;在栅极结构上的位线结构;在第一基板上的接触插塞结构,该接触插塞结构与位线结构间隔开;在位线结构和接触插塞结构上的堆叠结构,该堆叠结构包括在基本上垂直于第一基板的上表面的垂直方向上交替堆叠的绝缘层和板电极;以及电容器,包括延伸穿过堆叠结构并接触接触插塞结构的第二电极、在第二电极的侧壁上的铁电图案以及在铁电图案的侧壁上的第一电极,该第一电极接触每个板电极的侧壁,其中堆叠结构在第一方向上的边缘部分具有阶梯形状。

3、实施方式还可以针对一种半导体器件,该半导体器件包括:在第一基板上的有源图案;在第一基板上的隔离结构;覆盖有源图案的侧壁的隔离结构;栅极结构,延伸穿过有源图案的上部和隔离结构的上部,每个栅极结构在基本上平行于第一基板的上表面的第一方向上延伸,栅极结构在基本上平行于第一基板的上表面并与第一方向相交的第二方向上彼此间隔开;位线结构,在有源图案和隔离结构上,每个位线结构在第二方向上延伸,位线结构在第一方向上彼此间隔开;接触插塞结构,分别接触有源图案的上表面;在位线结构和接触插塞结构上的堆叠结构,该堆叠结构包括在基本上垂直于第一基板的上表面的垂直方向上交替堆叠的绝缘层和板电极;以及电容器,包括延伸穿过堆叠结构并接触每个接触插塞结构的第二电极、在第二电极的侧壁上的铁电图案以及在铁电图案的侧壁上的第一电极,第一电极分别接触板电极的侧壁并在垂直方向上彼此间隔开。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中所述第二电极具有在所述垂直方向上延伸的柱形,以及

3.根据权利要求2所述的半导体器件,其中每个所述第一电极在平行于所述第一基板的所述上表面的水平方向上从所述铁电图案的所述侧壁突出。

4.根据权利要求1所述的半导体器件,其中每个所述第一电极不接触所述绝缘层的侧壁。

5.根据权利要求1所述的半导体器件,其中每个所述第一电极具有侧壁,该侧壁在平行于所述第一基板的所述上表面的水平方向上具有朝向所述板电极中的对应一个的所述侧壁的凸起形状。

6.根据权利要求1所述的半导体器件,其中每个所述板电极包括掺有杂质的多晶硅或掺有杂质的硅锗,所述第一电极和所述第二电极中的每个包括金属。

7.根据权利要求1所述的半导体器件,其中所述电容器是在平行于所述第一基板的所述上表面并彼此交叉的第一方向和第二方向上彼此间隔开的多个电容器中的一个,所述多个电容器延伸穿过所述堆叠结构。

8.根据权利要求1所述的半导体器件,其中:

9.根据权利要求8所述的半导体器件,其中所述电容器是在所述第一方向上彼此间隔开的多个电容器中的一个,并且所述多个电容器中的每个延伸穿过所述多个堆叠结构中的相应一个。

10.根据权利要求1所述的半导体器件,其中:

11.根据权利要求1所述的半导体器件,还包括:

12.根据权利要求11所述的半导体器件,其中所述第一基板包括多晶硅。

13.一种半导体器件,包括:

14.根据权利要求13所述的半导体器件,其中所述电容器是在所述第一方向和第二方向上彼此间隔开的多个电容器中的一个,所述第二方向平行于所述第一基板的所述上表面并与所述第一方向相交,所述多个电容器延伸穿过所述堆叠结构。

15.根据权利要求13所述的半导体器件,其中:

16.根据权利要求15所述的半导体器件,其中所述电容器是在所述第一方向上彼此间隔开的多个电容器中的一个,并且所述多个电容器中的每个延伸穿过所述多个堆叠结构中的相应一个。

17.根据权利要求13所述的半导体器件,其中:

18.根据权利要求17所述的半导体器件,其中所述第一电极在平行于所述第一基板的所述上表面的水平方向上从所述铁电图案的所述侧壁突出。

19.根据权利要求13所述的半导体器件,其中所述第一电极不接触所述绝缘层的侧壁。

20.一种半导体器件,包括:

技术总结

一种半导体器件包括栅极结构、位线结构、接触插塞结构、堆叠结构和电容器。栅极结构设置在第一基板上。位线结构设置在栅极结构上。接触插塞结构设置在第一基板上并与位线结构间隔开。堆叠结构设置在位线结构和接触插塞结构上,并可以包括在与第一基板的上表面基本上垂直的垂直方向上交替堆叠的绝缘层和板电极。电容器包括延伸穿过堆叠结构并接触接触插塞结构的第二电极。铁电图案设置在第二电极的侧壁上。第一电极设置在铁电图形的侧壁上、分别接触板电极的侧壁并在垂直方向上彼此间隔开。

技术研发人员:李基硕,韩珍优,林汉镇

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/8/15

- 还没有人留言评论。精彩留言会获得点赞!