阵列基板、阵列基板制备方法及显示装置与流程

本申请涉及显示,尤其涉及一种阵列基板、阵列基板制备方法及显示装置。

背景技术:

1、有机发光二极管(organic light emitting diode,简称oled)和量子点发光二极管(quantμm-dot light emitting diodes,简称qled)为主动发光显示器件,具有自发光、广视角、高对比度、低耗电、极高反应速度、轻薄、可弯曲和成本低等优点。但是,在显示基板中,区域空间距离较近的两条金属走线之间由于电势不一致,容易积累静电电荷进而产生静电释放(electro-static discharge,简称esd),对显示基板造成静电击伤,影响显示基板正常工作,降低了产品的良率。

技术实现思路

1、有鉴于此,本申请的目的在于提出一种阵列基板、阵列基板制备方法及显示装置,以解决显示基板中空间距离相近的走线之间容易发生esd击伤的问题。

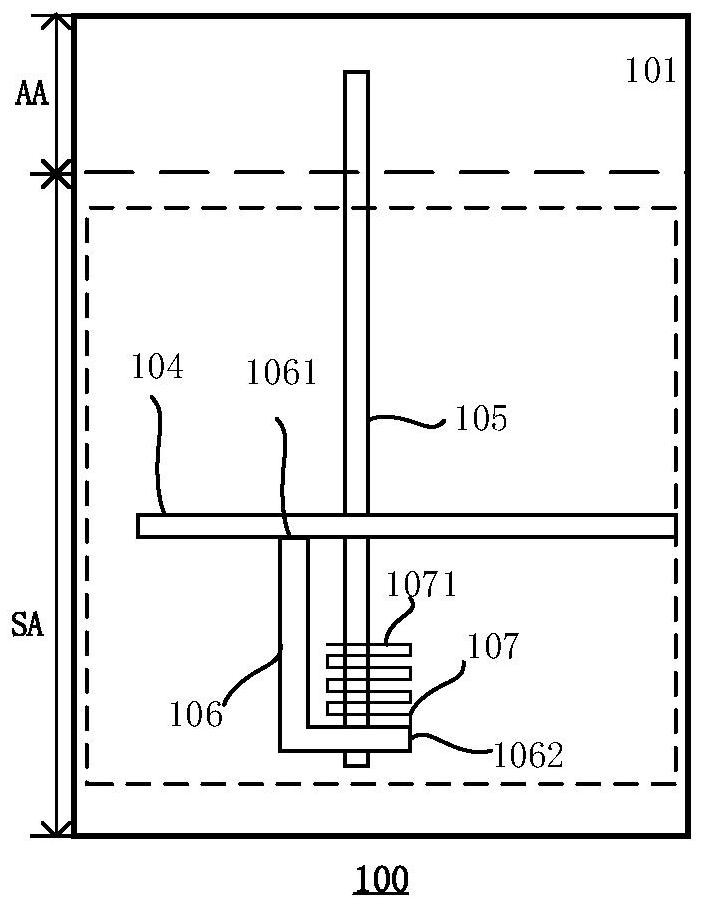

2、基于上述目的,本申请的第一方面提供了一种阵列基板,包括:

3、衬底基板,包括像素区域和与所述像素区域紧邻的非像素区域;

4、第一走线层,位于所述衬底基板的一侧,包括第一走线、第一静电释放部和尖端放电结构;所述第一走线、所述第一静电释放部和所述尖端放电结构位于所述非像素区域;所述第一静电释放部的第一端与所述第一走线连接,所述第一静电释放部的第二端悬空;所述尖端放电结构和所述第一静电释放部连接;

5、第二走线层,位于所述衬底基板与所述第一走线层之间,或位于所述第一走线层远离所述衬底基板的一侧,包括第二走线;所述第二走线位于所述非像素区域;所述第二走线在所述衬底基板上的正投影与所述尖端放电结构在所述衬底基板上的正投影存在交叠。

6、可选的,所述第一走线层还包括第二静电释放部,所述第二静电释放部的第一端与所述第一走线连接,所述第二静电释放部的第二端悬空。

7、可选的,所述第二静电释放部的第二端在所述衬底基板上的正投影与所述第一静电释放部的第二端在所述衬底基板上的正投影不重叠。

8、可选的,所述第一静电释放部的第二端的延长线与所述第二静电释放部的第二端重叠,或,所述第二静电释放部的第二端的延长线与所述第一静电释放部的第二端重叠。

9、可选的,所述第一静电释放部的第二端在所述衬底基板上的正投影与所述第二走线在所述衬底基板上的正投影之间的距离超过第一预设距离。

10、可选的,所述第二静电释放部在所述衬底基板上的正投影与所述第二走线在所述衬底基板上的正投影不重叠。

11、可选的,所述尖端放电结构与所述第一静电释放部的第二端之间的距离超过第二预设距离。

12、可选的,所述尖端放电结构包括第一尖端结构,所述第一尖端结构包括直线、弯折线或绕线中的至少一种。

13、可选的,所述尖端放电结构包括第二尖端结构,所述第二尖端结构的尖端夹角小于90°。

14、可选的,所述第二走线层位于所述衬底基板与所述第一走线层之间,所述第一走线层为第一栅线金属层,所述第一走线为第一数据线,所述第二走线层为背部金属层,所述第二走线为背部金属层中的信号线。

15、本申请的第二方面还提供了一种阵列基板的制备方法,应用于第一方面所述的阵列基板,包括:当所述第一走线为开路时,采用导电材料连通所述第一静电释放部的第二端和所述第二静电释放部的第二端。

16、本申请的第四方面还提供了一种显示装置,包括如第一方面所述的阵列基板。

17、从上面所述可以看出,本申请提供的阵列基板,包括衬底基板,衬底基板包括像素区域和与所述像素区域紧邻的非像素区域;第一走线层,位于所述衬底基板的一侧,包括第一走线、第一静电释放部和尖端放电结构;所述第一走线、所述第一静电释放部和所述尖端放电结构位于所述非像素区域;第二走线层,位于所述衬底基板与所述第一走线层之间,或位于所述第一走线层远离所述衬底基板的一侧,包括第二走线;所述第二走线位于所述非像素区域。所述第一静电释放部的第一端与所述第一走线连接,所述第一静电释放部的第二端悬空;所述尖端放电结构和所述第一静电释放部连接;在第一走线和第二走线之间产生静电电荷积累时,能够通过第一静电释放部将第一走线和第二走线之间积累的静电电荷有效转移至第一静电释放部。所述第二走线在所述衬底基板上的正投影与所述尖端放电结构在所述衬底基板上的正投影存在交叠,有利于通过尖端放电结构诱发静电释放,将静电释放区域转移至尖端放电结构处,避免第一走线和第二走线之间膜层交界处形成静电击伤现象,影响阵列基板正常工作,本申请提供的阵列基板能够降低显示装置出现静电击伤的概率,进而提升产品良率。

技术特征:

1.一种阵列基板,其特征在于,包括:

2.根据权利要求1所述的阵列基板,其特征在于,所述第一走线层还包括第二静电释放部,所述第二静电释放部的第一端与所述第一走线连接,所述第二静电释放部的第二端悬空。

3.根据权利要求2所述的阵列基板,其特征在于,所述第二静电释放部的第二端在所述衬底基板上的正投影与所述第一静电释放部的第二端在所述衬底基板上的正投影不重叠。

4.根据权利要求2所述的阵列基板,其特征在于,所述第一静电释放部的第二端的延长线与所述第二静电释放部的第二端重叠,或,所述第二静电释放部的第二端的延长线与所述第一静电释放部的第二端重叠。

5.根据权利要求4所述的阵列基板,其特征在于,所述第一静电释放部的第二端在所述衬底基板上的正投影与所述第二走线在所述衬底基板上的正投影之间的距离超过第一预设距离。

6.根据权利要求2所述的阵列基板,其特征在于,所述第二静电释放部在所述衬底基板上的正投影与所述第二走线在所述衬底基板上的正投影不重叠。

7.根据权利要求2-6任一项所述的阵列基板,其特征在于,所述尖端放电结构与所述第一静电释放部的第二端之间的距离超过第二预设距离。

8.根据权利要求1-6任一项所述的阵列基板,其特征在于,所述尖端放电结构包括第一尖端结构,所述第一尖端结构包括直线、弯折线或绕线中的至少一种。

9.根据权利要求1-6任一项所述的阵列基板,其特征在于,所述尖端放电结构包括第二尖端结构,所述第二尖端结构的尖端夹角小于90°。

10.根据权利要求1所述的阵列基板,其特征在于,所述第二走线层位于所述衬底基板与所述第一走线层之间,所述第一走线层为第一栅线金属层,所述第一走线为第一数据线,所述第二走线层为背部金属层,所述第二走线为背部金属层中的信号线。

11.一种阵列基板的制备方法,应用于权利要求2-10任一项所述的阵列基板,其特征在于,包括:

12.一种显示装置,其特征在于,包括如权利要求1-10所述的阵列基板。

技术总结

本申请提供一种阵列基板、阵列基板制备方法及显示装置,所述阵列基板包括衬底基板,包括像素区域和与所述像素区域紧邻的非像素区域;第一走线层,位于衬底基板的一侧,包括第一走线、第一静电释放部和尖端放电结构;第一走线、第一静电释放部和尖端放电结构位于所述非像素区域;第二走线层,位于衬底基板与所述第一走线层之间,或位于第一走线层远离衬底基板的一侧,包括第二走线;所述第二走线位于所述非像素区域。所述第一静电释放部的第一端与所述第一走线连接,所述第一静电释放部的第二端悬空;所述尖端放电结构和所述第一静电释放部连接。所述第二走线在所述衬底基板上的正投影与所述尖端放电结构在所述衬底基板上的正投影存在交叠。

技术研发人员:田雨,王培,张凯,姚景涛,陆菁宇

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:

技术公布日:2024/5/6

- 还没有人留言评论。精彩留言会获得点赞!