一种三维堆叠存储器及其制造方法与流程

本发明涉及半导体,特别涉及一种三维堆叠存储器及其制造方法。

背景技术:

1、ddr sdram(double data rate synchronous dynamic random access memory,双倍数据传输率同步动态随机存取存储器)是sdram的升级版本,ddr在时钟信号上升沿与下降沿各传输一次数据,这使得ddr的数据传输速度为传统sdram的两倍。随着计算量的激增,1代的ddr发展到2代ddr再到3代ddr、4代ddr甚至更高端的5代ddr。其中较为主流的ddr3是同步动态随机存取存储器的一种,同步是指ddr3数据的读取写入是按时钟同步的,动态是指ddr3中的数据掉电无法保存且保持数据需要周期性的刷新,随机存取是指可以随机操作任一地址的数据。目前随着数据处理量的增加,比如游戏和高性能计算领域,迫切需要高带宽的应用,高带宽内存(hbm,high bandwidth memory)成为绕过dram传统io增强模式演进的方案。但hbm制备成本高昂,系统搭配缺乏灵活性,并且hbm与主芯片封装在一起,不存在容量扩展的可能。而目前主流ddr3颗粒数据位宽为8位、16位,但处理器ddr控制器的数据位宽有32位、64位、72位等,通过单片颗粒就无法满足数据处理要求,需要多片颗粒集成,但这样做就增加了系统的面积与重量。

技术实现思路

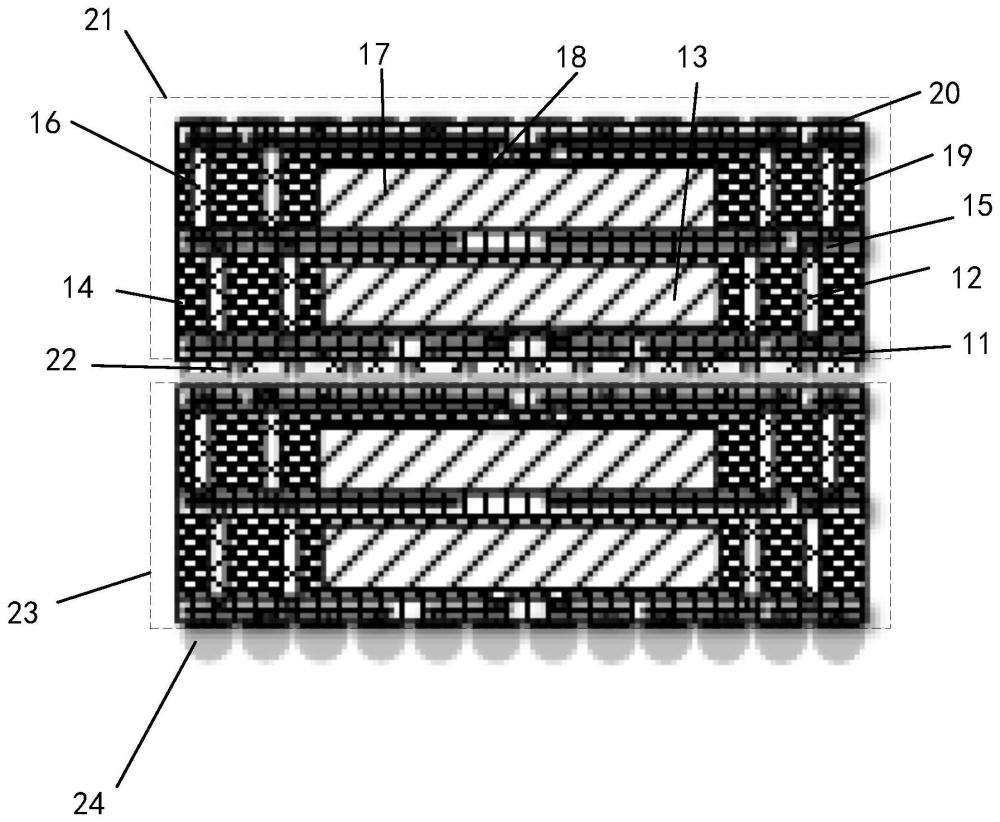

1、针对现有技术中的部分或全部问题,本发明提供一种三维堆叠存储器,所述三维堆叠存储器包括多个存储器子模块,所述多个存储器子模块通过模块间连接结构电连接,所述存储器子模块包括:

2、第一重布线层;

3、第一垂直互连结构,所述第一垂直互连结构设置在所述第一重布线层的第一表面;

4、第一存储芯片模块,所述第一存储芯片模块设置在所述第一重布线层的第一表面;

5、第一塑封层,所述第一塑封层设置在所述第一重布线层的第一表面,塑封并包覆所述第一存储芯片模块和所述第一垂直互连结构,但露出所述第一垂直互连结构的第一表面;

6、第二重布线层,所述第二重布线层设置在所述第一塑封层的第一表面;

7、第二垂直互连结构,所述第二垂直互连结构设置在所述第二重布线层的第一表面;

8、第二存储芯片模块,所述第二存储芯片模块设置在所述第二重布线层的第一表面;

9、第二塑封层,所述第二塑封层设置在所述第二重布线层的第一表面,塑封并包覆所述第二存储芯片模块和所述第二垂直互连结构,但露出所述第二垂直互连结构的第一表面;

10、第三重布线层,所述第三重布线层设置在所述第二塑封层的第一表面;

11、所述第二重布线层通过所述第一垂直互连结构与所述第一重布线层电连接;

12、所述第三重布线层通过所述第二垂直互连结构与所述第二重布线层电连接;

13、所述第一存储芯片模块通过其表面的凸点与所述第一重布线层或者所述第二重布线层电连接;

14、所述第二存储芯片模块通过其表面的凸点与所述第二重布线层或者所述第三重布线层电连接。

15、进一步地,模块间连接结构为焊球或者凸块结构或者ubm结构。

16、进一步地,所述第一重布线层包括第一介质层;和/或

17、所述第二重布线层包括第二介质层;和/或

18、所述第三重布线层包括第三介质层。

19、进一步地,所述第一垂直互连结构为塑封通孔;和/或

20、所述第二垂直互连结构为塑封通孔。

21、进一步地,所述第一存储芯片模块和所述第二存储芯片模块包含多个相同的芯片,或者多个同类型的芯片,或者多个不同类型的芯片。

22、进一步地,所述第一存储芯片模块的芯片通过点到点式拓扑结构或者平衡t型分支式拓扑结构或者串联式拓扑结构进行连接;和/或

23、所述第二存储芯片模块的芯片通过点到点式拓扑结构或者平衡t型分支式拓扑结构或者串联式拓扑结构进行连接。

24、本发明还提供一种三维堆叠存储器的制造方法,该方法包括如下步骤:

25、在载片的第一表面,制作第一重布线层;

26、在所述第一重布线层的第一表面制作第一垂直互连结构;

27、将第一存储芯片模块布置在所述第一重布线层的第一表面;

28、塑封并包覆所述第一存储芯片模块和所述第一垂直互连结构,形成第一塑封层;

29、减薄所述第一塑封层,露出所述第一垂直互连结构的第一表面;

30、在所述第一塑封层的第一表面,制作第二重布线层;

31、在所述第二重布线层的第一表面制作第二垂直互连结构;

32、将第二存储芯片模块布置在所述第二重布线层的第一表面;

33、塑封并包覆所述第二存储芯片模块和所述第二垂直互连结构,形成第二塑封层;

34、减薄所述第二塑封层,露出所述第二垂直互连结构的第一表面和所述第二存储芯片模块的第二表面,并去除所述载片;

35、在所述第二塑封层的第一表面,制作第三重布线层,形成存储器子模块;

36、在所述存储器子模块的第二表面制作模块间连接结构;

37、键合多个所述存储器子模块,形成键合后的堆叠存储器;

38、在所述键合后的堆叠存储器的第二表面外接焊球。

39、进一步地,所述塑封为注塑成型;

40、所述第一塑封层和所述第二塑封层的材料为环氧树脂。

41、进一步地,所述键合包括热压键合或者晶圆级键合。

42、进一步地,所述存储器子模块的焊接区域覆盖非导电胶膜。

43、与现有技术相比,本发明具有以下优点:

44、1.本发明通过基于扇出型晶圆级封装工艺,形成三维堆叠存储器,实现了存储器芯片根据系统需求自定义扩展位宽的需求。

45、2.本发明提出的三维堆叠存储器能实现大位宽、大容量,并有效地减小了系统面积,相比hbm,能有效减低芯片的制备成本。

技术特征:

1.一种三维堆叠存储器,其特征在于,所述三维堆叠存储器包括多个存储器子模块,所述多个存储器子模块通过模块间连接结构电连接,所述存储器子模块包括:

2.根据权利要求1所述的三维堆叠存储器,其特征在于,

3.根据权利要求1所述的三维堆叠存储器,其特征在于,

4.根据权利要求1所述的三维堆叠存储器,其特征在于,

5.根据权利要求1所述的三维堆叠存储器,其特征在于,

6.根据权利要求1所述的三维堆叠存储器,其特征在于,

7.一种三维堆叠存储器的制造方法,其特征在于,包括如下步骤:

8.根据权利要求7所述的三维堆叠存储器的制造方法,其特征在于,

9.根据权利要求7所述的三维堆叠存储器的制造方法,其特征在于,

10.根据权利要求9所述的三维堆叠存储器的制造方法,其特征在于,

技术总结

本发明涉及一种三维堆叠存储器及其制造方法。所述三维堆叠存储器包括多个存储器子模块,所述多个存储器子模块通过模块间连接结构电连接,所述存储器子模块包括:第一重布线层、第一垂直互连结构、第一存储芯片模块、第一塑封层、第二重布线层、第二垂直互连结构、第二存储芯片模块、第二塑封层以及第三重布线层。所述第二重布线层通过所述第一垂直互连结构与所述第一重布线层电连接;所述第三重布线层通过所述第二垂直互连结构与所述第二重布线层电连接。通过基于FOWLP工艺,形成三维堆叠存储器,实现存储芯片根据系统需求自定义扩展位宽的需求。三维堆叠存储器能实现大位宽、大容量,并有效地减小了系统面积,并相较HBM能有效减低芯片的制备成本。

技术研发人员:杨成林,周云燕,张文雯,宋刚

受保护的技术使用者:华进半导体封装先导技术研发中心有限公司

技术研发日:

技术公布日:2024/5/6

- 还没有人留言评论。精彩留言会获得点赞!