一种用于事件型视觉传感器的压缩编码电路

本发明涉及事件型视觉传感器事件编码电路领域,尤其涉及一种用于事件型视觉传感器的压缩编码电路。

背景技术:

1、事件型视觉传感器是一种检测并输出外界光强变化的传感器,每个像素独立感知光强变化,并离散化为光强增加和光强减少的事件;与传统的积分型cmos传感器相比,它输出的数据量更少,响应速度更快,功耗更低。因此,事件型视觉传感器在高速,高实时性,高动态范围的场合具有广泛应用。

2、事件型视觉传感器的事件数据编码过程一般分为以下几步:首先列选择电路选中产生事件的某一列,并将该列的事件传输至列采样寄存器电路中;之后编码电路将接收到的事件数据进行地址事件表示(address-event representation,aer)编码,最后通过输出接口电路将这些编码完成的数据输出。所述aer编码即(x,y,p,t)四元编码,其中x,y为像素的坐标,p为事件极性,t为事件触发时间。像素触发事件时,列选择电路会选通像素所在列,列地址数据即该列像素的序号,同时,时间戳电路也会生成时间戳数据并传输至系统控制电路。传统编码方式的事件型视觉传感器产生的列地址数据(即y数据)和时间戳数据(即t数据)占用较大输出位宽,在像素密集地触发事件条件下,存在大量数据冗余,传统的aer编码方式会存在大量资源浪费,增大后级数据传输带宽压力,因此需要对列地址数据和时间戳数据进行压缩编码。

技术实现思路

1、本发明所要解决的技术问题在于,针对现有的事件型视觉传感器编码存在的种种不足,提供一种用于事件型视觉传感器的压缩编码电路。

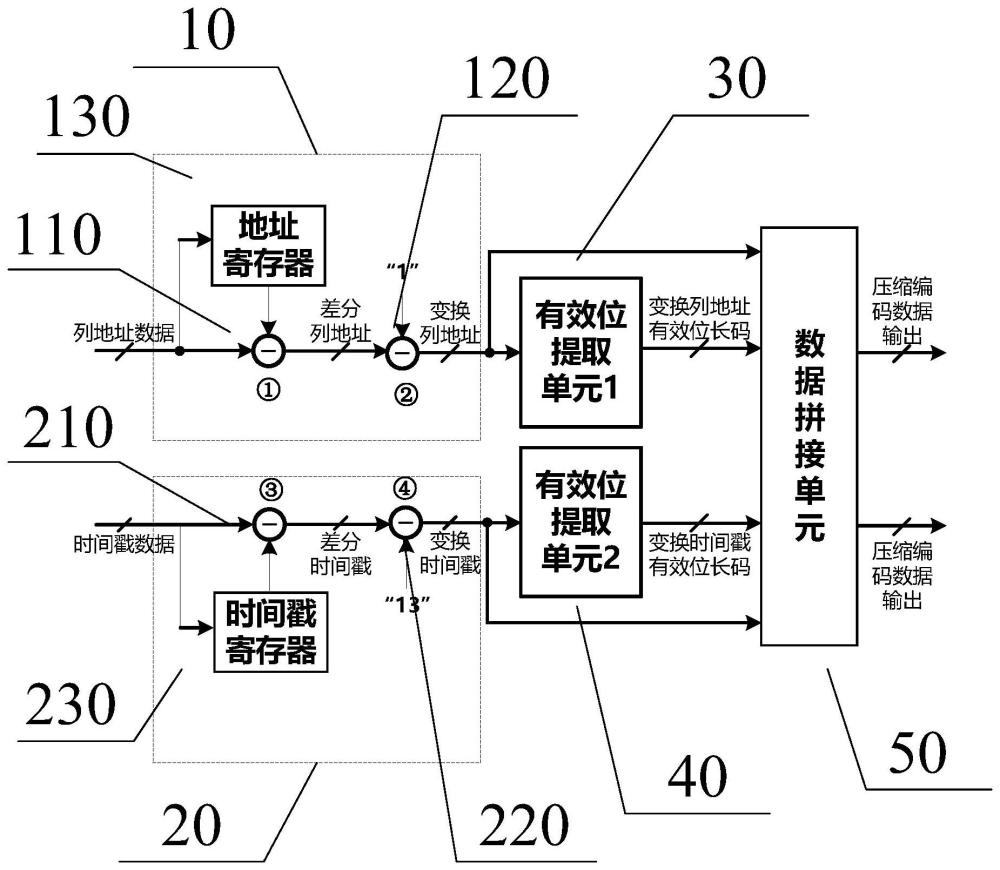

2、为了解决上述技术问题,本发明实施例提供了一种用于事件型视觉传感器的压缩编码电路,包括:列地址数据处理单元、时间戳数据处理单元、第一有效位提取单元、第二有效位提取单元和数据拼接单元;

3、所述地址数据处理单元用于对列地址数据进行处理,获取变换列地址数据;

4、所述第一有效位提取单元用于对所述变换列地址数据处理,获取变换列地址有效位长码;

5、所述时间戳数据处理单元用于对时间戳数据进行处理,获取变换时间戳数据;

6、所述第二有效位提取单元用于对所述变换时间戳数据进行处理,获取变换时间戳有效位长码;

7、所述数据拼接单元用于将所述变换列地址数据和变换列地址有效位长码、变换时间戳数据和变换时间戳有效位长码进行拼接形成最终压缩数据,并输出所述最终压缩数据;

8、其中,所述地址数据处理单元输入端与所述列地址数据相连接,输出端分别与第一有效位提取单元、数据拼接单元相连接;所述时间戳数据处理单元输入端与时间戳数据相连接,输出端分别与第二有效位提取单元、数据拼接单元相连接;所述第一有效位提取单元输出端、第二有效位提取单元输出端与所述数据拼接单元相连接。

9、优选的,所述列地址数据处理单元包括地址寄存器、第一减法器和第二减法器;

10、所述地址寄存器用于存储前一时刻的列地址数据;

11、所述第一减法器用于将这一时刻的列地址数据与前一时刻的列地址数据进行减法运算,获得差分列地址数据;

12、所述第二减法器用于将所述差分列地址数据与第一预设常数进行减法运算,获得变换列地址数据。

13、优选的,所述列地址数据分别与所述地址寄存器、第一减法器输入端相连接;所述地址寄存器输出端与所述第一减法器输入端相连接;所述第一减法器输出端与所述第二减法器输入端相连接;所述第二减法器输出端分别与所述第一有效位提取单元输入端、数据拼接单元输入端相连接。

14、优选的,所述时间戳数据处理单元包括时间戳寄存器、第三减法器和第四减法器;

15、所述时间戳寄存器用于存储前一时刻的时间戳数据;

16、所述第三减法器用于将这一时刻的时间戳数据与前一时刻的时间戳数据进行减法运算,获得差分时间戳数据;

17、所述第四减法器用于将所述差分时间戳数据与第二预设常数进行减法运算,获得变换时间戳数据。

18、优选的,所述时间戳数据分别与所述时间戳寄存器、第三减法器输入端相连接;所述时间戳寄存器输出端与所述第三减法器输入端相连接;所述第三减法器输出端与所述第四减法器输入端相连接;所述第四减法器输出端分别与所述第二有效位提取单元输入端、数据拼接单元输入端相连接。

19、优选的,所述第二有效位提取单元包括第一d触发器组、第二d触发器组、第五减法器、反相器、与门和多路选择器;

20、其中,所述第一d触发器组输入端与所述变换时间戳数据相连接,输出端分别与所述第五减法器输入端、与门输入端相连接;所述第五减法器输出端与所述反相器相连接;所述反相器输出端与所述与门另一输入端相连接;所述与门输出端与所述第二d触发器组相连接;所述第二d触发器组输出端与所述多路选择器相连接;所述多路选择器最终输出变换时间戳有效位长码。

21、优选的,所述变换时间戳数据通过所述第一d触发器组完成第一次高低位调换后,得到初加工数据;通过所述第五减法器进行减法运算,再经过所述反相器反相,得到二次加工数据;将所述初加工数据与二次加工数据通过与门相与后再通过第二d触发器组完成第二次高低位调换;最后进入所述多路选择器。

22、优选的,所述第五减法器另一输入端为数字“1”;所述初加工数据与所述数字“1”进行减法运算。

23、优选的,所述第一d触发器组、第二d触发器组、反相器和与门的位宽为32bit。

24、优选的,所述第一有效位提取单元与所述第二有效位提取单元结构相同;所述第一d触发器组、第二d触发器组、反相器和与门的位宽为10bit。

25、实施本发明实施例,具有如下有益效果:

26、(1)本发明实施例通过地址数据处理单元、时间戳数据处理单元对原始的列地址数据、时间戳数据进行处理,获取变换列地址数据和变换时间戳数据。再通过第一有效位提取单元、第二有效位提取单元获取变换列地址有效位长码、变换时间戳有效位长码,即表示所述变换列地址数据和变换时间戳所需的最小位数。最后通过所述数据拼接单元将所述变换列地址数据和变换列地址有效位长码、变换时间戳数据和变换时间戳有效位长码进行拼接形成最终压缩数据。拼接后的最终压缩数据即保留了原始的列地址数据、时间戳数据所有有用信息,又比原始的列地址数据、时间戳数据的位宽小,实现了对原始的列地址数据、时间戳数据的压缩,使需要编码的数据量显著减少,且最高可将数据压缩至1bit,从而避免了硬件资源的浪费,提高了事件数据的编码效率。

技术特征:

1.一种用于事件型视觉传感器的压缩编码电路,其特征在于,包括:列地址数据处理单元、时间戳数据处理单元、第一有效位提取单元、第二有效位提取单元和数据拼接单元;

2.根据权利要求1所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述列地址数据处理单元包括地址寄存器、第一减法器和第二减法器;

3.根据权利要求2所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述列地址数据分别与所述地址寄存器、第一减法器输入端相连接;所述地址寄存器输出端与所述第一减法器输入端相连接;所述第一减法器输出端与所述第二减法器输入端相连接;所述第二减法器输出端分别与所述第一有效位提取单元输入端、数据拼接单元输入端相连接。

4.根据权利要求1所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述时间戳数据处理单元包括时间戳寄存器、第三减法器和第四减法器;

5.根据权利要求4所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述时间戳数据分别与所述时间戳寄存器、第三减法器输入端相连接;所述时间戳寄存器输出端与所述第三减法器输入端相连接;所述第三减法器输出端与所述第四减法器输入端相连接;所述第四减法器输出端分别与所述第二有效位提取单元输入端、数据拼接单元输入端相连接。

6.根据权利要求1所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述第二有效位提取单元包括第一d触发器组、第二d触发器组、第五减法器、反相器、与门和多路选择器;

7.根据权利要求6所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述变换时间戳数据通过所述第一d触发器组完成第一次高低位调换后,得到初加工数据;通过所述第五减法器进行减法运算,再经过所述反相器反相,得到二次加工数据;将所述初加工数据与二次加工数据通过与门相与后再通过第二d触发器组完成第二次高低位调换;最后进入所述多路选择器。

8.根据权利要求7所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述第五减法器另一输入端为数字“1”;所述初加工数据与所述数字“1”进行减法运算。

9.根据权利要求6所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述第一d触发器组、第二d触发器组、反相器和与门的位宽为32bit。

10.根据权利要求6所述用于事件型视觉传感器的压缩编码电路,其特征在于,所述第一有效位提取单元与所述第二有效位提取单元结构相同;所述第一d触发器组、第二d触发器组、反相器和与门的位宽为10bit。

技术总结

本发明公开了一种用于事件型视觉传感器的压缩编码电路,包括:列地址数据处理单元、时间戳数据处理单元、第一有效位提取单元、第二有效位提取单元和数据拼接单元;地址数据处理单元用于获取变换列地址数据;第一有效位提取单元用于对变换列地址数据处理,获取变换列地址有效位长码;时间戳数据处理单元用于获取变换时间戳数据;第二有效位提取单元用于对变换时间戳数据进行处理,获取变换时间戳有效位长码;数据拼接单元用于将变换列地址数据和变换列地址有效位长码、变换时间戳数据和变换时间戳有效位长码进行拼接形成压缩数据。本发明实施例通过将列地址数据、时间戳数据处理并拼接后,将降低数据的位宽,提高了事件数据的编码效率。

技术研发人员:刘冬生,陈俊杰,简至杰,苏彦文,李豪,李凯岳

受保护的技术使用者:华中科技大学

技术研发日:

技术公布日:2024/6/11

- 还没有人留言评论。精彩留言会获得点赞!