一种用于消除ISI效应的标准单元电路及方法与流程

本发明涉及isi效应消除,具体为一种用于消除isi效应的标准单元电路及方法。

背景技术:

1、在现有技术中,常常使用nmos管和pmos管共同构成的驱动电路来对设备的io端口进行驱动,但由于工艺本身的限制,会出现isi效应,从而使输出的数据出现抖动,影响数据的传输质量。

2、为了消除isi效应,目前常用的方法是增加电压或者增加晶体管的尺寸,但这样芯片的设计面积会变得很大,消除的isi效应也有限,同时晶体管尺寸增加会使得功耗也得到提升,还会加大前一级的负载,可能会使得isi效应反而变得更强,也不符合芯片集成化、节能化的发展趋势。

3、在所述背景技术部分公开的上述信息仅用于加强对本公开的背景的理解,因此它可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本发明的目的在于提供一种用于消除isi效应的标准单元电路及方法,以解决上述背景技术中提出的问题。

2、为实现上述目的,本发明提供如下技术方案:

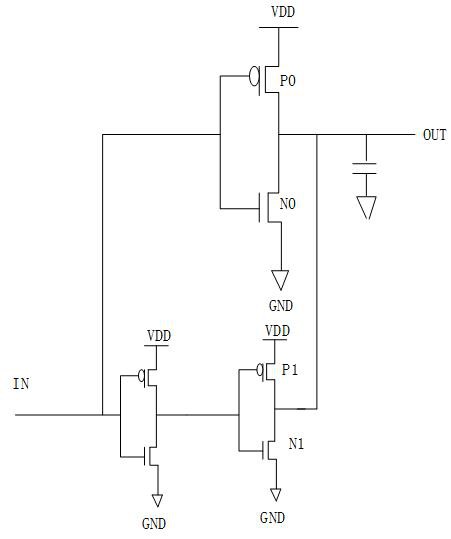

3、一种用于消除isi效应的标准单元电路,包括主驱动模块、副驱动模块和滤波模块,其中:

4、所述主驱动模块包括第一逻辑单元,用于根据输入信号产生第一输出信号;

5、所述副驱动模块包括第二逻辑单元和第三逻辑单元,用于根据输入信号产生第二输出信号,并将第二输出信号发送到主驱动模块的输出端与第一输出信号进行叠加;

6、所述滤波模块用于对第一输出信号和第二输出信号的叠加信号进行滤波,生成总输出信号。

7、优选的,所述第一输出信号与第二输出信号的相位相反。

8、优选的,所述第二逻辑单元的输入端与第一逻辑单元的输入端电性连接,用于接收相同的输入信号,所述第二逻辑单元的输出端与第三逻辑单元的输入端电性连接,所述第三逻辑单元的输出端与第一逻辑单元的输出端电性连接。

9、优选的,所述第一逻辑单元、第二逻辑单元和第三逻辑单元均包括一组pmos管和一组nmos管。

10、优选的,所述pmos管和nmos管采用共栅极接法,所述pmos管的源极接有工作电压,漏极与nmos管的源极电性连接,所述nmos管的漏极接地。

11、优选的,所述第一逻辑单元、第二逻辑单元和第三逻辑单元的输入端均为pmos管和nmos管的栅极,输出端均在pmos管的漏极和nmos管的源极之间。

12、一种用于消除isi效应的方法,所述消除isi效应的方法适用于上述的任一项标准单元电路,具体步骤如下:

13、将输入信号分为两路完全相同的信号,并分别发送到主驱动模块和副驱动模块;

14、主驱动模块根据输入信号生成第一输出信号,副驱动模块根据输入信号生成第二输出信号;

15、第一输出信号与第二输出信号叠加,生成总输出信号后进行输出。

16、与现有技术相比,本发明的有益效果是:本发明通过增加一路副驱动模块,根据输入信号产生第二输出信号来对第一输出信号进行修正,再将第一输出信号和第二输出信号叠加后作为总输出信号进行输出,能够降低输出电压的幅度,减少上升时间和下降时间,从而起到降低isi效应的效果,避开了增加电路功耗的缺点,且结构简单,使电路更加符合集成化,节能化的趋势。

技术特征:

1.一种用于消除isi效应的标准单元电路,其特征在于,包括主驱动模块、副驱动模块和滤波模块,其中:

2.根据权利要求1所述的一种用于消除isi效应的标准单元电路,其特征在于:所述第一输出信号与第二输出信号的相位相反。

3.根据权利要求1所述的一种用于消除isi效应的标准单元电路,其特征在于:所述第二逻辑单元的输入端与第一逻辑单元的输入端电性连接,用于接收相同的输入信号,所述第二逻辑单元的输出端与第三逻辑单元的输入端电性连接,所述第三逻辑单元的输出端与第一逻辑单元的输出端电性连接。

4.根据权利要求1所述的一种用于消除isi效应的标准单元电路,其特征在于:所述第一逻辑单元、第二逻辑单元和第三逻辑单元均包括一组pmos管和一组nmos管。

5.根据权利要求3所述的一种用于消除isi效应的标准单元电路,其特征在于:所述pmos管和nmos管采用共栅极接法,所述pmos管的源极接有工作电压,漏极与nmos管的源极电性连接,所述nmos管的漏极接地。

6.根据权利要求4所述的一种用于消除isi效应的标准单元电路,其特征在于:所述第一逻辑单元、第二逻辑单元和第三逻辑单元的输入端均为pmos管和nmos管的栅极,输出端均在pmos管的漏极和nmos管的源极之间。

7.一种用于消除isi效应的方法,其特征在于:所述消除isi效应的方法适用于权利要求1-5所述的任一项标准单元电路,具体步骤如下:

技术总结

本发明提供一种用于消除ISI效应的标准单元电路及方法,涉及ISI效应消除技术领域,包括主驱动模块、副驱动模块和滤波模块。本发明通过增加一路副驱动模块,根据输入信号产生第二输出信号来对第一输出信号进行修正,再将第一输出信号和第二输出信号叠加后作为总输出信号进行输出,能够降低输出电压的幅度,减少上升时间和下降时间,从而起到降低ISI效应的效果,避开了增加电路功耗的缺点,且结构简单,使电路更加符合集成化,节能化的趋势。

技术研发人员:林云,刘德启

受保护的技术使用者:博越微电子(江苏)有限公司

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!