一种半导体致冷器陶瓷双面集成电路及其制备方法与流程

本发明涉及集成电路制造领域,并且更具体地,涉及一种半导体致冷器陶瓷双面集成电路及其制备方法。

背景技术:

1、目前,随着电子产品小型化、轻量化、薄型化、高性能、i/o端数的增加以及功能多样化的发展,传统的半导体封装技术已不能很好的满足要求,使得对微型超微型半导体制冷器焊接成为亟待解决的问题和挑战。

2、半导体制冷器(tec)是一种利用半导体材料的peltier效应(珀耳帖效应)来实现制冷的电子器件。其原理是由半导体晶粒按一定顺序排列、并固定在绝缘的两块金属化陶瓷基板之间,故tec由半导体晶粒、导热绝缘材质基板、导线、焊料等组成。因陶瓷基板具有高导热性能、良好绝缘性能、以及高强度可提供平整表面,所以半导体制冷器件的导热绝缘材质基板广泛使用氧化铝、氮化铝等陶瓷基板。

3、半导体制冷器普遍使用浸润性良好的锡焊料将半导体颗粒焊接于金属化陶瓷基板表面,锡焊料在使用过程中会呈液态具有流动性。

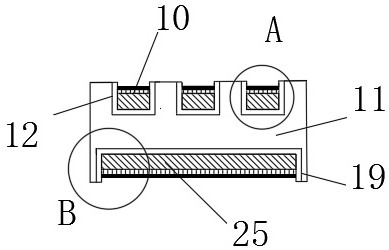

4、图1为现有的tec集成电路俯视图示意图,图1中,陶瓷基板11上分布有若干第一焊接小单元10,图2为截面示意图,图2中,第一焊接小单元10连接在陶瓷基板11的外表面上。在用焊料将半导体晶粒(也称为元器件)焊接到第一焊接小单元10上及后续tec的使用过程中,由于焊料表面张力的作用,焊料容易向外蔓延并与其他第一焊接小单元10接触,降低半导体晶粒焊接的可靠性和焊接精度,影响tec的质量。

5、为了解决该问题,有的技术人员采用增加设置表面光滑的金属铂材料阻挡层防止焊料蔓延接触,但效果并不理想;有的技术人员采用在第一焊接小单元10之间设置坑,当从第一焊接小单元10位置处蔓延而来的焊料经过坑时,流入坑内从而停止继续流动,该方法虽然有部分效果,但焊料向外蔓延的方向必须指定流到坑内才能停止流动,而焊料融化为液体形态,其流向可能向第一焊接小单元10四方流动,不必然流到坑内,而可能曲线流动。

6、上述背景技术是为了便于理解本发明,并非是申请本发明之前已向普通公众公开的公知技术。

技术实现思路

1、针对上述问题,本发明提供一种半导体致冷器陶瓷双面集成电路,该半导体致冷器陶瓷双面集成电路降低了半导体致冷器陶瓷双面集成电路的高度,更适宜于尺寸小型化。

2、一种半导体致冷器陶瓷双面集成电路,包括:

3、陶瓷基板;

4、至少两个第一焊接小单元;

5、至少两个第一盲孔;

6、一个第二焊接小单元;以及

7、一个第二盲孔;

8、其中,第一焊接小单元与第一盲孔的数量相等,第一盲孔由陶瓷基板的正表面向背表面方向延伸,第一焊接小单元的底面与第一盲孔的底面连接,第一焊接小单元的侧面与第一盲孔的侧壁连接,第一焊接小单元的顶面不高于陶瓷基板的正表面;第二盲孔由陶瓷基板的背表面向正表面方向延伸,第二焊接小单元的顶面与第二盲孔的底面连接,第二焊接小单元的侧面与第二盲孔的侧壁连接,第二焊接小单元的底面不低于陶瓷基板的背表面。

9、可选地,所述陶瓷基板为氮化铝陶瓷基板、氮化硼陶瓷基板、氧化铝陶瓷基板或氧化铍陶瓷基板。

10、可选地,所述第一焊接小单元的顶面低于陶瓷基板的正表面,所述第二焊接小单元的底面高于陶瓷基板的背表面。

11、可选地,所述第一焊接小单元包括第一金属层和第一预制焊料层,第一预制焊料层连接在第一金属层的正表面上;所述第二焊接小单元包括第二金属层和第二预制焊料层,第二预制焊料层连接在第二金属层的背表面上。

12、可选地,所述陶瓷基板的正表面与第一焊接小单元顶面之间的距离h1≧第一预制焊料层的液态体积/第一盲孔的截面积-第一预制焊料层的固态体积/第一盲孔的截面积;所述陶瓷基板的背表面与第二焊接小单元底面之间的距离h2≧第二预制焊料层的液态体积/第二盲孔的截面积-第二预制焊料层的固态体积/第二盲孔的截面积。

13、可选地,所述第一金属层为铜层、镍层、钯层、金层中的一层或多层,所述第一预制焊料层为金锡层,所述第二金属层为铜层、镍层、钯层、金层中的一层或多层,所述第二预制焊料层为金锡层。

14、可选地,所述第一预制焊料层厚度为3-10μm,所述第一金属层厚度为10-100μm;所述第二预制焊料层厚度为3-10μm,所述第二金属层厚度为10-100μm。

15、可选地,所述第一焊接小单元还包括第一底膜层,第一底膜层覆盖在第一盲孔的底面和侧面上;所述第二焊接小单元还包括第二底膜层,第二底膜层覆盖在第二盲孔的底面和侧面上。

16、可选地,所述第一底膜层厚度为100nm-1000nm,所述第二底膜层厚度为100nm-1000nm。

17、本发明还提供一种半导体致冷器陶瓷双面集成电路的制备方法。

18、一种半导体致冷器陶瓷双面集成电路的制备方法,包括以下步骤:

19、s1,陶瓷基板上形成做掩膜的光刻胶图形;

20、s2,陶瓷基板上刻出第一盲孔和第二盲孔;

21、s3,去掉光刻胶图形;

22、s5,形成做掩膜的光刻胶图形;

23、s6,电沉积,在第一盲孔内形成电沉积第一金属层,第二盲孔内形成电沉积第二金属层;

24、s7,电镀,在第一盲孔内形成第一预制焊料层,第二盲孔内形成第二预制焊料层;

25、s8,去掉光刻胶图形;

26、形成上述半导体致冷器陶瓷双面集成电路。

27、可选地,所述半导体致冷器陶瓷双面集成电路的制备方法中,s3后还包括s4,陶瓷基板的正面方向与背面方向分别溅射金属,形成第一底膜层和第二底膜层;s8后还包括s9,形成做掩膜的光刻胶图形;s9后还包括s10,去除底膜;s10后还包括s11,去除光刻胶图形。

28、可选地,s7中,在形成的第一预制焊料层前,先在s6电沉积形成的电沉积第一金属层上电镀形成电镀第一金属层,电沉积第二金属层上电镀形成电镀第二金属层。

29、与现有技术相比,本发明的有益效果在于:

30、本发明通过在陶瓷基板正表面上开设有第一盲孔,并将第一焊接小单元位于第一盲孔内,解决了焊料向外蔓延,同时降低了半导体致冷器陶瓷双面集成电路的高度,更适宜于尺寸小型化。

技术特征:

1.一种半导体致冷器陶瓷双面集成电路,其特征在于,包括:

2.根据权利要求1所述的半导体致冷器陶瓷双面集成电路,其特征在于,所述陶瓷基板为氮化铝陶瓷基板、氮化硼陶瓷基板、氧化铝陶瓷基板或氧化铍陶瓷基板;或/和

3.根据权利要求2所述的半导体致冷器陶瓷双面集成电路,其特征在于,所述第一焊接小单元包括第一金属层和第一预制焊料层,第一预制焊料层连接在第一金属层的正表面上;所述第二焊接小单元包括第二金属层和第二预制焊料层,第二预制焊料层连接在第二金属层的背表面上。

4.根据权利要求3所述的半导体致冷器陶瓷双面集成电路,其特征在于,所述陶瓷基板的正表面与第一焊接小单元顶面之间的距离h1≧第一预制焊料层的液态体积/第一盲孔的截面积-第一预制焊料层的固态体积/第一盲孔的截面积;所述陶瓷基板的背表面与第二焊接小单元底面之间的距离h2≧第二预制焊料层的液态体积/第二盲孔的截面积-第二预制焊料层的固态体积/第二盲孔的截面积。

5.根据权利要求3所述的半导体致冷器陶瓷双面集成电路,其特征在于,所述第一金属层为铜层、镍层、钯层、金层中的一层或多层,所述第一预制焊料层为金锡层,所述第二金属层为铜层、镍层、钯层、金层中的一层或多层,所述第二预制焊料层为金锡层。

6.根据权利要求5所述的半导体致冷器陶瓷双面集成电路,其特征在于,所述第一预制焊料层厚度为3-10μm,所述第一金属层厚度为10-100μm;所述第二预制焊料层厚度为3-10μm,所述第二金属层厚度为10-100μm。

7.根据权利要求3-6任一项所述的半导体致冷器陶瓷双面集成电路,其特征在于,所述第一焊接小单元还包括第一底膜层,第一底膜层覆盖在第一盲孔的底面和侧面上;所述第二焊接小单元还包括第二底膜层,第二底膜层覆盖在第二盲孔的底面和侧面上。

8.根据权利要求7所述的半导体致冷器陶瓷双面集成电路,其特征在于,所述第一底膜层厚度为100nm-1000nm,所述第二底膜层厚度为100nm-1000nm。

9.一种半导体致冷器陶瓷双面集成电路的制备方法,其特征在于,包括以下步骤:

10.根据权利要求9所述的半导体致冷器陶瓷双面集成电路的制备方法,其特征在于,所述半导体致冷器陶瓷双面集成电路的制备方法中,s3后还包括s4,陶瓷基板的正面方向与背面方向分别溅射金属,形成第一底膜层和第二底膜层;s8后还包括s9,形成做掩膜的光刻胶图形;s9后还包括s10,去除底膜;s10后还包括s11,去除光刻胶图形;

技术总结

本发明公开了一种半导体致冷器陶瓷双面集成电路及其制备方法,属于集成电路制造领域,包括:陶瓷基板;至少两个第一焊接小单元;至少两个第一盲孔;一个第二焊接小单元;以及一个第二盲孔;第一盲孔由陶瓷基板的正表面向背表面方向延伸,第一焊接小单元的底面与第一盲孔的底面连接,第一焊接小单元的侧面与第一盲孔的侧壁连接,第一焊接小单元的顶面不高于陶瓷基板的正表面;第二盲孔由陶瓷基板的背表面向正表面方向延伸,第二焊接小单元的顶面与第二盲孔的底面连接,第二焊接小单元的侧面与第二盲孔的侧壁连接,第二焊接小单元的底面不低于陶瓷基板的背表面。本发明降低了半导体致冷器陶瓷双面集成电路的高度,解决了焊料向外蔓延的问题。

技术研发人员:肖亚飞,孙世刚,徐健,杜晶,郑思原

受保护的技术使用者:四川科尔威光电科技有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!