一种带校正电路的相关多次采样低功耗计数器的制作方法

本发明涉及计数器电路,尤其涉及一种带校正电路的相关多次采样低功耗计数器。

背景技术:

1、随着cmos图像传感器(cmos image sensor,cis)不断发展,不仅对阵列规模、面积和功耗提出了更高要求,同时对性能要求也越来越苛刻。噪声一直是cis设计中重点关注的对象之一,如像素和列电路带来的读出噪声就对cis性能会产生直接影响。伴随着cis阵列规模的变大,小的工艺尺寸有利于cis实现更小的面积,但小的像素源跟随器(sourcefollower,sf)会带给读出电路中随机噪声更大,以至于信噪比(snr)变差。

2、通常一款低噪声读出电路的设计是减小读出噪声和提高snr的较为有效方式,近几年由于单斜adc(single-slope adc,ss adc)功耗、面积以及结构简单等方面的优势,受到cis设计者的青睐,ss adc主要由比较器(comparator)、斜坡发生器(ramp generator)和计数器(counter)等部分组成。与相关双采样(correlated double sampling,cds)不同,相关多次采样(correlated multiple sample,cms)采用多个黑色/信号样本的平均值来提高信噪比,该技术在ss adc中的实现可以有效抑制来自像素源跟随器和读出电路带来的随机噪声,计数器counter作为连接ss adc中比较器和数字信号处理电路的桥梁,其对数字域实现cms技术来进一步减小噪声具有关键的影响,因此如何减小计数器counter在实现相关多次采样过程中造成的计数错误是亟需解决的问题。

技术实现思路

1、本发明的目的是提供一种带校正电路的相关多次采样低功耗计数器,利用校正电路可以校正计数器counter在实现相关多次采样过程中造成的计数错误,使图像传感器可以实现数字域相关多次采样,减小来自像素源跟随器和读出电路带来的噪声,提高信噪比snr。

2、本发明的目的是通过以下技术方案实现的:

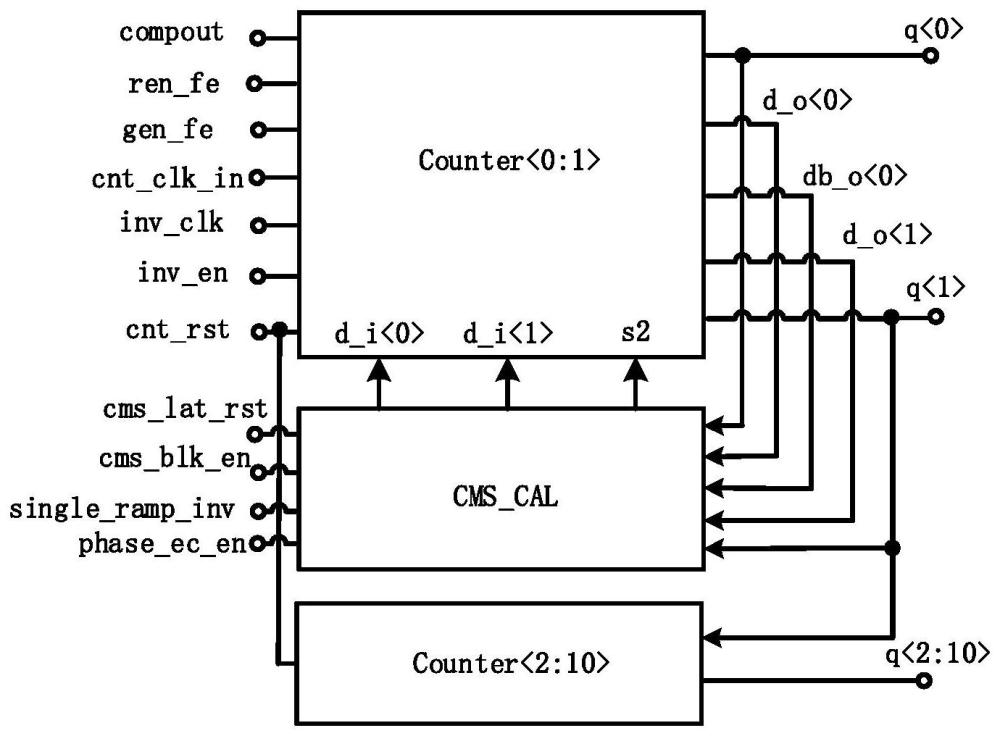

3、一种带校正电路的相关多次采样低功耗计数器,所述计数器包括第0~1级计数器counter<0:1>、第2~10级计数器counter<2:10>和相关多次采样校正电路cms_cal,其中:

4、所述第0~1级计数器counter<0:1>作为计数器实现低功耗设计的关键电路,所述第2~10级计数器counter<2:10>作为计数器结构中的重复级,具有相同电路结构;

5、所述第0~1级计数器counter<0:1>的输入信号compout为比较器输出信号,输入信号第0bit低功耗计数使能信号ren_fe、第1bit低功耗计数使能信号gen_fe、取反采样信号inv_clk、取反使能信号inv_en、计数器复位信号cnt_rst、第1bit计数进位校正采样信号cms_lat_rst、第0bit计数结果采样信号cms_blk_en和相关多次采样进位控制信号single_ramp_inv均由数字电路提供;输入信号cnt_clk_in由时钟产生电路提供;

6、所述第0~1级计数器counter<0:1>的输出信号正交时钟cnt_clk_q计数结果d_o<0>、正交时钟cnt_clk_q计数结果的反信号db_o<0>、正交时钟cnt_clk_i计数结果d_o<1>、第0bit计数结果q<0>和第1bit计数结果q<1>作为所述相关多次采样校正电路cms_cal的输入信号;

7、所述相关多次采样校正电路cms_cal的输出信号正交时钟cnt_clk_q取反校正信号d_i<0>、正交时钟cnt_clk_i取反校正信号d_i<1>和第1bit计数相位控制信号s2将送入所述第0~1级计数器counter<0:1>的输入端,用于校正相关多次采样过程中第0~1级计数器counter<0:1>错误翻转所引起的计数错误;

8、所述第0~1级计数器counter<0:1>和第2~10级计数器counter<2:10>输出的计数结果q<0:10>将送给外部读出电路,并最终送给数字电路进行处理。

9、由上述本发明提供的技术方案可以看出,利用校正电路可以校正计数器counter在实现相关多次采样过程中造成的计数错误,使图像传感器可以实现数字域相关多次采样,减小来自像素源跟随器和读出电路带来的噪声,提高信噪比snr。

技术特征:

1.一种带校正电路的相关多次采样低功耗计数器,其特征在于,所述计数器包括第0~1级计数器counter<0:1>、第2~10级计数器counter<2:10>和相关多次采样校正电路cms_cal,其中:

2.根据权利要求1所述带校正电路的相关多次采样低功耗计数器,其特征在于,所述第0~1级计数器counter<0:1>包括四个d触发器,分别为dff0、dff1、dff2和dff3;两个锁存器,分别为latch0和latch1;五个与非门,分别为nand0、nand1、nand2、nand3和nand4;11个反相器,分别为inv0、inv1、inv2、inv3、inv4、inv5、inv6、inv7、inv8、inv9、inv10;三个二选一数据选择器,分别为mux2_0、mux2_1和mux2_2;或非门nor0;以及两个异或门,分别为xor0和xor1,其中:

3.根据权利要求1所述带校正电路的相关多次采样低功耗计数器,其特征在于,所述第2~10级计数器counter<2:10>为传统二进制计数器结构,由9级相同的结构组成,每一级都是由二分频电路组成,分别为div2_0、div2_1、div2_2、div2_3、div2_4、div2_5、div2_6、div2_7和div2_8,且每一级的输出作为下一级的输入时钟;

4.根据权利要求1所述带校正电路的相关多次采样低功耗计数器,其特征在于,所述相关多次采样校正电路cms_cal包括四个锁存器,分别为latch2、latch3、latch4和latch5;四个二选一数据选择器,分别为mux2_3、mux2_4、mux2_5和mux2_6;三个反相器,分别为inv11、inv12和inv13;以及异或门xor2;

技术总结

本发明公开了一种带校正电路的相关多次采样低功耗计数器,包括第0~1级计数器Counter<0:1>、第2~10级计数器Counter<2:10>和相关多次采样校正电路CMS_CAL,第0~1级计数器Counter<0:1>作为计数器实现低功耗设计的关键电路,第2~10级计数器Counter<2:10>作为计数器结构中的重复级,具有相同电路结构;相关多次采样校正电路CMS_CAL用于校正相关多次采样过程中第0~1级计数器Counter<0:1>错误翻转所引起的计数错误。利用校正电路可以校正计数器counter在实现相关多次采样过程中造成的计数错误,使图像传感器可以实现数字域相关多次采样。

技术研发人员:王浩,鲁军阁

受保护的技术使用者:豪威科技(北京)股份有限公司

技术研发日:

技术公布日:2024/5/12

- 还没有人留言评论。精彩留言会获得点赞!