音频模数转换芯片阵列数据分时输出实现装置及实现方法与流程

本发明属于音频模数转换(adc)芯片阵列,具体涉及一种音频模数转换芯片阵列数据分时输出实现装置及实现方法。

背景技术:

1、随着语音识别技术的高速发展,音频adc(analog-to-digital converter,模拟数字转换器)芯片在该领域得到越来越广泛的应用。在一些要求比较高的语音识别应用领域,需要将多个音频adc芯片集成起来形成一个阵列(常称作麦克风阵列)的形式,用以提高语音识别的效果。

2、音频adc芯片阵列的集成方式多种多样,常见的有两类集成方式。第1类是将各个音频adc芯片的输出音频串行数据信号线以三态的方式集成在一根共享音频数据信号线上,然后各个音频adc芯片分时占用这根共享音频数据信号线,如附图1a所示;第2类是每个音频adc芯片包含一个音频数据输入信号线和一个音频数据输出信号线,然后将前一级音频adc芯片的音频输出信号线接到后一级音频adc芯片的音频输入信号线上,一级一级地传递下去,最后通过最后一级音频adc芯片的音频输出数据信号线传递出去,如附图1b所示。

3、第一类集成方式是将多个芯片的输出数据通过线与的方式连接在一起,每个芯片只在属于自己的时隙期间驱动数据输出,不属于自己的时隙期间对外输出高阻态。例如两个采样位宽为16比特,数据格式为dspb的芯片1和芯片2通过第一类集成方式,集成后总的adc输出示意图如图2所示,芯片1只在时隙1输出数据,在其他时间高阻输出,芯片2在时隙2输出数据,在其他时间高阻输出。

4、将不同芯片的输出数据线直接线与的集成方式,因不同芯片输出数据的延时不同,会出现在部分时间段上同时驱动的问题。如图4所示,芯片1和芯片2在相邻的两个时隙输出数据,芯片1的输出数据c1d0延时为t1,芯片2的输出数据c2d15延时为t2,由于t1和t2的不同,将使得c1d0和c2d15两者存在重叠,就会出现图中t3位置同时驱动的多驱动问题。

5、因此,针对上述技术问题,有必要提供一种新型的音频模数转换芯片数据输出方法。

6、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种音频模数转换芯片阵列数据分时输出实现装置及实现方法,其能够解决相邻两个字段时隙交接处存在多驱动冲突的问题。

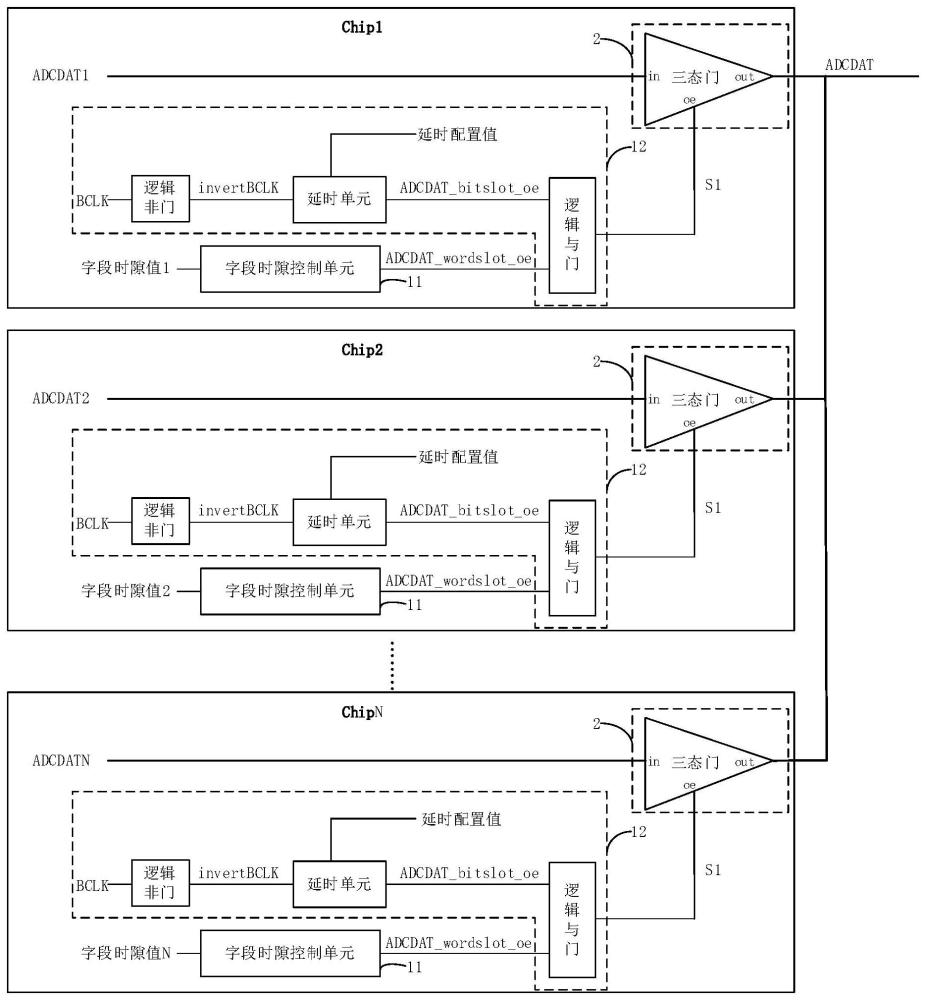

2、为了实现上述目的,本发明一具体实施例提供了一种音频模数转换芯片阵列数据分时输出实现装置,所述实现装置包括多个并联的音频模数转换芯片,所述音频模数转换芯片包括控制模块和开关模块;

3、所述控制模块包括字段时隙控制单元和第一逻辑运算单元,所述字段时隙控制单元用于基于字段时隙值产生字段时隙指示信号,所述第一逻辑运算单元用于对位时钟信号和字段时隙指示信号进行逻辑运算以获得第一控制信号,所述第一控制信号用于控制开关模块动作。

4、在本发明的一个或多个实施例中,所述第一逻辑运算单元包括逻辑非门、延时单元和逻辑与门;

5、所述逻辑非门用于对位时钟信号进行逻辑取反操作以产生位时钟取反信号,所述延时单元用于对位时钟取反信号进行延时操作以获得比特时隙指示信号;

6、所述逻辑与门用于对比特时隙指示信号和字段时隙指示信号进行与逻辑运算操作以获得第一控制信号。

7、在本发明的一个或多个实施例中,所述延时单元的延时时间大于等于音频模数转换芯片阵列中最大的音频模数转换芯片输出数据延时并且小于1/2比特时长。

8、在本发明的一个或多个实施例中,所述字段时隙控制单元包括时隙计数器,所述时隙计数器用于获取当前时隙位置计数值,所述字段时隙控制单元用于比较当前时隙位置计数值与字段时隙值以获得字段时隙指示信号。

9、在本发明的一个或多个实施例中,所述控制模块还包括字比特标志控制单元和第二逻辑运算单元;

10、所述字比特标志控制单元用于基于字长指示值和位时钟信号产生有效字长指示信号;

11、所述第二逻辑运算单元与第一逻辑运算单元以及字比特标志控制单元相连,所述第二逻辑运算单元用于对第一控制信号和有效字长指示信号进行或逻辑判断以获得第二控制信号;所述第二控制信号用于控制开关模块动作。

12、在本发明的一个或多个实施例中,所述字比特标志控制单元包括比特计数器,所述比特计数器用于标记当前字段时隙比特位置计数值;所述字比特标志控制单元用于基于标记当前字段时隙比特位置计数值和位时钟信号输出有效字长指示信号。

13、在本发明的一个或多个实施例中,所述开关模块为三态门电路,所述三态门电路包括使能控制端、输入端和输出端;所述输入端用于接收输入信号,所述输出端用于发送输入信号,所述使能控制端用于基于第一控制信号或者第二控制信号控制三态门电路的开启或者关断。

14、本发明一具体实施例提供了一种音频模数转换芯片阵列数据分时输出实现方法,基于任一项实施方式所述的音频模数转换芯片阵列数据分时输出实现装置,所述方法包括:

15、通过字段时隙控制单元基于字段时隙值产生字段时隙指示信号,通过第一逻辑运算单元对位时钟信号和字段时隙指示信号进行逻辑运算以获得第一控制信号;

16、基于第一控制信号控制开关模块动作。

17、在本发明的一个或多个实施例中,所述通过第一逻辑运算单元对位时钟信号和字段时隙指示信号进行逻辑运算以获得第一控制信号包括:

18、通过逻辑非门对位时钟信号进行逻辑取反操作以产生位时钟取反信号,通过延时单元对位时钟取反信号进行延时操作以获得比特时隙指示信号;

19、通过第一逻辑运算单元对比特时隙指示信号和字段时隙指示信号进行与逻辑判断以获得第一控制信号。

20、在本发明的一个或多个实施例中,所述方法还包括:

21、通过字比特标志控制单元基于字长指示值和位时钟信号产生有效字长指示信号;

22、通过第二逻辑运算单元对第一控制信号和有效字长指示信号进行或逻辑判断以获得第二控制信号;

23、基于第二控制信号控制开关模块动作。

24、与现有技术相比,本发明的音频模数转换芯片阵列数据分时输出实现装置及实现方法,通过将位时钟信号取反延时获得比特时隙指示信号,并通过逻辑与门用于对比特时隙指示信号和字段时隙指示信号进行与逻辑运算操作以获得第一控制信号的方法,将模数转换芯片阵列的输出数据的有效区间从一个比特时隙(等于一个位时钟周期)减小,以使相邻两个字段时隙交接处存在高阻态保护区间,由于这个高组态保护区间任何芯片都不会驱动,相邻两个字段时隙交接处不会存在多驱动冲突的问题。

技术特征:

1.一种音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述实现装置包括多个并联的音频模数转换芯片,所述音频模数转换芯片包括控制模块和开关模块;

2.根据权利要求1所述的音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述第一逻辑运算单元包括逻辑非门、延时单元和逻辑与门;

3.根据权利要求2所述的音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述延时单元的延时时间大于等于音频模数转换芯片阵列中最大的音频模数转换芯片输出数据延时并且小于1/2比特时长。

4.根据权利要求1所述的音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述字段时隙控制单元包括时隙计数器,所述时隙计数器用于标记当前时隙位置计数值,所述字段时隙控制单元用于比较当前时隙位置计数值与字段时隙值以获得字段时隙指示信号。

5.根据权利要求1所述的音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述控制模块还包括字比特标志控制单元和第二逻辑运算单元;

6.根据权利要求5所述的音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述字比特标志控制单元包括比特计数器,所述比特计数器用于标记当前字段时隙比特位置计数值;所述字比特标志控制单元用于基于标记当前字段时隙比特位置计数值和位时钟信号输出有效字长指示信号。

7.根据权利要求1或5所述的音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述开关模块为三态门电路,所述三态门电路包括使能控制端、输入端和输出端;所述输入端用于接收输入信号,所述输出端用于发送输入信号,所述使能控制端用于基于第一控制信号或者第二控制信号控制三态门电路的开启或者关断。

8.一种音频模数转换芯片阵列数据分时输出实现方法,基于如权利要求1~7任一项所述的音频模数转换芯片阵列数据分时输出实现装置,其特征在于,所述方法包括:

9.根据权利要求8所述的音频模数转换芯片阵列数据分时输出实现方法,其特征在于,所述通过第一逻辑运算单元对位时钟信号和字段时隙指示信号进行逻辑运算以获得第一控制信号包括:

10.根据权利要求8所述的音频模数转换芯片阵列数据分时输出实现方法,其特征在于,所述方法还包括:

技术总结

本发明公开了一种音频模数转换芯片阵列数据分时输出实现装置及实现方法,其中实现装置包括多个并联的音频模数转换芯片,音频模数转换芯片包括控制模块和开关模块;控制模块包括字段时隙控制单元和第一逻辑运算单元,字段时隙控制单元用于基于字段时隙值产生字段时隙指示信号,第一逻辑运算单元用于对位时钟信号和字段时隙指示信号进行逻辑运算以获得第一控制信号,第一控制信号用于控制开关模块动作。本发明通过将位时钟信号取反延时的方法,使得相邻两个字段时隙交接处存在半个比特时隙的高阻态保护区间,由于高组态保护区间任何芯片都不会驱动,解决了相邻两个字段时隙存在多驱动冲突的问题。

技术研发人员:汪俊达,张保华,於清,林坤

受保护的技术使用者:苏州顺芯半导体有限公司

技术研发日:

技术公布日:2024/6/2

- 还没有人留言评论。精彩留言会获得点赞!