一种车载SerDes芯片、包括其的汽车配件及汽车的制作方法

本发明涉及汽车通信传输领域,具体涉及一种车载serdes芯片、包括其的汽车配件及汽车。

背景技术:

1、随着互联网和信息技术日新月异的发展,数据接口的带宽和吞吐量越来越高。接口带宽的提升需要更加高速且抖动更小的时钟来进行同步和数据的恢复采集。

2、多相位采样技术能够避免时钟频率工作在数据速率,降低接口电路的功耗、提高电子产品的寿命,因此,高速高精度多相时钟对于当代接口系统至关重要。但产生高速且高精度的多相位时钟一直是一件富有挑战性的课题。首先,高速低抖动的时钟通常通过低频晶振时钟通过锁相环产生。使用较高频的参考时钟可以提高锁相环的带宽,减小锁相环的倍频因子,优化抖动性能,但是系统端的硬件开销会更大,且有些应用的知识产权ip核共用一颗低速晶振时钟。如何通过更低频率的参考时钟来产生高速低抖动的多相时钟来满足高速接口的要求也是一个难点。

3、现有的将参考时钟二倍频的技术需要参考时钟具有严格的50%占空比,否则将带来严重的参考杂散,因此需要对参考时钟的占空比进行校正。而对参考时钟进行四倍频需要复杂的后台自校准电路来减小占空比失真和抖动,增加了芯片的功耗、面积和设计复杂度。

技术实现思路

1、有鉴于此,本发明提供了一种车载serdes芯片、包括其的汽车配件及汽车,从而解决或者至少缓解了现有技术中存在的上述问题和其它方面的问题中的一个或多个。

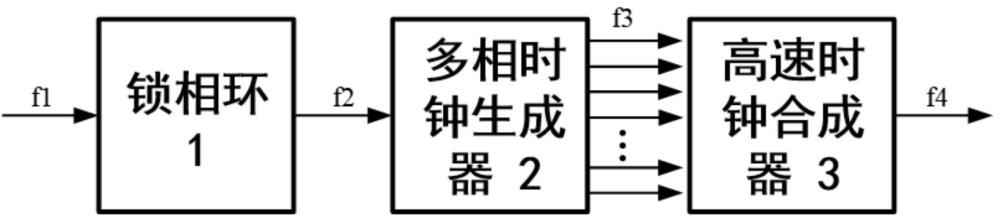

2、为了实现前述目的,本发明的第一方面提供了一种车载serdes芯片,其中,所述车载serdes芯片包括高速时钟生成系统,所述高速时钟生成系统包括:

3、锁相环,所述锁相环将输入的参考时钟信号f1进行倍频后生成高速时钟信号f2作为中间频率源;

4、多相时钟生成器,所述多相时钟生成器与所述锁相环连接,接收来自所述锁相环的所述高速时钟信号f2并生成同频多相位时钟信号f3;

5、高速时钟合成器,所述高速时钟合成器与所述多相时钟生成器连接,接收来自所述多相时钟生成器的所述同频多相位时钟信号f3并合成比所述高速时钟信号f2以及所述同频多相位时钟信号f3更高频的多相位合成时钟信号f4。

6、在如前所述的车载serdes芯片中,可选地,所述锁相环包括鉴相器、环路滤波器、压控振荡器、多模分频器以及delta-sigma调制器;所述鉴相器的输出端连接所述环路滤波器的输入端,所述环路滤波器的输出端连接所述压控振荡器的输入端,所述压控振荡器的输出端连接所述多相时钟生成器,并从所述压控振荡器和所述多相时钟生成器的中间分出一条支路连接到所述多模分频器,所述多模分频器的输出端再连回到所述鉴相器的输入端形成所述锁相环;在所述多模分频器和所述鉴相器的连接路中分出一条支路连接到所述delta-sigma调制器的输入端,所述delta-sigma调制器的输出端连接到所述多模分频器,形成反馈环;

7、所述鉴相器包括鉴频鉴相器和电荷泵,所述鉴频鉴相器将输入的参考时钟信号f1和来自所述多模分频器的反馈时钟信号fdiv的频率和相位进行比较得到误差信号,所述电荷泵将所述鉴频鉴相器输出的所述误差信号转换为电流信号输出给所述环路滤波器;

8、所述环路滤波器将来自所述电荷泵的所述电流信号转换为电压控制信号vctrl并对所述电压控制信号vctrl的高频杂散信号进行滤波后输出给所述压控振荡器,所述压控振荡器根据所述电压控制信号vctrl形成高速时钟信号f2,所述高速时钟信号f2一路输出给所述多相时钟生成器,另一路作为所述多模分频器的输入结合所述delta-sigma调制器提供的分频比进行小数分频产生低频的所述反馈时钟信号fdiv给所述鉴频鉴相器与所述参考时钟信号f1的相位进行对齐。

9、在如前所述的车载serdes芯片中,可选地,所述同频多相位时钟信号f3分为四相时钟或八相时钟或十六相时钟,所述多相位合成时钟信号f4分为两相时钟或四相时钟或八相时钟。

10、在如前所述的车载serdes芯片中,可选地,全速率时钟数据恢复使用所述两相时钟,时钟频率和数据速率相等。

11、在如前所述的车载serdes芯片中,可选地,半速率时钟数据恢复使用所述四相时钟,时钟频率是数据速率的一半。

12、在如前所述的车载serdes芯片中,可选地,四分之一速率时钟数据恢复使用所述八相时钟,时钟频率是数据速率的四分之一。

13、在如前所述的车载serdes芯片中,可选地,所述高速时钟合成器通过cmos逻辑电路将所述同频多相位时钟信号f3合成为所述多相位合成时钟信号f4。

14、在如前所述的车载serdes芯片中,可选地,所述多相时钟生成器包括多相时钟延迟链和注入锁定环,所述多相时钟延迟链与所述锁相环的输出端连接,所述多相时钟延迟链的输出端连接所述注入锁定环的输入端,所述注入锁定环的输出端连接至所述高速时钟合成器;

15、所述多相时钟延迟链用于生成同频率的多相时钟fm,所述同频率的多相时钟fm再通过所述注入锁定环生成相位关系精确的所述同频多相位时钟信号f3。

16、为了实现前述目的,本发明的第二方面提供了一种包括如前述第一方面中任一项所述的车载serdes芯片的汽车配件。

17、为了实现前述目的,本发明的第三方面提供了一种包括如前述第二方面中所述的汽车配件的汽车。

18、本发明提供了一种车载serdes芯片、包括其的汽车配件及汽车,其能够利用低速晶振时钟生成相位关系精确的高速多相时钟,且抖动性能优异,再合成频率更高的多相时钟,使serdes同步传输的数据量更大、效率更高。

技术特征:

1.一种车载serdes芯片,其特征在于,所述车载serdes芯片包括高速时钟生成系统,所述高速时钟生成系统包括:

2.如权利要求1所述的车载serdes芯片,其特征在于,所述锁相环(1)包括鉴相器(4)、环路滤波器(5)、压控振荡器(6)、多模分频器(7)以及delta-sigma调制器(8);所述鉴相器(4)的输出端连接所述环路滤波器(5)的输入端,所述环路滤波器(5)的输出端连接所述压控振荡器(6)的输入端,所述压控振荡器(6)的输出端连接所述多相时钟生成器(2),并从所述压控振荡器(6)和所述多相时钟生成器(2)的中间分出一条支路连接到所述多模分频器(7),所述多模分频器(7)的输出端再连回到所述鉴相器(4)的输入端形成所述锁相环(1);在所述多模分频器(7)和所述鉴相器(4)的连接路中分出一条支路连接到所述delta-sigma调制器(8)的输入端,所述delta-sigma调制器(8)的输出端连接到所述多模分频器(7),形成反馈环;

3.如权利要求1或2所述的车载serdes芯片,其特征在于,所述同频多相位时钟信号f3分为四相时钟或八相时钟或十六相时钟,所述多相位合成时钟信号f4分为两相时钟或四相时钟或八相时钟。

4.如权利要求3所述的车载serdes芯片,其特征在于,全速率时钟数据恢复使用所述两相时钟,时钟频率和数据速率相等。

5.如权利要求3所述的车载serdes芯片,其特征在于,半速率时钟数据恢复使用所述四相时钟,时钟频率是数据速率的一半。

6.如权利要求3所述的车载serdes芯片,其特征在于,四分之一速率时钟数据恢复使用所述八相时钟,时钟频率是数据速率的四分之一。

7.如权利要求1或2所述的车载serdes芯片,其特征在于,所述高速时钟合成器(3)通过cmos逻辑电路将所述同频多相位时钟信号f3合成为所述多相位合成时钟信号f4。

8.如权利要求1或2所述的车载serdes芯片,其特征在于,所述多相时钟生成器(2)包括多相时钟延迟链(9)和注入锁定环(10),所述多相时钟延迟链(9)与所述锁相环(1)的输出端连接,所述多相时钟延迟链(9)的输出端连接所述注入锁定环(10)的输入端,所述注入锁定环(10)的输出端连接至所述高速时钟合成器(3);

9.一种包括如权利要求1至8中任一项所述的车载serdes芯片的汽车配件。

10.一种包括如权利要求9所述的汽车配件的汽车。

技术总结

本发明涉及一种车载SerDes芯片、包括其的汽车配件及汽车。车载SerDes芯片包括高速时钟生成系统,高速时钟生成系统包括:锁相环,其将输入的参考时钟信号进行倍频后生成高速时钟信号作为中间频率源;多相时钟生成器,接收来自锁相环的高速时钟信号并生成同频多相位时钟信号;高速时钟合成器,接收来自多相时钟生成器的同频多相位时钟信号并合成比高速时钟信号以及同频多相位时钟信号更高频的多相位合成时钟信号。本发明能够利用低速晶振时钟生成相位关系精确的高速多相时钟,且抖动性能优异,再合成频率更高的多相时钟,使SerDes同步传输的数据量更大、效率更高。

技术研发人员:惠宇轩

受保护的技术使用者:南京仁芯科技有限公司

技术研发日:

技术公布日:2024/5/27

- 还没有人留言评论。精彩留言会获得点赞!