锁存器的制作方法

本发明涉及半导体集成电路,尤其是涉及一种锁存器。

背景技术:

1、集成电路技术节点的先进给芯片的可靠性带来了很多挑战,其中一个挑战就是单粒子效应带来的软错误。例如:当单个高能粒子如质子或α粒子等穿过芯片时,会在芯片中产生大量的电子空穴对,这些电子空穴对会形成瞬态电流,当芯片的尺寸越来越小时,这些由单粒子引起的瞬态电流可能会造成电路的逻辑状态翻转,从而产生软错误。软错误可能会发生在不同的电子设备中,例如汽车电子、医疗设备等。

2、并且,在深亚微米和纳米技术中,器件尺寸的急剧缩放以及电荷共享模型效应可能会使单粒子效应同时影响多个节点,并导致多节点翻转,大幅度增加了软错误的概率,多节点翻转在软错误中所占的比例越来越高。

技术实现思路

1、本发明的目的在于提供一种锁存器,可以抵抗多个节点的单粒子干扰,降低多节点翻转在软错误中所占的比例。

2、为了达到上述目的,本发明提供了一种锁存器,包括:

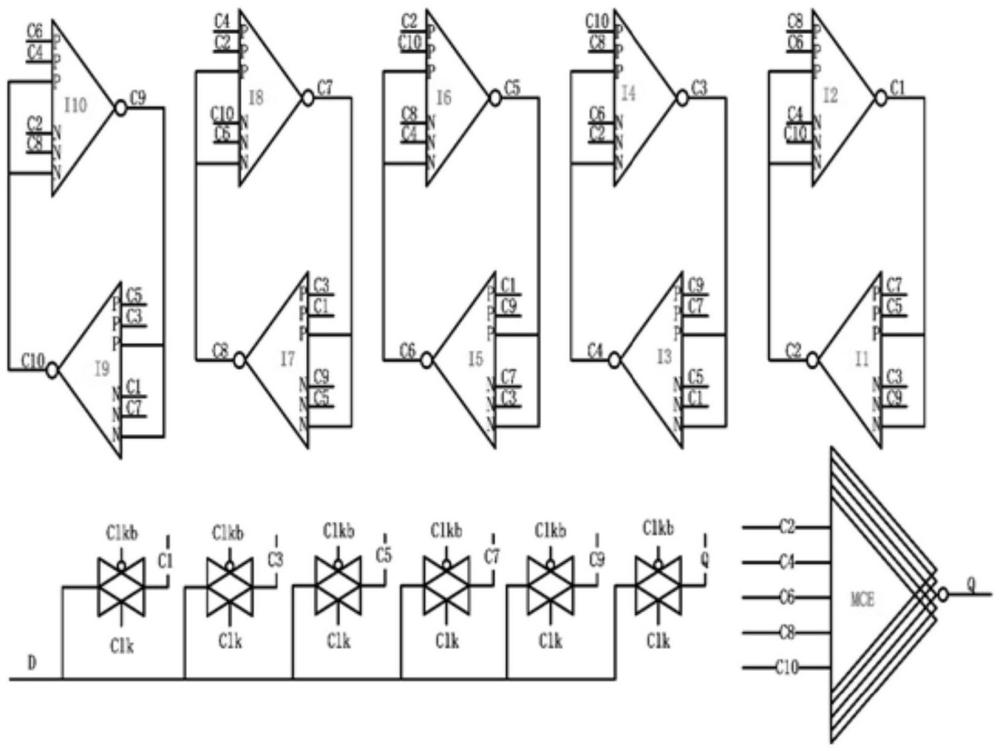

3、第一锁存结构至第五锁存结构和一个穆勒单元以及第一传输门至第六传输门;

4、每个锁存结构均由第一反向器和第二反向器组成,第一反向器包括依次串联的第一pmos管至第三pmos管以及依次串联的第一nmos管至第三nmos管,所述第一pmos管的源极接电源,所述第三pmos管的漏极接所述第一nmos管的漏极,并作为第一反向器的输出,所述第三nmos管的源极接地,第二反向器包括依次串联的第四pmos管至第六pmos管以及依次串联的第四nmos管至第六nmos管,所述第四pmos管的源极接电源,所述第六pmos管的漏极接所述第四nmos管的漏极,并作为第二反向器的输出,所述第三nmos管的源极接地,所述第三pmos管的栅极与所述第三nmos管的栅极短接再接所述第二反向器的输出,所述第六pmos管的栅极与第六nmos管的栅极短接再接所述第一反向器的输出,其中,每个锁存结构的第一pmos管至第二nmos管的栅极还依次并分别连接其他每个锁存结构的第一pmos管至第二nmos管的不同栅极,每个锁存结构的第四pmos管至第五nmos管的栅极还依次并分别连接其他每个锁存结构的第四pmos管至第五nmos管的不同栅极;

5、所述穆勒单元具有五个输入端,分别接第一锁存结构的第一pmos管至第二nmos管的栅极;

6、所述第一传输门至第六传输门的输入端均相连接,并作为锁存器的数据输入端d,第一传输门至第五传输门与所述第一锁存结构的第四pmos管至第五nmos管的栅极一一连接,第六传输门的输出端与穆勒单元的输出端相连接,并作为锁存器的输出。

7、可选的,在所述的锁存器中,所述穆勒单元包括依次串联的第七pmos管至第十一pmos管以及依次串联的第七nmos管至第十一nmos管,所述第七pmos管的源极接电源,所述第十一nmos管的源极接地,所述第十一pmos管的漏极接第七nmos管的漏极,并作为穆勒单元的输出端,第七pmos管至第十一pmos管的栅极与第十一nmos管至第七nmos管的栅极一一连接并依次作为穆勒单元的五个输入端。

8、选的,在所述的锁存器中,所述穆勒单元的输入端的电平均一致时,则所述穆勒单元具为反相器功能,所述穆勒单元的输入端的电平不一致时,所述穆勒单元的输出呈高阻态。

9、选的,在所述的锁存器中,所述第一传输门至第六传输门的结构均相同。

10、选的,在所述的锁存器中,所述第一传输门至第六传输门控制端均输入时钟信号clk,第一传输门至第六传输门的反相控制端均输入时钟信号clkb。

11、选的,在所述的锁存器中,通过控制所述时钟信号clk,将锁存器分为传输和锁存两种工作模式。

12、选的,在所述的锁存器中,当时钟信号clk为高电平时,锁存器处于传输工作模式,输入信号传输到锁存器的输出端。

13、选的,在所述的锁存器中,当时钟信号clk为低电平时,锁存器处于锁存工作模式,输入数据存储在第一锁存结构至第五锁存结构中,锁存器的输出来源于第一锁存结构至第五锁存结构。

14、在本发明提供的锁存器中,抵抗了多个节点的单粒子干扰,降低多节点翻转在软错误中所占的比例。

技术特征:

1.一种锁存器,其特征在于,包括:

2.如权利要求1所述的锁存器,其特征在于,所述穆勒单元包括依次串联的第七pmos管至第十一pmos管以及依次串联的第七nmos管至第十一nmos管,所述第七pmos管的源极接电源,所述第十一nmos管的源极接地,所述第十一pmos管的漏极接第七nmos管的漏极,并作为穆勒单元的输出端,第七pmos管至第十一pmos管的栅极与第十一nmos管至第七nmos管的栅极一一连接并依次作为穆勒单元的五个输入端。

3.如权利要求2所述的锁存器,其特征在于,所述穆勒单元的输入端的电平均一致时,则所述穆勒单元具为反相器功能,所述穆勒单元的输入端的电平不一致时,所述穆勒单元的输出呈高阻态。

4.如权利要求1所述的锁存器,其特征在于,所述第一传输门至第六传输门的结构均相同。

5.如权利要求1所述的锁存器,其特征在于,所述第一传输门至第六传输门控制端均输入时钟信号clk,第一传输门至第六传输门的反相控制端均输入时钟信号clkb。

6.如权利要求5所述的锁存器,其特征在于,通过控制所述时钟信号clk,将锁存器分为传输和锁存两种工作模式。

7.如权利要求5所述的锁存器,其特征在于,当时钟信号clk为高电平时,锁存器处于传输工作模式,输入信号传输到锁存器的输出端。

8.如权利要求1所述的锁存器,其特征在于,当时钟信号clk为低电平时,锁存器处于锁存工作模式,输入数据存储在第一锁存结构至第五锁存结构中,锁存器的输出来源于第一锁存结构至第五锁存结构。

技术总结

本发明提供了一种锁存器,包括:第一至第五锁存结构和一个穆勒单元以及第一至第六传输门;每个锁存结构均由第一反向器和第二反向器组成,每个锁存结构的第一PMOS管至第二NMOS管的栅极依次并分别连接其他每个锁存结构的第一PMOS管至第二NMOS管的不同栅极,每个锁存结构的第四PMOS管至第五NMOS管的栅极还依次并分别连接其他每个锁存结构的第四PMOS管至第五NMOS管的不同栅极;穆勒单元具有五个输入端,分别接第一锁存结构的第一PMOS管至第二NMOS管的栅极;第一传输门至第六传输门的输入端均相连接,作为锁存器的数据输入端D,第六传输门的输出端与穆勒单元的输出端相连接,作为锁存器的输出。

技术研发人员:邱国际,潘炯

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/9/5

- 还没有人留言评论。精彩留言会获得点赞!