半导体器件及其制造方法以及电子系统与流程

本公开涉及半导体器件及其制造方法和电子系统。

背景技术:

1、在实施数据存储的电子系统中,半导体器件可以存储高容量数据。因此,正在研究增加半导体器件的数据存储容量的方法。作为增加半导体器件的数据存储容量的一种方法,已经提出了包括三维排列的存储单元而不是二维排列的存储单元的半导体器件。

技术实现思路

1、一些实施方式可以提供具有改善的可靠性和性能的半导体器件、其制造方法和电子系统。

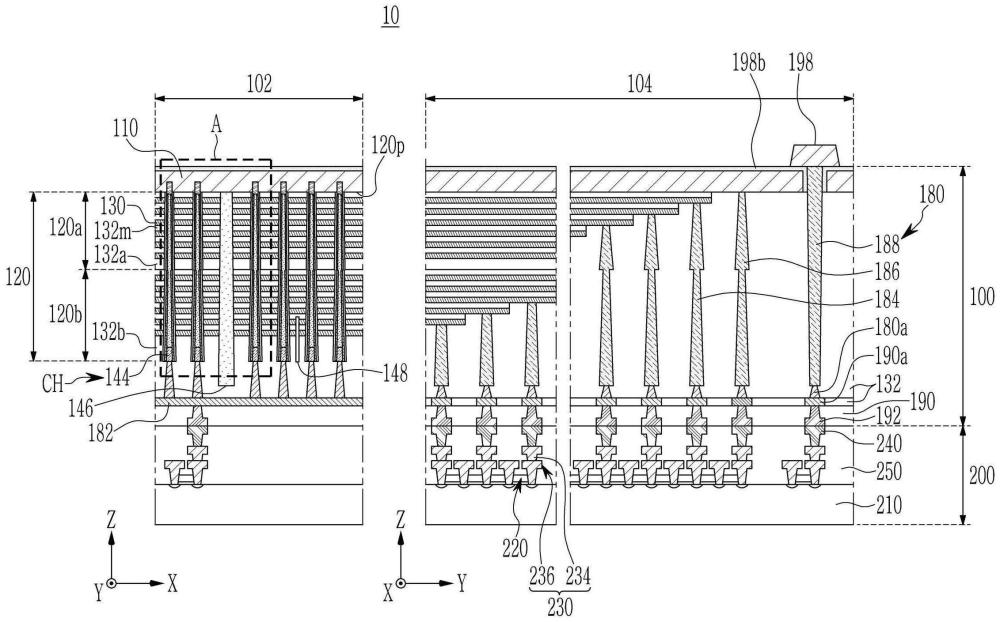

2、根据实施方式的半导体器件包括栅极堆叠结构、沟道结构和水平导电层。栅极堆叠结构可以包括交替堆叠的多个栅极电极和多个绝缘层。沟道结构可以提供有延伸到栅极堆叠结构中的内部部分和从栅极堆叠结构的一个表面突出的突出部分。水平导电层可以连接到沟道结构的突出部分。在这种情况下,沟道结构可以包括半导体层。半导体层可以包括多晶区和沟道区,多晶区至少在突出部分中并且包括多晶半导体材料,沟道区在内部部分中并且具有与多晶区的晶体结构不同的晶体结构。

3、根据实施方式的电子系统包括主衬底、在主衬底上的上述半导体器件以及在主衬底上的与半导体器件电连接的控制器。

4、根据实施方式的半导体器件的制造方法包括形成堆叠结构、形成初步沟道结构、形成半导体层和形成多个栅极电极。在堆叠结构的形成中,可以形成包括交替堆叠在衬底上的多个牺牲绝缘层和多个绝缘层的堆叠结构。在初步沟道结构的形成中,可以形成延伸到堆叠结构中的穿透部分,并且可以在穿透部分中形成包括初步半导体层的初步沟道结构,该初步半导体层包括非晶半导体材料。在半导体层的形成中,可以进行热处理工艺用于初步半导体层的结晶。在这种情况下,初步半导体层的第一区可以结晶以具有多晶结构,初步半导体层的第二区可以结晶以具有单晶结构或准单晶结构。在多个栅极电极的形成中,多个牺牲绝缘层可以用多个栅极电极替换。

5、根据实施方式,沟道结构中的损坏或缺陷可以通过包括具有多晶半导体材料的多晶区的半导体层减少或防止。此外,通过包括具有与多晶区的晶体结构不同的晶体结构的沟道区的半导体层,单元电流可以增加。因此,可以改善半导体器件的可靠性和性能。

6、根据实施方式,具有改进的可靠性和性能的半导体器件可以通过合理复杂性的工艺形成。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中所述沟道区具有单晶结构或准单晶结构。

3.根据权利要求1所述的半导体器件,其中所述沟道区包括沟道部分和在所述沟道部分与所述多晶区之间的界面部分,以及

4.根据权利要求3所述的半导体器件,其中所述界面部分包括金属,

5.根据权利要求3所述的半导体器件,其中所述沟道部分包括与所述多晶区相同的材料,以及

6.根据权利要求3所述的半导体器件,进一步包括:

7.根据权利要求1所述的半导体器件,其中所述沟道区包括沟道部分和在所述沟道部分与所述多晶区之间的界面部分,

8.根据权利要求1所述的半导体器件,其中所述多晶区在所述沟道结构的延伸方向上的高度大于所述沟道区在与所述沟道结构的侧表面交叉的方向上的厚度。

9.根据权利要求8所述的半导体器件,其中所述多晶区的所述高度与所述沟道区的所述厚度的比率为2或更大。

10.根据权利要求1所述的半导体器件,其中所述多晶区在所述沟道结构的延伸方向上的高度等于或大于所述多晶区的底表面在与所述延伸方向交叉的方向上的直径或宽度。

11.根据权利要求10所述的半导体器件,其中所述多晶区的所述高度与所述多晶区的所述底表面的所述直径或所述宽度的比率为1.5或更大。

12.根据权利要求1所述的半导体器件,其中所述多晶区在所述沟道结构的延伸方向上的高度等于或大于所述突出部分在所述沟道结构的所述延伸方向上的高度。

13.根据权利要求1所述的半导体器件,其中所述沟道区包括沟道部分以及在所述沟道部分和所述多晶区之间并包括金属的界面部分,以及

14.根据权利要求1所述的半导体器件,进一步包括在所述沟道区内部并在所述多晶区上的芯绝缘层。

15.根据权利要求1所述的半导体器件,其中所述沟道结构进一步包括至少部分地围绕所述内部部分中的所述半导体层的栅极电介质层以及在所述沟道区内部并在所述多晶区上的芯绝缘层,以及

16.根据权利要求1所述的半导体器件,进一步包括包含外围电路结构的电路区,

17.一种电子系统,包括:

18.一种半导体器件的制造方法,包括:

19.根据权利要求18所述的半导体器件的制造方法,进一步包括:

20.根据权利要求18所述的半导体器件的制造方法,其中,在所述初步沟道结构的形成中,所述初步沟道结构包括延伸到所述堆叠结构中的内部部分和从所述堆叠结构的一个表面突出的突出部分,以及

技术总结

本发明公开了一种半导体器件、包括半导体器件的电子系统、和半导体器件的制造方法。该半导体器件包括栅极堆叠结构、沟道结构和水平导电层。栅极堆叠结构可以包括交替堆叠的多个栅极电极和多个绝缘层。沟道结构可以提供有延伸到栅极堆叠结构中的内部部分和从栅极堆叠结构的一个表面突出的突出部分。水平导电层可以连接到沟道结构的突出部分。在这种情况下,沟道结构可以包括半导体层。半导体层可以包括多晶区和沟道区,多晶区至少在突出部分中并且包括多晶半导体材料,沟道区位于内部部分中并且具有与多晶区的晶体结构不同的晶体结构。

技术研发人员:梁时荣,金柳延,金载镐

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2025/1/6

- 还没有人留言评论。精彩留言会获得点赞!