量子芯片及其制备方法

本发明涉及超导电子学器件,尤其涉及一种量子芯片及其制备方法。

背景技术:

1、近年来,芯片的发展已经越来越接近半导体的物理极限,信息存储单元的尺寸将达到纳米量级,在纳米尺度的沟道中,电子的有效迁移变得困难,并且沟道表面的缺陷也会导致电荷散射,减缓电子流动速度,从而影响其表面迁移率,散热问题加剧,功耗迅速增加,限制了器件密度的进一步提升,使得无法保持摩尔定律所预测的发展速度和趋势。

2、为此,已提出了很多方案,其中,量子计算被认为是有巨大潜力的解决方案。1995年量子计算机被证明可大幅度提高大规模数据的搜索速度,量子计算机可由多个量子比特构建而成,目前超导量子比特被认为是具有潜力的量子比特载体之一。

3、目前的量子芯片主要存在以下缺陷,即难以构建一种可以处理大量量子比特同时保持稳定性和一致性的器件。除此之外,目前量子计算机的发展中,难以将多个量子比特耦合到计算系统中,也难以保持量子相干性。量子比特的相干性很容易受到环境噪声的影响,量子纠缠的建立和维持需要精密的控制技术等。

技术实现思路

1、有鉴于此,为解决上述技术问题中的至少之一,本发明提供了一种量子芯片及其制备方法,能够提高量子比特的退相干时间。

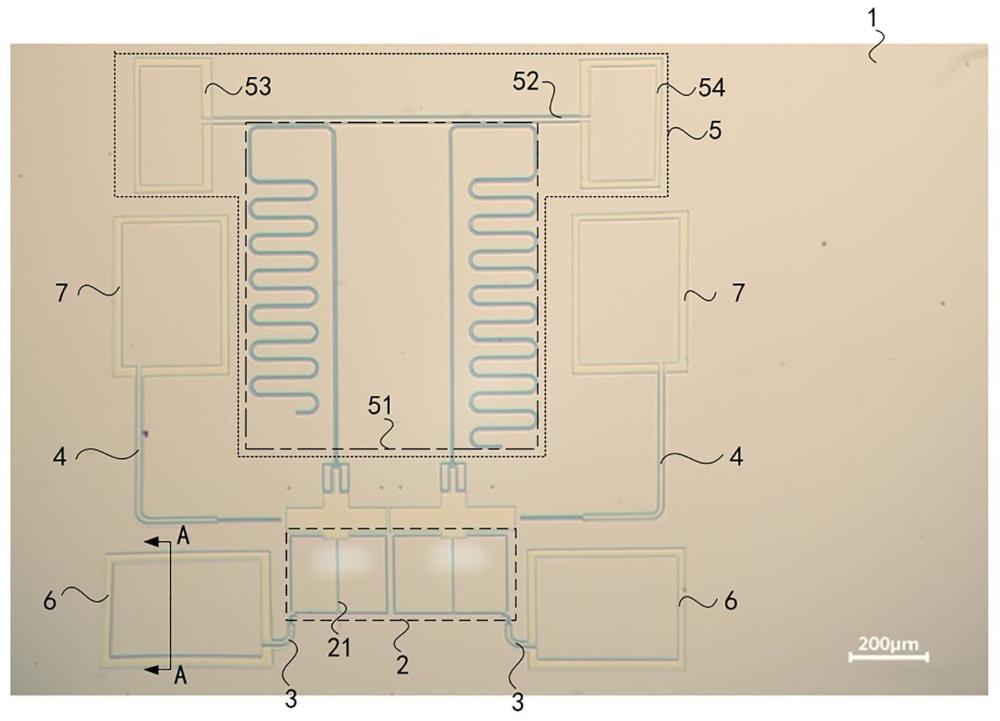

2、作为本发明的一个方面,提供了一种量子芯片,包括衬底、超导量子比特、偏置层和激励层。超导量子比特设置在上述衬底上,超导量子比特包括并联的两个约瑟夫森结。两个上述约瑟夫森结中的至少之一包括第一超导层和第二超导层。第二超导层与上述第一超导层在高度方向上形成间隙,上述间隙作为势垒层。偏置层设置在上述衬底上,与上述超导量子比特耦合,适用于传输来自外部的磁通偏置电压,上述磁通偏置电压适用于调控上述超导量子比特的频率,使上述超导量子比特处于工作频率。激励层设置在上述衬底上,与上述超导量子比特耦合,适用于传输来自外部的微波脉冲,上述微波脉冲适用于在上述工作频率下,驱动上述超导量子比特,使上述超导量子比特的能级跃迁,调控上述超导量子比特的量子态。

3、根据本发明的实施例,上述量子芯片还包括输出组件,输出组件设置在上述衬底上,与上述超导量子比特耦合,适用于将上述超导量子比特所处的量子态转换成电信号并输出。

4、根据本发明的实施例,上述输出组件包括谐振腔和检测层。谐振腔与上述超导量子比特耦合,以获取上述超导量子比特所处的量子态并转换成电信号,检测层与上述谐振腔耦合。其中,从上述检测层的第一端输入的电压信号,受到上述电信号的影响,从上述检测层的第二端输出响应信号,以基于上述电压信号与上述响应信号计算上述超导量子比特的量子态。

5、根据本发明的实施例,上述两个约瑟夫森结形成在上述衬底的第一部分上,上述衬底的第一部分具有第一区域和第二区域,其中第一区域向上延伸形成凸台,上述凸台的侧面与上述第二区域之间的夹角大于0°且小于等于90°,第一超导层设置在上述凸台上,第二超导层设置在上述第二区域上。其中,上述势垒层位于上述第一超导层和上述第二超导层之间,以在上述量子芯片处于超导转变温度以下的情况下,通过向上述第一超导层或上述第二超导层通入电流,使通入电流的超导层中的库珀对产生量子隧穿效应,穿过上述势垒层,进入到另一个超导层,形成约瑟夫森电流。

6、根据本发明的实施例,上述势垒层在竖直方向上的长度小于上述第一超导层和上述第二超导层所采用的超导材料的超导相干长度。

7、根据本发明的实施例,上述第一超导层和上述第二超导层为具有超导性质的金属或非金属材料。

8、根据本发明的实施例,上述第一超导层和上述第二超导层的表面粗糙度小于上述间隙的控制精度。

9、作为本发明实施例的另一个方面,提供了一种制备上述任一种量子芯片的制备方法,包括:

10、在具有第一部分和第二部分的衬底的第二部分上和上述第一部分的第一区域上曝光出偏置层图形和激励层图形;

11、在上述第二部分和上述第一部分的第一区域上沉积掩膜;

12、对上述衬底的第一部分的第二区域向下刻蚀,以形成具有阶梯结构的第一衬底;

13、去除第一衬底上的上述掩膜;

14、在上述偏置层图形和上述激励层图形上生长超导材料,形成偏置层和激励层;以及

15、在上述第一部分的第一区域和第二区域上再次生长超导材料,以同时形成第一超导层和第二超导层,并使上述第一超导层与上述第二超导层之间形成间隙作为势垒层,以形成两个约瑟夫森结。

16、根据本发明的实施例,上述在上述偏置层图形和上述激励层图形上生长超导材料,形成偏置层和激励层中,生长的超导材料的厚度能够使位于上述阶梯结构上侧与下侧的超导材料之间的距离大于超导材料的超导相干长度,使外围区域通过上述阶梯结构与上述偏置层图形和上述激励层断开。

17、根据本发明的实施例,上述第一部分具有并列设置的第一约瑟夫森结区域和第二约瑟夫森结区域,每个约瑟夫森结区域包括一个第一区域和一个第二区域,通过在每个约瑟夫森结区域的第一区域和第二区域上生长超导材料,形成两个约瑟夫森结。

18、根据本发明实施例的量子芯片,将两个并联的约瑟夫森结设置在衬底上,形成超导量子比特,并通过偏置层传输磁通偏置电压来调控超导量子比特,使超导量子比特处于工作频率,进一步通过激励层传输微波脉冲,驱动超导量子比特,使超导量子比特的能级跃迁,调控超导量子比特的量子态,实现信息的读取和写入。

19、本发明提供的量子芯片的制备方法,简化了传统的制备量子芯片的方法,能够通过控制沉积超导材料的不同厚度,分别制备出约瑟夫森结部分和量子芯片的其他电路部分,是一种简单易行制的器件制备工艺,可制备出大量高稳定性和高一致性的量子比特,并为提高量子比特连通性、栅极保真度、增加相干时间等作出贡献。

技术特征:

1.一种量子芯片,其特征在于,包括:

2.根据权利要求1所述的量子芯片,其特征在于,还包括:

3.根据权利要求2所述的量子芯片,其特征在于,所述输出组件包括:

4.根据权利要求1所述的量子芯片,其特征在于,两个所述约瑟夫森结形成在所述衬底的第一部分上,所述衬底的第一部分具有第一区域和第二区域,其中第一区域向上延伸形成凸台,所述凸台的侧面与所述第二区域之间的夹角的范围大于0°且小于等于90°,所述第一超导层设置在所述凸台上;所述第二超导层设置在所述第二区域上;

5.根据权利要求4所述的量子芯片,其特征在于,所述势垒层在竖直方向上的长度小于所述第一超导层和所述第二超导层所采用的超导材料的超导相干长度。

6.根据权利要求4所述的量子芯片,其特征在于,所述第一超导层和所述第二超导层为具有超导性质的金属或非金属材料。

7.根据权利要求4所述的量子芯片,其特征在于,所述第一超导层和所述第二超导层的表面粗糙度小于所述间隙的控制精度。

8.一种制备权利要求1-7中任一项所述的量子芯片的制备方法,其特征在于,包括:

9.根据权利要求8所述的制备方法,其特征在于,所述在所述偏置层图形和所述激励层图形上生长超导材料,形成偏置层和激励层中,生长的超导材料的厚度能够使位于所述阶梯结构上侧与下侧的超导材料之间的距离大于超导材料的超导相干长度,使外围区域通过所述阶梯结构与所述偏置层图形和所述激励层断开。

10.根据权利要求8所述的制备方法,其特征在于,所述第一部分具有并列设置的第一约瑟夫森结区域和第二约瑟夫森结区域,每个约瑟夫森结区域包括一个第一区域和一个第二区域,通过在每个约瑟夫森结区域的第一区域和第二区域上生长超导材料,形成两个约瑟夫森结。

技术总结

本发明提供了一种量子芯片及其制备方法。量子芯片包括衬底、超导量子比特、偏置层和激励层。超导量子比特设置在衬底上,超导量子比特包括并联两个约瑟夫森结。两个约瑟夫森结中的至少之一包括第一超导层;第二超导层与第一超导层在高度方向上形成间隙,间隙作为势垒层;偏置层设置在衬底上,与超导量子比特耦合,用于传输来自外部的磁通偏置电压,磁通偏置电压用于调控超导量子比特的频率,使超导量子比特处于工作频率。激励层设置在衬底上,与超导量子比特耦合,用于传输自外部的微波脉冲,微波脉冲用于在工作频率下,驱动超导量子比特,调控超导量子比特的量子态。

技术研发人员:马雷,张凯敏,郝路珍,田昊

受保护的技术使用者:天津大学

技术研发日:

技术公布日:2024/6/18

- 还没有人留言评论。精彩留言会获得点赞!