一种半导体结构中的通孔的制作方法及半导体工艺设备与流程

本申请涉及半导体,具体涉及一种半导体结构中的通孔的制作方法及半导体工艺设备。

背景技术:

1、在3dnand领域,刻蚀沟道孔(channelhole)前,首先要在沟道层上形成碳掩膜层,然后以硅氧化物为掩膜,在碳掩膜层上形成用于刻蚀沟道孔的过孔(hardmaskopen,简称hmo),该工艺过程简称为chhmo。

2、hmo为具有高深宽比的通孔,因此需要采用高深宽比刻蚀工艺,即,使得等离子体在较深深度下依然能保持良好的各向异性,以及可以将等离子体自由基输送到刻蚀尖端。但是该工艺过程也同时会对硅氧化物形成较强的物理轰击而产生硅氧化物的刻蚀副产物,副产物溅射到硅氧化物掩膜孔的顶部,使得硅氧化物掩膜孔的孔径随着刻蚀的进行逐渐变小,即发生颈缩,严重时甚至发生硅氧化物掩膜孔的顶部堵塞,阻碍对碳掩膜层的刻蚀,此现象也被称为“clogging”。

技术实现思路

1、针对上述技术问题,本申请提供一种半导体结构中的通孔的制作方法及半导体工艺设备,可以延缓chhmo工艺中硅氧化物掩膜孔阻塞。

2、为解决上述技术问题,第一方面,本申请实施例提供一种半导体结构中的通孔的制作方法,所述半导体结构包括:含碳层,层叠于所述含碳层上方的硅氧化物层,以及位于所述硅氧化物层上图形化的第一掩膜层,所述制作方法包括:

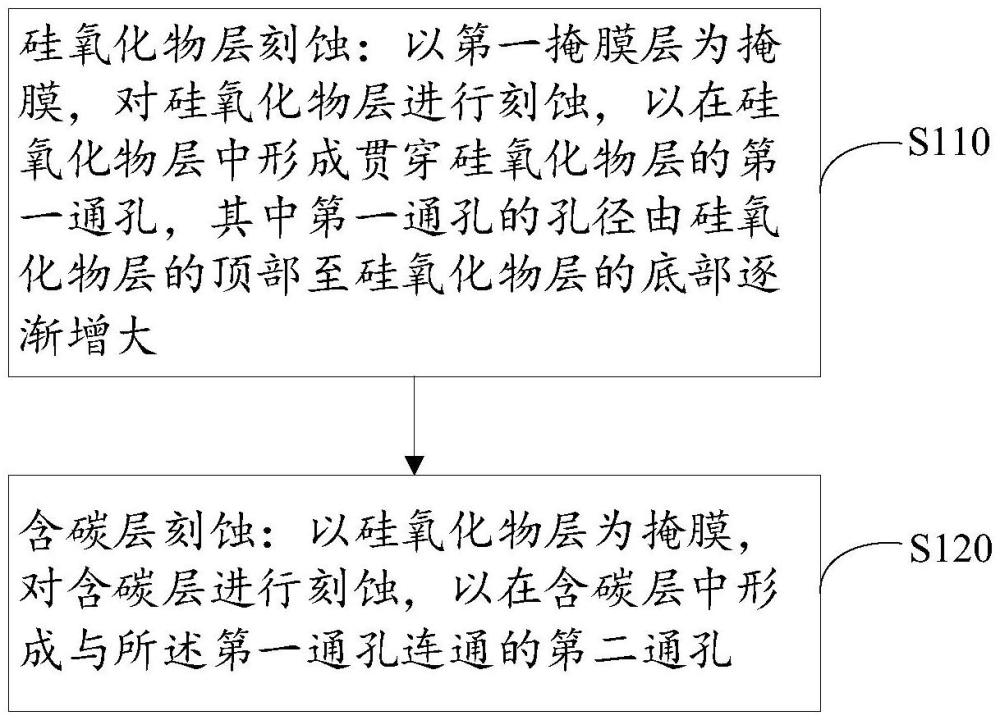

3、硅氧化物层刻蚀:以所述第一掩膜层为掩膜,对所述硅氧化物层进行刻蚀,以在所述硅氧化物层中形成贯穿所述硅氧化物层的第一通孔,其中所述第一通孔的孔径由所述硅氧化物层的顶部至所述硅氧化物层的底部逐渐增大;

4、含碳层刻蚀:以所述硅氧化物层为掩膜,对所述含碳层进行刻蚀,以在所述含碳层中形成与所述第一通孔连通的第二通孔。

5、可选的,所述硅氧化物层刻蚀的步骤包括:

6、主刻蚀:以所述第一掩膜层为掩膜,在第一腔室压力下,采用含c、h、f元素的气体和sf6的混合气体对所述硅氧化物层进行刻蚀,刻蚀的深度h满足:0.9t≤h≤t,其中,t为所述硅氧化物层的厚度,所述混合气体中s元素和h元素的比例为1:(3~4);

7、过刻蚀:在第二腔室压力下,采用所述混合气体继续刻蚀预设时间,以使刻蚀停止在所述含碳层的表面,其中所述第二腔室压力大于所述第一腔室压力。

8、可选的,所述第一腔室压力为10~30mt,所述第二腔室压力为30~50mt。

9、可选的,所述含c、h、f元素的气体为ch2f2和/或ch3f。

10、可选的,所述含c、h、f元素的气体为ch2f2;

11、所述sf6与所述ch2f2的流量比为1/2~2/3。

12、可选的,所述sf6的流量为20~30sccm,所述ch2f2的流量为40~60sccm。

13、可选的,根据调整公式设置所述sf6的流量以使所述第一通孔的顶部直径符合预设值,所述调整公式为:

14、△d=(0.5~1.0)△f/0.1,

15、其中,△d为所述第一通孔的顶部直径的变化值,△f为所述sf6的流量变化。

16、可选的,所述主刻蚀的工艺条件为:上电极加载的射频功率为800~1500w,下电极加载的射频功率为50~200w;和/或,

17、所述过刻蚀的工艺条件为:上电极加载的射频功率为800~1500w,下电极加载的射频功率为50~200w;

18、所述主刻蚀时所述下电极加载的射频功率大于或等于所述过刻蚀时所述下电极加载的射频功率。

19、可选的,所述过刻蚀的刻蚀时间t2满足:0.3t1≤t2≤0.4t1,其中,t1为所述主刻蚀的刻蚀时间。

20、第二方面,本申请实施例还提供一种半导体工艺设备,包括工艺腔室、进气组件、上电极组件、下电极组件和控制器,所述控制器包括至少一个处理器和至少一个存储器,所述存储器中存储有计算机程序,所述计算机程序被所述处理器执行时实现如上各实施例所述的制作方法。

21、如上所述,本申请的半导体结构中制作通孔的方法中,首先以第一掩膜层为掩膜,对硅氧化物层进行刻蚀,以在硅氧化物层中形成贯穿硅氧化物层的第一通孔,其中第一通孔的孔径由硅氧化物层的顶部至硅氧化物层的底部逐渐增大;然后以硅氧化物层为掩膜对含碳层进行刻蚀,由于硅氧化物层本身会有少量的消耗,硅氧化物层形成的刻蚀副产物附着在第一通孔的侧壁上。由于第一通孔为正梯形,随着硅氧化物层高度的消耗,第一通孔的孔径在逐渐变大,逐渐增大的量抵消了因刻蚀副产物的堵塞本应逐渐缩小的量,从而推迟了硅氧化物层的第一通孔堵塞的时间,提高了含碳层刻蚀的时间;同时,因第一通孔底部的孔径较大,刻蚀含碳层的过程中,被溅射堆积在第一通孔侧壁的刻蚀副产物会填补在第一通孔孔径较大的底部,即孔径较大的底部可以容纳更多的刻蚀副产物,进一步延长了第一通孔堵塞的时间。由此,可以减少chhmo刻蚀过程中使用bt工艺的次数,从而刻蚀完成后,含碳层中的第二通孔顶部的弓形轮廓直径也较小,可以提高后续刻蚀沟道孔时图形传递的精度。

技术特征:

1.一种半导体结构中的通孔的制作方法,其特征在于,所述半导体结构包括:含碳层,层叠于所述含碳层上方的硅氧化物层,以及位于所述硅氧化物层上图形化的第一掩膜层,所述制作方法包括:

2.根据权利要求1所述的制作方法,其特征在于,所述硅氧化物层刻蚀的步骤包括:

3.根据权利要求2所述的制作方法,其特征在于,所述第一腔室压力为10~30mt,所述第二腔室压力为30~50mt。

4.根据权利要求2所述的制作方法,其特征在于,所述含c、h、f元素的气体为ch2f2和/或ch3f。

5.根据权利要求4所述的制作方法,其特征在于,所述含c、h、f元素的气体为ch2f2;

6.根据权利要求5所述的制作方法,其特征在于,所述sf6的流量为20~30sccm,所述ch2f2的流量为40~60sccm。

7.根据权利要求6所述的制作方法,其特征在于,所述主刻蚀中,根据调整公式设置所述sf6的流量以使所述第一通孔的顶部直径符合预设值,所述调整公式为:

8.根据权利要求2所述的制作方法,其特征在于,所述主刻蚀的工艺条件为:上电极加载的射频功率为800~1500w,下电极加载的射频功率为50~200w;和/或,

9.根据权利要求2所述的制作方法,其特征在于,所述过刻蚀的刻蚀时间t2满足:0.3t1≤t2≤0.4t1,其中,t1为所述主刻蚀的刻蚀时间。

10.一种半导体工艺设备,包括工艺腔室、进气组件、上电极组件、下电极组件和控制器,其特征在于,所述控制器包括至少一个处理器和至少一个存储器,所述存储器中存储有计算机程序,所述计算机程序被所述处理器执行时实现如权利要求1-9中任一项所述的制作方法。

技术总结

本申请公开了一种半导体结构中的通孔的制作方法及半导体工艺设备,制作方法包括:含碳层,层叠于含碳层上方的硅氧化物层,以及位于硅氧化物层上图形化的第一掩膜层,制作方法包括:硅氧化物层刻蚀:以第一掩膜层为掩膜,对硅氧化物层进行刻蚀,以在硅氧化物层中形成贯穿硅氧化物层的第一通孔,其中第一通孔的孔径由硅氧化物层的顶部至硅氧化物层的底部逐渐增大;含碳层刻蚀:以硅氧化物层为掩膜,对含碳层进行刻蚀,以在含碳层中形成与第一通孔连通的第二通孔。本申请可以推迟硅氧化物层的第一通孔堵塞的时间,还可以减小含碳层中的第二通孔顶部的弓形轮廓直径,从而可以提高后续刻蚀沟道孔时图形传递的精度。

技术研发人员:郭方敏,徐士楠,钦辉,李豫豪

受保护的技术使用者:北京北方华创微电子装备有限公司

技术研发日:

技术公布日:2024/9/9

- 还没有人留言评论。精彩留言会获得点赞!