信号整形电路、时钟信号产生电路、芯片及电子设备的制作方法

本申请涉及集成电路,具体涉及一种信号整形电路、时钟信号产生电路、芯片及电子设备。

背景技术:

1、时钟信号是时序逻辑的基础,以保证相关的电子组件得以同步/按序运作。其中,时钟信号的边沿决定了接收时钟信号的对象状态发生改变的时刻,因此上升沿以及下降沿的持续时间成为了时钟信号的重要指标。

2、在相关技术中,对时钟信号进行整形可以获取上升沿以及下降沿持续时间较短的时钟信号,例如采用反相器或者施密特触发器对时钟信号进行整形。然而,当时钟信号的电压在vdd/2附近时,反相器中的pmos管和nmos管将会同时导通,使得从电源端到接地端的通路会被导通,最终产生较大的电源到地的电流以及功耗,这导致了信号整形电路功耗增大的问题。

技术实现思路

1、鉴于以上问题,本申请实施例提供一种信号整形电路、时钟信号产生电路、芯片及电子设备,以解决上述技术问题。

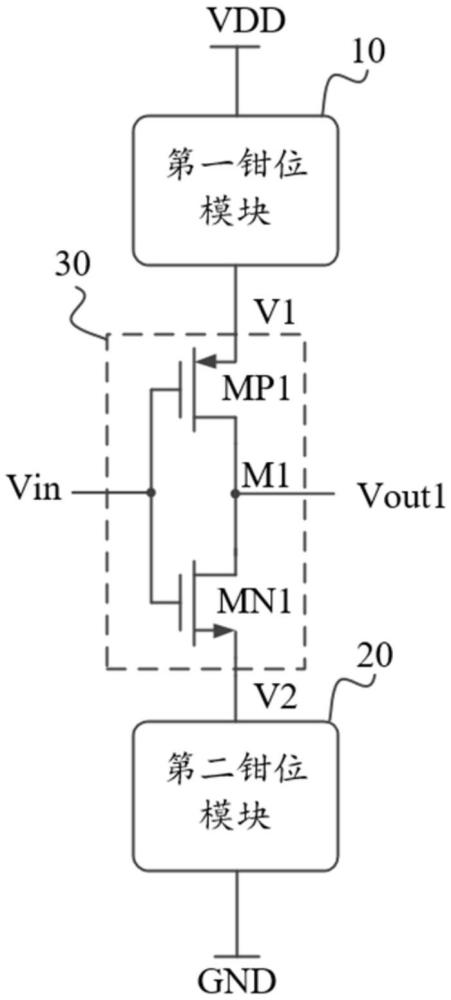

2、第一方面,本申请实施例提供一种信号整形电路,包括:

3、第一钳位模块,第一钳位模块用于根据电源端电压输出第一钳位电压;

4、第二钳位模块,第二钳位模块用于根据接地端电压输出第二钳位电压;

5、第一反相模块,第一反相模块包括至少一个第一低电位导通晶体管以及至少一个第一高电位导通晶体管,第一低电位导通晶体管的第一端接入第一钳位电压,第一高电位导通晶体管的第一端接入第二钳位电压;

6、第一低电位导通晶体管和第一高电位导通晶体管的控制端接入输入电压信号,第一低电位导通晶体管的第二端与第一高电位导通晶体管的第二端相互连接,第一低电位导通晶体管与第一高电位导通晶体管之间的第一节点用于输出第一输出电压信号;

7、其中,第一钳位电压小于电源端电压,第二钳位电压大于接地端电压,且在信号整形电路工作过程中的任一时刻,第一钳位模块、第二钳位模块以及第一反相模块对应于电源端与接地端之间通路保持断开状态。

8、第二方面,本申请提供一种时钟信号产生电路,包括:

9、参考电压产生电路,参考电压产生电路用于产生参考电压;

10、电容充放电电路,电容充放电电路进行充放电并输出比较电压;

11、比较电路,比较电路用于对比比较电压与参考电压并输出比较信号;

12、如第一方面所述的信号整形电路,信号整形电路用于对比较信号整形并输出时钟信号;

13、逻辑电路,逻辑电路用于根据时钟信号控制电容充放电电路进行充放电。

14、第三方面,本申请提供一种芯片,包括如第二方面所述的时钟信号产生电路。

15、第四方面,本申请提供一种电子设备,包括如第三方面所述的芯片。

16、在本申请中,第一钳位模块向第一低电位导通晶体管的第一端输入第一钳位电压,第一低电位导通晶体管的控制端接入输入电压信号,由于第一钳位电压小于电源端电压,对于第一低电位导通晶体管而言,意味着输入电压信号的电压需要降低至更小值才能让第一低电位导通晶体管导通;同时,第二钳位模块向第一高电位导通晶体管的第一端输入第二钳位电压,第一高电位导通晶体管的控制端接入输入电压信号,由于第二钳位电压大于接地端电压,对于第一高电位导通晶体管而言,意味着输入电压信号的电压需要升高至更大值才能让第一高电位导通晶体管导通。也就是说,本申请通过降低第一低电位导通晶体管导通时输入电压信号的电压值,并抬高第一高电位导通晶体管导通时输入电压信号的电压值,可以避免第一低电位导通晶体管以及第一高电位导通晶体管同时导通的现象,进而在信号整形电路工作过程中的任一时刻,第一钳位模块、第二钳位模块以及第一反相模块对应于电源端与接地端之间通路保持断开状态,最终有利于降低信号整形电路的功耗以及电子设备的发热量。

17、本申请的这些方面或其他方面在以下实施例的描述中会更加简明易懂。

技术特征:

1.一种信号整形电路,其特征在于,包括:

2.如权利要求1所述的信号整形电路,其特征在于,当所述输入电压信号的电压大于或等于第一预设值时,所述第一高电位导通晶体管处于导通状态,所述第一低电位导通晶体管处于截止状态;

3.如权利要求1所述的信号整形电路,其特征在于,所述第一钳位模块包括多个串联的第一钳位晶体管,所述第二钳位模块包括多个串联的第二钳位晶体管;

4.如权利要求1所述的信号整形电路,其特征在于,所述第一钳位模块包括多个串联的第一二极管,所述第二钳位模块包括多个串联的第二二极管。

5.如权利要求1所述的信号整形电路,其特征在于,所述信号整形电路还包括第二反相模块,所述第二反相模块包括第二低电位导通晶体管以及第二高电位导通晶体管;

6.如权利要求5所述的信号整形电路,其特征在于,所述信号整形电路还包括第一反馈模块以及第二反馈模块;

7.如权利要求6所述的信号整形电路,其特征在于,所述第一反馈模块包括第三低电位导通晶体管,所述第二反馈模块包括第三高电位导通晶体管;

8.一种时钟信号产生电路,其特征在于,包括:

9.一种芯片,其特征在于,包括如权利要求8所述的时钟信号产生电路。

10.一种电子设备,其特征在于,包括如权利要求9所述的芯片。

技术总结

本申请提供一种信号整形电路、时钟信号产生电路、芯片及电子设备,信号整形电路包括:第一钳位模块,第一钳位模块用于根据电源端电压输出第一钳位电压;第二钳位模块,第二钳位模块用于根据接地端电压输出第二钳位电压;第一反相模块,第一反相模块包括至少一个第一端接入第一钳位电压的第一低电位导通晶体管以及至少一个第一端接入第二钳位电压的第一高电位导通晶体管。本申请在信号整形电路工作过程中的任一时刻,第一钳位模块、第二钳位模块以及第一反相模块对应于电源端与接地端之间通路保持断开状态,最终有利于降低信号整形电路的功耗以及电子设备的发热量。

技术研发人员:黄振宇,叶学锋,刘帅锋

受保护的技术使用者:合肥市芯海电子科技有限公司

技术研发日:

技术公布日:2024/8/20

- 还没有人留言评论。精彩留言会获得点赞!