一种半导体结构及其制备方法与流程

本公开涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、阻变式随机存取存储器(resistive random access memory,rram)是一种利用材料的可变电阻特性来存储信息的非易失性(non-volatile)存储器,具有功耗低、密度高、读写速度快、耐久性好等优点。

2、现有的存储阵列中,大多采用2t2r的结构,即包括两个晶体管(transistor)和两个阻变式随机存取存储器(rram),但是现有的结构中,一个2t2r结构中的两个rram连接同一条位线,这样由于操作时均是对单个rram进行操作,此时另一个晶体管就会面临高漏电压导致的击穿风险。

技术实现思路

1、本公开提供了一种半导体结构及其制备方法,以至少解决现有技术中存在的以上技术问题。

2、根据本公开的第一方面,提供了一种半导体结构,所述半导体结构包括:

3、衬底;

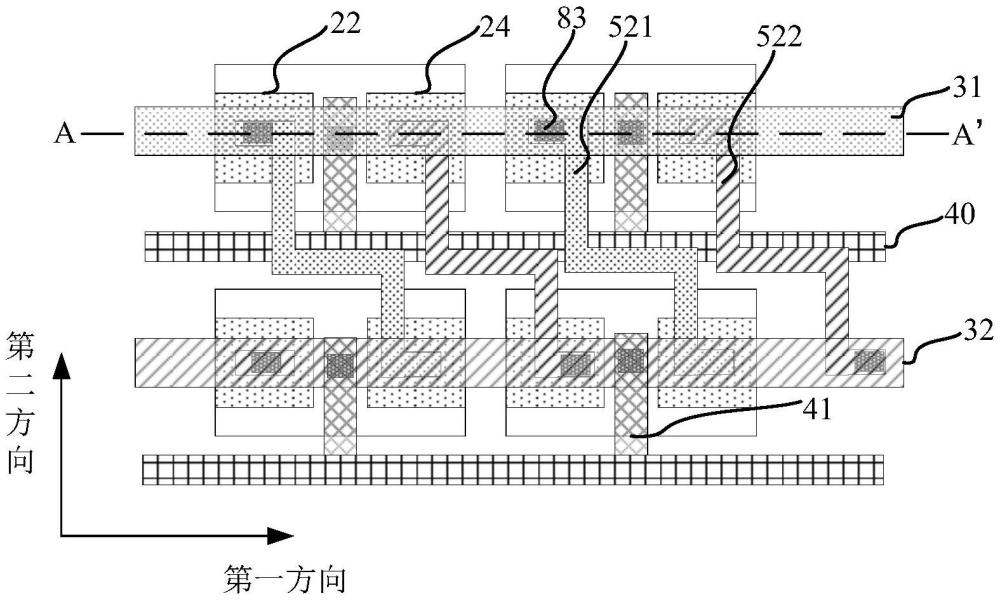

4、多个沿第一方向和第二方向排列的存储单元,每个存储单元包括第一晶体管和与所述第一晶体管连接的第一忆阻器,以及第二晶体管和与所述第二晶体管连接的第二忆阻器;其中,所述第一方向和所述第二方向为平行于所述衬底平面的方向,所述第一方向和所述第二方向相交;

5、多条沿所述第一方向延伸的第一位线和多条沿所述第一方向延伸的第二位线,其中,每相邻两排沿所述第一方向排列的所述存储单元中,第一排中的全部所述第一忆阻器和第二排中的全部所述第二忆阻器与同一条所述第一位线连接,第一排中的全部所述第二忆阻器和第二排中的全部所述第一忆阻器与同一条所述第二位线连接。

6、在一可实施方式中,还包括:

7、多条沿所述第一方向延伸的源极线,其中,同一排沿所述第一方向延伸的所述存储单元中,全部所述第一晶体管和全部所述第二晶体管与同一条源极线连接。

8、在一可实施方式中,还包括:

9、第一导电连接层,位于所述第一忆阻器和所述第二忆阻器上,与所述第一忆阻器和所述第二忆阻器电连接;

10、第二导电连接层,位于所述第一导电连接层上,所述第二导电连接层包括第一子导电连接层和第二子导电连接层;其中,每相邻两排沿所述第一方向排列的所述存储单元中,第一排中的所述第一忆阻器和第二排中的与第一排的所述第一忆阻器呈对角分布的所述第二忆阻器通过所述第一子导电连接层电连接,第一排中的所述第二忆阻器和第二排中的与第一排的所述第二忆阻器呈对角分布的所述第一忆阻器通过所述第二子导电连接层电连接。

11、在一可实施方式中,所述第一位线位于所述第一子导电连接层上,与所述第一子导电连接层电连接;

12、所述第二位线位于所述第二子导电连接层上,与所述第二子导电连接层电连接。

13、在一可实施方式中,还包括:

14、多条沿所述第二方向延伸的第一字线和多条沿所述第二方向延伸的第二字线,其中,同一排沿所述第二方向排列的全部第一晶体管与所述第一字线连接,同一排沿所述第二方向排列的全部第二晶体管与所述第二字线连接。

15、根据本公开的第二方面,提供了一种半导体结构的制备方法,所述方法包括:

16、提供衬底;

17、形成多个沿第一方向和第二方向排列的存储单元,每个存储单元包括第一晶体管和与所述第一晶体管连接的第一忆阻器,以及第二晶体管和与所述第二晶体管连接的第二忆阻器;其中,所述第一方向和所述第二方向为平行于所述衬底平面的方向,所述第一方向和所述第二方向相交;

18、形成多条沿所述第一方向延伸的第一位线和多条沿所述第一方向延伸的第二位线,其中,每相邻两排沿所述第一方向排列的所述存储单元中,第一排中的全部所述第一忆阻器和第二排中的全部所述第二忆阻器与同一条所述第一位线连接,第一排中的全部所述第二忆阻器和第二排中的全部所述第一忆阻器与同一条所述第二位线连接。

19、在一可实施方式中,还包括:

20、在形成所述第一位线和所述第二位线之前,形成多条沿所述第一方向延伸的源极线,其中,同一排沿所述第一方向延伸的所述存储单元中,全部所述第一晶体管和全部所述第二晶体管与同一条源极线连接。

21、在一可实施方式中,还包括:

22、在形成所述第一位线和所述第二位线之前,形成位于所述第一忆阻器和所述第二忆阻器上的第一导电连接层,所述第一导电连接层与所述第一忆阻器和所述第二忆阻器电连接;

23、形成位于所述第一导电连接层上的第二导电连接层,所述第二导电连接层包括第一子导电连接层和第二子导电连接层;其中,每相邻两排沿所述第一方向排列的所述存储单元中,第一排中的所述第一忆阻器和第二排中的与第一排的所述第一忆阻器呈对角分布的所述第二忆阻器通过所述第一子导电连接层电连接,第一排中的所述第二忆阻器和第二排中的与第一排的所述第二忆阻器呈对角分布的所述第一忆阻器通过所述第二子导电连接层电连接。

24、在一可实施方式中,所述第一位线位于所述第一子导电连接层上,与所述第一子导电连接层电连接;

25、所述第二位线位于所述第二子导电连接层上,与所述第二子导电连接层电连接。

26、在一可实施方式中,还包括:

27、在形成所述第一位线和所述第二位线之前,形成多条沿所述第二方向延伸的第一字线和多条沿所述第二方向延伸的第二字线,其中,同一排沿所述第二方向排列的全部第一晶体管与所述第一字线连接,同一排沿所述第二方向排列的全部第二晶体管与所述第二字线连接。

28、本公开的半导体结构及其制备方法,每个存储单元中的第一忆阻器和第二忆阻器连接不同位线,因此可以分别控制两条位线的电压,可以较大程度避免在进行启动操作时,相邻晶体管在共用源极线带来的高漏电压造成的击穿风险,降低相邻晶体管漏电情况;同时每相邻两排沿第一方向排列的存储单元中,第一排中的全部第一忆阻器和第二排中的全部第二忆阻器与同一条第一位线连接,第一排中的全部第二忆阻器和第二排中的全部第一忆阻器与同一条第二位线连接,因此两排存储单元中,仍然只需要形成两条位线,器件的单元面积没有增加,阵列密度不变。

29、应当理解,本部分所描述的内容并非旨在标识本公开的实施例的关键或重要特征,也不用于限制本公开的范围。本公开的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种半导体结构,其特征在于,所述半导体结构包括:

2.根据权利要求1所述的半导体结构,其特征在于,还包括:

3.根据权利要求1所述的半导体结构,其特征在于,还包括:

4.根据权利要求3所述的半导体结构,其特征在于,

5.根据权利要求1所述的半导体结构,其特征在于,还包括:

6.一种半导体结构的制备方法,其特征在于,所述方法包括:

7.根据权利要求6所述的方法,其特征在于,还包括:

8.根据权利要求6所述的方法,其特征在于,还包括:

9.根据权利要求8所述的方法,其特征在于,

10.根据权利要求6所述的方法,其特征在于,还包括:

技术总结

本公开提供了一种半导体结构及其制备方法,其中,半导体结构包括:衬底;多个沿第一方向和第二方向排列的存储单元,每个存储单元包括第一晶体管和与所述第一晶体管连接的第一忆阻器,以及第二晶体管和与所述第二晶体管连接的第二忆阻器;其中,所述第一方向和所述第二方向为平行于所述衬底平面的方向,所述第一方向和所述第二方向相交;多条沿所述第一方向延伸的第一位线和多条沿所述第一方向延伸的第二位线,其中,每相邻两排沿所述第一方向排列的所述存储单元中,第一排中的全部所述第一忆阻器和第二排中的全部所述第二忆阻器与同一条所述第一位线连接,第一排中的全部所述第二忆阻器和第二排中的全部所述第一忆阻器与同一条所述第二位线连接。

技术研发人员:刘华仪,李文明,陈昱煌,尹家宇,潘天龙

受保护的技术使用者:厦门半导体工业技术研发有限公司

技术研发日:

技术公布日:2024/9/9

- 还没有人留言评论。精彩留言会获得点赞!