一种线路板局部表面处理工艺的制作方法

本发明涉及pcb表面处理,特别涉及一种线路板局部表面处理工艺。

背景技术:

1、pcb表面处理工艺包括镀金,镀金一般发生在焊盘都留有露出铜的空间或者金手指上,当同一个pcb设计中有局部镀硬金加其他位置喷锡,并且在镀金位置无法拉镀金导线且需要在镀金位置四周包金时,行业内基本做法为局部镀硬金位置四周不包金,用其他镀金方式可以实现镀硬金,但是会造成硬金金厚不足和焊盘都留有露出铜的空间四周无法包金,主要原因为局部镀金焊盘都留有露出铜的空间位置受焊盘都留有露出铜的空间间距影响,无法拉镀金导线,如无法设计导线则无法实现镀硬金要求的金厚,影响产品质量。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提出一种线路板局部表面处理工艺,能够在局部镀硬金和其他位置喷锡同时存在的情况下进行镀金并且四周包金,不受焊盘都留有露出铜的空间间距影响。

2、根据本发明的第一方面实施例的一种线路板局部表面处理工艺,包括下列步骤:

3、前制程,对pcb进行包括压合、钻孔、树脂塞孔、钻非塞孔金属化孔、沉铜板镀的工艺操作,然后将需要蚀刻焊盘都留有露出铜的空间的一面定义为cs面都留有露出铜的空间,另一面定义为ss面都留有露出铜的空间;

4、一次蚀刻,对cs面都留有露出铜的空间进行显影蚀刻,形成焊盘都留有露出铜的空间,ss面都留有露出铜的空间不进行操作,ss面都留有露出铜的空间与焊盘都留有露出铜的空间电性导通;

5、开窗,对ss面都留有露出铜的空间和cs面都留有露出铜的空间贴干膜,显影后洗脱cs面都留有露出铜的空间上的部分干膜,使得cs面都留有露出铜的空间露出焊盘都留有露出铜的空间需要镀金的位置;

6、cs面都留有露出铜的空间镀金,将ss面都留有露出铜的空间作为导电部分与cs面都留有露出铜的空间上的焊盘都留有露出铜的空间接通,在电镀的时候将cs面都留有露出铜的空间上的焊盘都留有露出铜的空间表面及四周电镀上金层,免去在cs面都留有露出铜的空间上的焊盘都留有露出铜的空间拉镀金导线;

7、退干膜,将cs面都留有露出铜的空间和ss面都留有露出铜的空间的干膜完全褪去,使得ss面都留有露出铜的空间的铜面显露;

8、二次蚀刻,对ss面都留有露出铜的空间的铜面进行蚀刻,完成整张pcb的线路蚀刻。

9、根据本发明实施例的一种线路板局部表面处理工艺,至少具有如下有益效果:将需要蚀刻的两面分为cs面都留有露出铜的空间和ss面都留有露出铜的空间,cs面都留有露出铜的空间和ss面都留有露出铜的空间在时间上错开处理,利用ss面都留有露出铜的空间作为cs面都留有露出铜的空间上焊盘都留有露出铜的空间的镀金导线,可以解决针对设计局部镀硬金加其他位置喷锡,在镀金位置无法拉镀金导线且需要四周包金的困难。pcb的顶层命名为cs面都留有露出铜的空间、pcb的底层命名为ss面都留有露出铜的空间;局部镀金且要求焊盘都留有露出铜的空间四周包金位置不设计镀金导线,采用ss面都留有露出铜的空间非镀金面作为cs面都留有露出铜的空间镀金焊盘都留有露出铜的空间的导电体,免去了后期凿除导线的麻烦,而且一改常规做法,将ss面都留有露出铜的空间的利用起来,镀金即包金不受焊盘都留有露出铜的空间间距影响,适用范围广,具有开创性。

10、根据本发明的一些实施例,在所述一次蚀刻的步骤中,蚀刻出的焊盘都留有露出铜的空间包括孤立焊盘都留有露出铜的空间,在孤立焊盘都留有露出铜的空间镀金的时候拉镀金导线进行电镀,电镀完成之后将镀金导线挑除,对孤立焊盘都留有露出铜的空间依旧可以采用拉镀金导线的方式进行电镀,保证现有工艺的顺畅性。

11、根据本发明的一些实施例,在挑除导线之后,对焊盘都留有露出铜的空间进行完整度检查,利用放大镜人眼观测或者利用工业视觉检测系统拍照的方式对焊盘都留有露出铜的空间进行检查,通过与合格品的焊盘都留有露出铜的空间图像对比,得出焊盘都留有露出铜的空间完整度的结论。

12、根据本发明的一些实施例,还包括阻焊步骤,整张pcb的线路蚀刻完成之后,对pcb的两面均覆上阻焊层,并且留出焊盘都留有露出铜的空间的开窗位置,流出的开窗位置便于对焊盘都留有露出铜的空间进行进一步操作,例如喷锡。

13、根据本发明的一些实施例,还包括喷锡步骤,在焊盘都留有露出铜的空间周围粘贴胶带都留有露出铜的空间,保护局部镀金位置并露出喷锡位置,然后对喷锡位置进行喷锡处理,粘贴胶带都留有露出铜的空间使需要喷锡的部分露出。

14、根据本发明的一些实施例,在所述cs面都留有露出铜的空间镀金的步骤中,将pcb的焊盘都留有露出铜的空间置于电镀液中,ss面都留有露出铜的空间的铜面作为导电体来进行镀金,将pcb的焊盘都留有露出铜的空间置于电镀液中,能够一次性电镀完全部的焊盘都留有露出铜的空间。

15、根据本发明的一些实施例,所述开窗步骤中,ss面都留有露出铜的空间贴干膜导电的夹点位置都留有露出铜的空间。

16、根据本发明的一些实施例,还包括后制程,后制程包括在阻焊完成之后对pcb进行丝印以及性能测试。

17、本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:

1.一种线路板局部表面处理工艺,其特征在于,包括下列步骤:

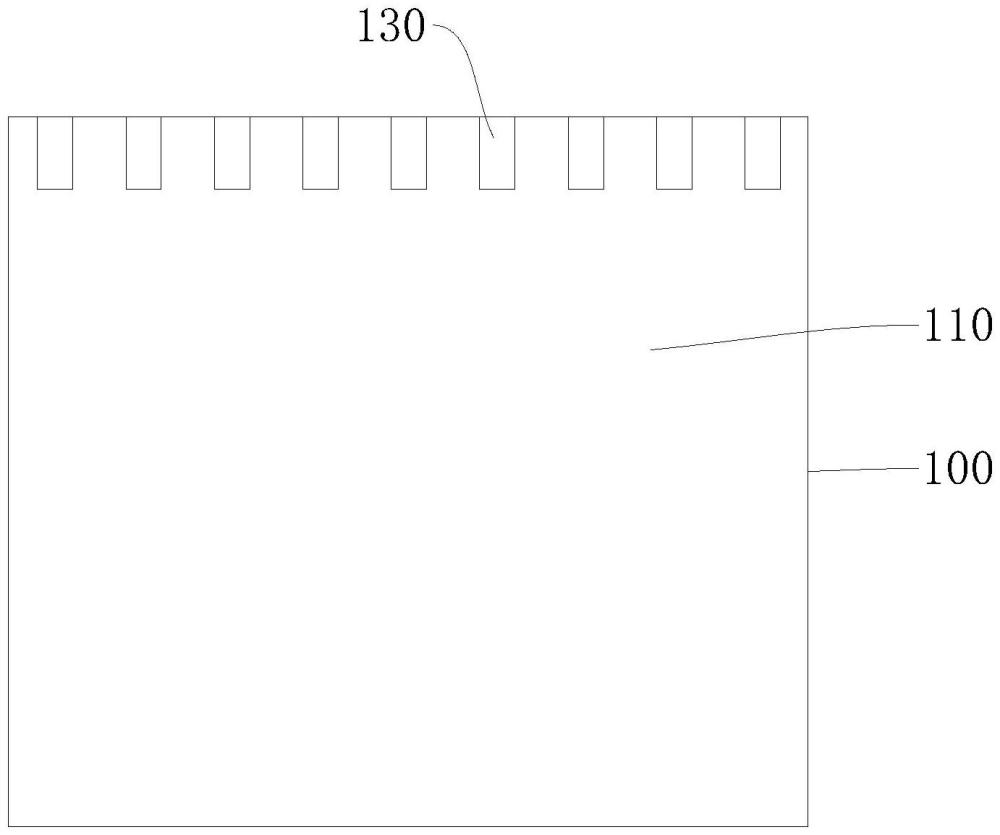

2.根据权利要求1所述的一种线路板局部表面处理工艺,其特征在于:在所述一次蚀刻的步骤中,蚀刻出的焊盘(130)包括孤立焊盘,在孤立焊盘镀金的时候拉镀金导线进行电镀,电镀完成之后将镀金导线挑除。

3.根据权利要求2所述的一种线路板局部表面处理工艺,其特征在于:在挑除导线之后,对焊盘(130)进行完整度检查,利用放大镜人眼观测或者利用工业视觉检测系统拍照的方式对焊盘(130)进行检查,通过与合格品的焊盘(130)图像对比,得出焊盘(130)完整度的结论。

4.根据权利要求1所述的一种线路板局部表面处理工艺,其特征在于:还包括阻焊步骤,整张pcb(100)的线路蚀刻完成之后,对pcb(100)的两面均覆上阻焊层,并且留出焊盘(130)的开窗位置。

5.根据权利要求4所述的一种线路板局部表面处理工艺,其特征在于:还包括喷锡步骤,在焊盘(130)周围粘贴胶带(140),保护局部镀金位置并露出喷锡位置,然后对喷锡位置进行喷锡处理。

6.根据权利要求1所述的一种线路板局部表面处理工艺,其特征在于:在所述cs面(110)镀金的步骤中,将pcb(100)的焊盘(130)置于电镀液中,ss面(120)的铜面作为导电体来进行镀金。

7.根据权利要求1所述的一种线路板局部表面处理工艺,其特征在于:所述开窗步骤中,ss面(120)贴干膜导电的夹点位置都留有露出铜的空间。

8.根据权利要求1所述的一种线路板局部表面处理工艺,其特征在于:还包括后制程,后制程包括在阻焊完成之后对pcb(100)进行丝印以及性能测试。

技术总结

本发明公开了一种线路板局部表面处理工艺,包括下列步骤:前制程,对PCB进行包括压合、钻孔、树脂塞孔、钻非塞孔金属化孔、沉铜板镀的工艺操作,然后将需要蚀刻焊盘的一面定义为CS面,另一面定义为SS面;一次蚀刻,对CS面进行显影蚀刻,形成焊盘,SS面与焊盘电性导通;开窗,对SS面和CS面贴干膜,显影后洗脱CS面上的部分干膜,使得CS面露出焊盘需要镀金的位置;CS面镀金,将SS面作为导电部分与CS面上的焊盘接通,在电镀的时候将CS面上的焊盘表面及四周电镀上金层,免去在CS面上的焊盘拉镀金导线;退干膜,将CS面和SS面的干膜完全褪去,使得SS面的铜面显露;二次蚀刻,对SS面的铜面进行蚀刻。

技术研发人员:房鹏博,荀宗献,邵家坤,刘江,梁锦练

受保护的技术使用者:珠海杰赛科技有限公司

技术研发日:

技术公布日:2024/11/14

- 还没有人留言评论。精彩留言会获得点赞!