本发明涉及集成电路,具体而言,涉及一种全数字锁相环补偿值的设定方法、装置、存储介质及设备。

背景技术:

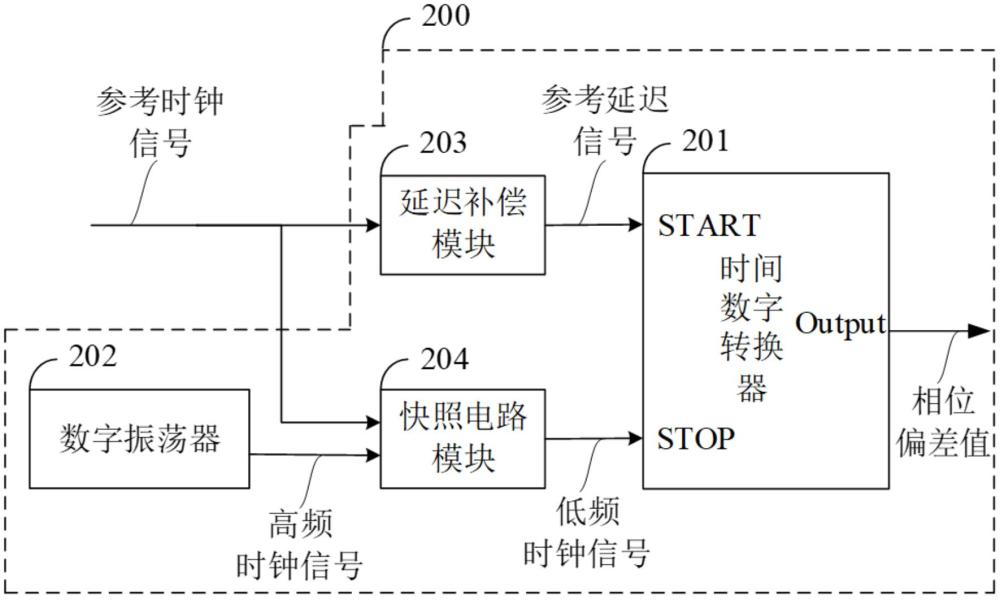

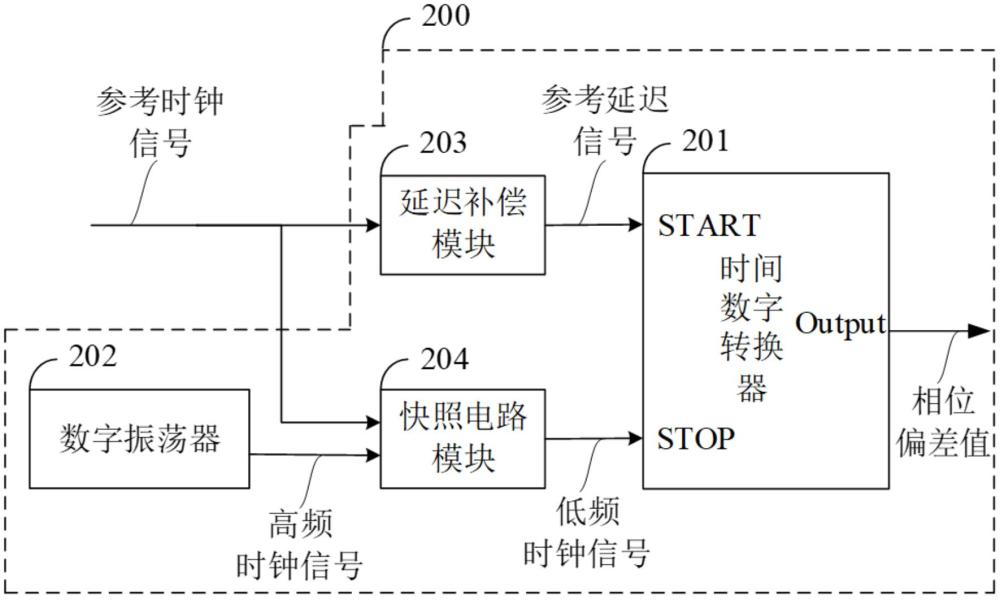

1、传统意义的模拟集成锁相环的成本在先进工艺中越来越高,而性能却趋于饱和,因此在纳米级工艺生产中全数字锁相环(all digital phase locked loop, adpll) 相比传统模拟锁相环更有优势。全数字锁相环本质上仍然工作在相位信号上,而相位信号是一种模拟信号,因此全数字锁相环通常会采用时间数字转换器(time-to-digitalconverter, tdc) 将相位信号转换成数字信号。由于时间数字转换器功耗较大,通常会设置快照电路模块使时间数字转换器工作在参考频率,以降低功耗。

2、快照电路模块涉及高频时钟域到低频时钟域的转换,其中,高频时钟域指数字振荡器(digital control oscillator, dco)频率,低频时钟域指参考时钟频率。高频时钟域对应的路径与低频时钟域对应的路径通常存在相位差,所以需要设置延迟补偿模块对两条路径上的相位差进行补偿。延迟补偿模块的补偿值大小直接影响全数字锁相环的工作状态。

3、由于快照电路模块所带来的延迟时间通常在皮秒级,难以用仪器测量其时序,或者测量成本过高。因此,如何在不依赖外部测量仪器的情况下,设置延迟补偿模块的补偿值,以保障快照电路模块对应延迟补偿的时序裕度,以保障全数字锁相环时序稳定,使其能够稳定工作,成为了本领域技术人员所关注的难题。

技术实现思路

1、本发明的目的在于提供一种全数字锁相环补偿值的设定方法、装置、存储介质及设备,以至少部分改善上述问题。

2、为了实现上述目的,本发明实施例采用的技术方案如下:

3、第一方面,本发明实施例提供一种全数字锁相环补偿值的设定方法,所述方法包括:在设置完全数字锁相环中延迟补偿模块的补偿值后,控制所述全数字锁相环工作;当所述全数字锁相环在预设时间长度内达到锁定状态时,控制所述全数字锁相环切换为开环状态;获取所述全数字锁相环的第一采样结果数和第二采样结果数,其中,所述第一采样结果数表示所述全数字锁相环中的时间数字转换器在相位超前阶段内的采样结果的数量,所述第二采样结果数表示所述时间数字转换器在相位滞后阶段内的采样结果的数量;基于所述第一采样结果数和所述第二采样结果数确定当前的补偿值是否合格。

4、第二方面,本发明实施例提供一种全数字锁相环补偿值的设定装置,所述装置包括:第一处理单元,用于设置全数字锁相环中延迟补偿模块的补偿值;所述第一处理单元还用于控制所述全数字锁相环工作,当所述全数字锁相环在预设时间长度内达到锁定状态时,控制所述全数字锁相环切换为开环状态;所述第一处理单元还用于获取所述全数字锁相环的第一采样结果数和第二采样结果数,其中,所述第一采样结果数表示所述全数字锁相环中的时间数字转换器在相位超前阶段内的采样结果的数量,所述第二采样结果数表示所述时间数字转换器在相位滞后阶段内的采样结果的数量;第二处理单元,用于基于所述第一采样结果数和所述第二采样结果数确定当前的补偿值是否合格。

5、第三方面,本发明实施例提供一种存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现上述的方法。

6、第四方面,本发明实施例提供一种电子设备,所述电子设备包括:处理器和存储器,所述存储器用于存储一个或多个程序;当所述一个或多个程序被所述处理器执行时,实现上述的方法。

7、相对于现有技术,本发明实施例所提供的一种全数字锁相环补偿值的设定方法、装置、存储介质及设备,在不依赖外部测量仪器的情况下,通过全数字锁相环中的时间数字转换器的采样结果数,对延迟补偿模块的补偿值进行验证,保障延迟补偿模块的补偿值合格,以保障快照电路模块对应延迟补偿的时序裕度,以保障全数字锁相环时序稳定,使其能够稳定工作。

8、为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:1.一种全数字锁相环补偿值的设定方法,其特征在于,所述方法包括:

2.如权利要求1所述的全数字锁相环补偿值的设定方法,其特征在于,所述基于所述第一采样结果数和所述第二采样结果数确定当前的补偿值是否合格的步骤,包括:

3.如权利要求2所述的全数字锁相环补偿值的设定方法,其特征在于,在当前的补偿值不合格时,所述方法还包括:

4.如权利要求3所述的全数字锁相环补偿值的设定方法,其特征在于,在当前的补偿值不合格时,所述方法还包括:

5.如权利要求1所述的全数字锁相环补偿值的设定方法,其特征在于,所述基于所述第一采样结果数和所述第二采样结果数确定当前的补偿值是否合格的步骤,包括:

6.如权利要求4或5所述的全数字锁相环补偿值的设定方法,其特征在于,所述相位超前方向裕度和所述相位滞后方向裕度的算式为:

7.如权利要求5所述的全数字锁相环补偿值的设定方法,其特征在于,在当前的补偿值不合格时,所述方法还包括:

8.如权利要求7所述的全数字锁相环补偿值的设定方法,其特征在于,在当前的补偿值不合格时,所述方法还包括:

9.如权利要求1所述的全数字锁相环补偿值的设定方法,其特征在于,所述获取所述全数字锁相环的第一采样结果数和第二采样结果数的步骤,包括:

10.如权利要求1所述的全数字锁相环补偿值的设定方法,其特征在于,在控制所述全数字锁相环工作后,所述方法还包括:

11.一种全数字锁相环补偿值的设定装置,其特征在于,所述装置包括:

12.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该计算机程序被处理器执行时实现如权利要求1-10中任一项所述的方法。

13.一种电子设备,其特征在于,包括:处理器和存储器,所述存储器用于存储一个或多个程序;当所述一个或多个程序被所述处理器执行时,实现如权利要求1-10中任一项所述的方法。

技术总结本发明涉及集成电路技术领域,本发明提出一种全数字锁相环补偿值的设定方法、装置、存储介质及设备,在设置完全数字锁相环中延迟补偿模块的补偿值后,控制全数字锁相环工作;当全数字锁相环在预设时间长度内达到锁定状态时,控制全数字锁相环切换为开环状态;获取全数字锁相环的第一采样结果数和第二采样结果数;基于第一采样结果数和第二采样结果数确定当前的补偿值是否合格。不依赖外部测量仪器的情况下,通过全数字锁相环中的时间数字转换器的采样结果数,对延迟补偿模块的补偿值进行验证,保障延迟补偿模块的补偿值合格,以保障快照电路模块对应延迟补偿的时序裕度,以保障全数字锁相环时序稳定,使其能够稳定工作。

技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名

受保护的技术使用者:厦门电科星拓科技有限公司

技术研发日:技术公布日:2024/8/13