一种高集成小型化半导体制冷器及其制备方法与流程

本发明涉及半导体制冷器,具体涉及一种高集成小型化半导体制冷器及其制备方法。

背景技术:

1、随着5g通信、物联网、光通信等技术的快速发展,在这些高速率通信场景下电子元器件的热管理问题日益突出。现有的,一般采用半导体制冷器(tec)实现对这些需要高速率通信模块的温度进行精准控制。

2、tec是一种固态制冷技术,原理是热电材料的帕尔贴效应,当两种不同导体构成回路时,若给回路一个直流电,则回路中的一个节点放热,另一个节点制冷。但单个热电材料晶粒的制冷能力有限,tec一般由十几到几十个晶粒组合而成,配合热敏电阻以及控制电流方向,tec既可以制冷又可以制热,实现优于0.1℃的温度控制稳定性。多个晶粒以电串联、热并联的方式交替排列,然后夹在两块导热陶瓷基板之间。

3、tec安装时,一般是将tec放置在需要散热的高速率通信模块的上表面,将回路两端的导电极通过导线连接到高速率通信模块的供电电极上。然而随着器件的小型化发展,需要减小高速率通信模块的整体厚度从而使得制造出的器件尺寸可以朝着小型化不断发展。

技术实现思路

1、本发明的目的在于提供一种高集成小型化半导体制冷器,通过将半导体制冷器嵌入到高速率通信模块陶瓷基板本体内部的凹槽内,保证了陶瓷基板本体表面的平整度,并且可以减小整个高速率通信模块的厚度,实现器件的小型化设计。

2、为了实现上述目的,本申请采用以下技术方案:

3、第一方面,本申请提供一种高集成小型化半导体制冷器,包括陶瓷基板本体,陶瓷基板本体上开设有用于放置半导体制冷器的凹槽,半导体制冷器嵌入凹槽内与陶瓷基板本体的表面齐平。

4、在一些具体实施方式中,半导体制冷器包括上基板和多个半导体晶粒,上基板盖设在凹槽上方,在上基板面向凹槽底部的下表面设有多个第一电极,凹槽底部的表面对应设有多个第二电极,半导体晶粒设置在上基板和凹槽底部之间,且半导体晶粒的两端分别与第一电极和第二电极电性连接。将第二电极直接布设在凹槽底部,可以减少半导体制冷器的下基板基材的使用,节约成本的同时减小半导体制冷器的厚度,有助于器件的小型化发展。

5、在一些具体实施方式中,上基板的面积与凹槽槽口面积匹配,使得上基板盖设在凹槽上方后与陶瓷基板本体表面在同一水平面。

6、在一些具体实施方式中,上基板与陶瓷基板本体的上表面均布设有高速率通信模块的电路层。由于上基板嵌入凹槽内后与陶瓷基板本体的表面齐平,因此,可以认为上基板也是陶瓷基板本体的一部分,那么可以在上基板上布设电路或者安装电子器件,从而节省陶瓷基板本体的安装空间,实现高速率通信模块的小型化设计。

7、在一些具体实施方式中,在凹槽底部一侧两端的第二电极作为输入电极和输出电极,从输入电极和输出电极分别引出导线沿着凹槽侧壁延伸至陶瓷基板本体表面与陶瓷基板本体表面的供电电极电性连接。

8、在一些具体实施方式中,将上基板一侧两端的两个第一电极作为输入电极和输出电极,输入电极和输出电极分别贯穿上基板与陶瓷基板本体表面的供电电极直接电性连接。从凹槽底部走线增加了线损,直接通过在基板上通过电镀打孔的方式将电极从基板上引出,然后与陶瓷基板本体表面的电极电性连接即可。

9、第二方面,本申请提供一种高集成小型化半导体制冷器的制备方法,包括以下步骤:

10、s1、根据半导体制冷器的尺寸在陶瓷基板本体上开设用于放置半导体制冷器的凹槽;

11、s2、将半导体制冷器嵌入凹槽内;

12、s3、在陶瓷基板本体的表面形成高速率通信模块的电路层。

13、在一些具体实施方式中,步骤s2的具体过程为:

14、s21、在凹槽底部形成多个第二电极,将凹槽底部一侧两端的两个第二电极作为输入电极和输出电极;

15、s22、从输入电极和输出电极分别引出导线沿着凹槽侧壁延伸至陶瓷基板本体表面与陶瓷基板本体表面的供电电极电性连接;

16、s23、将多个半导体晶粒按顺序排列并电性连接固定在第二电极上;

17、s24、将下表面设有多个第一电极的上基板嵌入凹槽内,将凹槽填平,并且第一电极与半导体晶粒电性连接固定;

18、s25、在陶瓷基板本体的表面以及上基板的上表面均形成高速率通信模块的电路层。

19、在一些具体实施方式中,步骤s2的具体过程为:

20、s21、在凹槽底部形成多个第二电极;

21、s22、将多个半导体晶粒按顺序排列并电性连接固定在第二电极上;

22、s23、在上基板面向凹槽的一面设有多个第一电极,将上基板一侧两端的两个第一电极作为输入电极和输出电极,输入电极和输出电极分别贯穿上基板;

23、s24、将上基板嵌入凹槽内将凹槽填平,并且第一电极与半导体晶粒电性连接固定;

24、s25、在陶瓷基板本体的表面以及上基板的上表面均形成高速率通信模块的电路层,并将电路层的供电电极与输入电极和输出电极直接电性连接。

25、本发明具有的有益效果:

26、通过将半导体制冷器嵌入到需要散热器件(例如高速率通信模块)的陶瓷基板本体内部的凹槽内,保证了陶瓷基板本体表面的平整度,并且可以减小整个高速率通信模块的厚度,实现器件的小型化设计,同时将半导体制冷器的第二电极直接布设在凹槽底部,省略了下基板,可以减少基材使用,节约基板成本,将半导体制冷器内嵌后,在半导体制冷器上基板的上表面还可以布设其他电路,进一步缩小了高速率通信模块的整体尺寸。

技术特征:

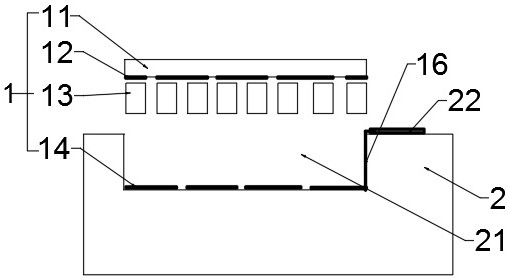

1.一种高集成小型化半导体制冷器,其特征在于,包括陶瓷基板本体(2),陶瓷基板本体(2)上开设有用于放置半导体制冷器(1)的凹槽(21),半导体制冷器(1)嵌入凹槽(21)内与陶瓷基板本体(2)的表面齐平。

2.根据权利要求1所述的一种高集成小型化半导体制冷器,其特征在于,半导体制冷器(1)包括上基板(11)和多个半导体晶粒(13),上基板(11)盖设在凹槽(21)上方,在上基板(11)面向凹槽(21)底部的下表面设有多个第一电极(12),凹槽(21)底部的表面对应设有多个第二电极(14),半导体晶粒(13)设置在上基板(11)和凹槽(21)底部之间,且半导体晶粒(13)的两端分别与第一电极(12)和第二电极(14)电性连接。

3.根据权利要求2所述的一种高集成小型化半导体制冷器,其特征在于,上基板(11)的面积与凹槽(21)槽口面积匹配,使得上基板(11)盖设在凹槽(21)上方后与陶瓷基板本体(2)表面在同一水平面。

4.根据权利要求3所述的一种高集成小型化半导体制冷器,其特征在于,上基板(11)与陶瓷基板本体(2)的上表面均布设有电路层(23)。

5.根据权利要求2所述的一种高集成小型化半导体制冷器,其特征在于,在凹槽(21)底部一侧两端的第二电极(14)作为输入电极和输出电极,从输入电极和输出电极分别引出导线(16)沿着凹槽(21)侧壁延伸至陶瓷基板本体(2)表面与陶瓷基板本体(2)表面的供电电极(22)电性连接。

6.根据权利要求2所述的一种高集成小型化半导体制冷器,其特征在于,将上基板(11)一侧两端的两个第一电极(12)作为输入电极和输出电极,输入电极和输出电极分别贯穿上基板(11)与陶瓷基板本体(2)表面的供电电极(22)直接电性连接。

7.一种高集成小型化半导体制冷器的制备方法,其特征在于,包括以下步骤:

8.根据权利要求7所述的一种高集成小型化半导体制冷器的制备方法,其特征在于,步骤s2的具体过程为:

9.根据权利要求7所述的一种高集成小型化半导体制冷器的制备方法,其特征在于,步骤s2的具体过程为:

技术总结

本发明公开了一种高集成小型化半导体制冷器及其制备方法,包括陶瓷基板本体,陶瓷基板本体上开设有用于放置半导体制冷器的凹槽,半导体制冷器嵌入凹槽内与陶瓷基板本体的表面齐平。通过将半导体制冷器嵌入到陶瓷基板本体内部的凹槽内,保证了陶瓷基板本体表面的平整度,并且可以减小整个高速率通信模块的厚度,实现器件的小型化设计,同时将半导体制冷器的第二电极直接布设在凹槽底部,省略了下基板,可以减少基材使用,节约基板成本,将半导体制冷器内嵌后,在半导体制冷器上基板的上表面还可以布设其他电路,进一步缩小了高速率通信模块的整体尺寸。

技术研发人员:孙世刚,肖亚飞,徐健,杜晶,翟军云,唐兴友,贾翔

受保护的技术使用者:四川科尔威光电科技有限公司

技术研发日:

技术公布日:2024/8/20

- 还没有人留言评论。精彩留言会获得点赞!