集成不同电子组件的半导体电子装置的制造过程及半导体电子装置的制作方法

本公开涉及集成不同电子组件的半导体电子装置的制造过程并且涉及半导体电子装置。

背景技术:

1、已知包括基于硅的有源和/或无源电子组件(例如cmos、dmos、bjt晶体管、二极管、电阻器等)的半导体电子装置,这些有源和/或无源电子组件集成在同一硅管芯中并且例如使用bcd(双极-cmos-dmos)技术制成。

2、在实践中,这些电子组件的运作基于单一半导体材料(硅)的电子特性。

3、这些装置在同一管芯上单片集成了数字电路、模拟电路和电源电路,它们在彼此非常不同的电压下工作,例如,从用于实现逻辑功能的cmos晶体管的情况下的几伏到用于电源应用的dmos晶体管的情况下的数百伏。

4、基于硅的电子组件集成到在<100>硅晶片上生长的单晶硅区域内。

5、还已知包括基于异质结构的电子组件(例如hemt晶体管)的半导体电子装置。

6、在实践中,这些电子组件的操作基于两种不同半导体材料之间的异质结的电子特性。

7、详细地,在hemt晶体管中,导电通道基于在异质结处(即,在具有不同带隙的半导体材料之间的界面处)形成的具有高迁移率的二维电子气(2deg)层的形成。例如,已知基于氮化铝镓(algan)层与氮化镓(gan)层之间的异质结的hemt装置。

8、hemt装置,特别是基于algan/gan异质结构或异质结的hemt装置,具有多种优势,使其特别适合并广泛用于不同应用。例如,hemt装置的高击穿阈值被运用于高性能电源开关;导电通道中电子的高迁移率允许形成高频放大器;此外,2deg中的高电子浓度允许获得低导通(on)状态电阻(ron)。

9、此外,用于射频(rf)应用的hemt装置通常具有比类似的硅ldmos装置更好的rf性能。

10、基于异质结构的电子组件集成到在<111>硅晶片上或在蓝宝石(al2o3)或碳化硅(sic)基板上外延生长的异质结构中。

11、为了使用简单且低成本的制造过程,基于异质结构的电子组件和基于硅的电子组件被集成在彼此不同的管芯中,从两个不同的硅晶片开始。以这种方式,基于硅的组件和基于异质结构的组件的制造过程不会互相影响。

12、例如,可以使用高热预算来生长异质结构,而不会损坏基于硅的组件。

13、但是,这使得结合基于硅的组件和基于异质结构的组件两者的电子装置具有大占用面积以及因此具有高制造成本、高功耗、和低电气性能,例如由于管芯之间的电连接引入的寄生电容、电阻或电感。

14、根据一种方法,其中形成基于硅的组件的管芯和其中形成基于异质结构的组件的管芯通过管芯转移技术彼此接合。

15、但是,即使是这种方法,在使用中也存在成本以及制造和电气性能可靠性方面的缺点。

技术实现思路

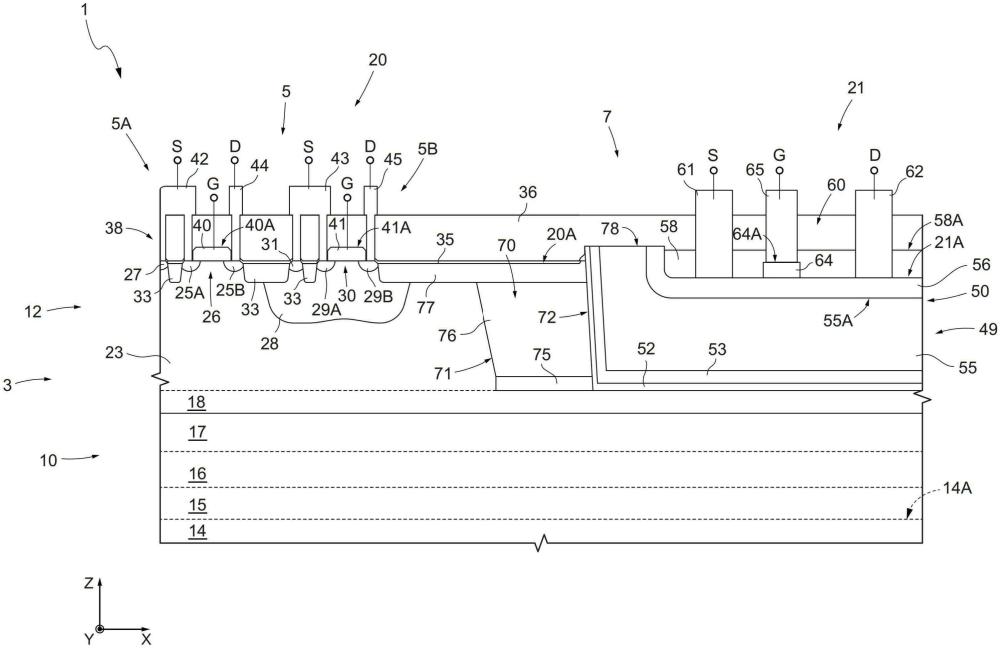

1、根据本公开,由此提供了一种半导体电子装置的制造过程和一种半导体电子装置,包括在具有第一部分和第二部分的基板层的第一部分上形成单一半导体材料的外延区域,该外延区域具有与基板层相对的第一表面。该过程包括在基板层的第二部分上形成包括异质结构的外延多层;在外延区域与外延多层之间形成具有与第一表面共面的第二表面的分隔部分,以及在外延区域上形成第一电子组件。该过程包括在异质结构上形成第二电子组件,形成第一电子组件包括在形成外延多层之后在外延区域中形成多个掺杂区域。

技术特征:

1.一种用于制造半导体电子装置的过程,包括:

2.根据权利要求1所述的制造过程,其中第一电子组件是mos晶体管,并且形成所述多个掺杂区域包括在外延区域中形成mos晶体管的源极区域、漏极区域和体接触区域。

3.根据权利要求1所述的制造过程,其中第一电子组件是具有栅极绝缘区域的mos晶体管,形成第一电子组件还包括:

4.根据权利要求1所述的制造过程,其中掺杂区域具有在1·1016原子/cm3和4·1021原子/cm3的范围内的掺杂水平。

5.根据权利要求1所述的制造过程,其中生长外延多层包括:

6.根据权利要求5所述的制造过程,其中在形成外延区域之前形成生长掩模,该生长掩模暴露基板层的第一部分。

7.根据权利要求5所述的制造过程,其中形成外延区域包括生长单一半导体材料的表面层,该表面层具有在基板层的第一部分上延伸的第一部分和在生长掩模上延伸的第二部分;并且其中在生长掩模中形成开口包括在表面层的第二部分中形成延伸到生长掩模的凹部。

8.根据权利要求7所述的制造过程,还包括形成蚀刻掩模,该蚀刻掩模在表面层的第一部分之上延伸并且具有在表面层的第二部分之上的开口,

9.根据权利要求5所述的制造过程,其中生长掩模包括氧化物层。

10.根据权利要求5所述的制造过程,其中生长掩模具有在7nm和300nm的范围内的厚度。

11.根据权利要求3所述的制造过程,其中第二电子组件是hemt晶体管并且异质结构基于元素周期表iii族和v族的材料。

12.根据权利要求11所述的制造过程,其中hemt晶体管包括具有上表面的半导体材料的沟道调制区域,形成第二电子组件包括在异质结构上生长沟道调制区域以使得沟道调制区域的上表面布置在沿着第一方向距基板层第一距离处,该第一距离小于栅极绝缘层的上表面与基板层之间沿着第一方向的第二距离。

13.根据权利要求12所述的制造过程,还包括耦合到基板层并且具有第一导电类型的基板,该基板层具有与第一导电类型不同的第二导电类型并且在基板之上延伸。

14.根据权利要求13所述的制造过程,其中单一半导体材料是硅。

15.一种电子装置,包括:

16.根据权利要求15所述的电子装置,其中第二电子组件包括:

17.根据权利要求15所述的电子装置,还包括位于基板区域与外延多层之间的缓冲层。

18.一种方法,包括:

19.根据权利要求18所述的方法,还包括,在形成表面层之后,在表面层的第一部分中形成掺杂区域和多个绝缘部分。

20.根据权利要求18所述的方法,其中工作多层包括:

技术总结

本公开涉及集成不同电子组件的半导体电子装置的制造过程及半导体电子装置。为了制造半导体电子装置,提供一种晶片,该晶片具有半导体材料的基板层,该基板层具有第一部分和与第一部分不同的第二部分。在基板层的第一部分上生长单一半导体材料的外延区域。在基板层的第二部分上生长具有异质结构的外延多层。从外延区域形成基于单一半导体材料的第一电子组件,并且从异质结构形成基于异质结构的第二电子组件。形成第一电子组件包括在生长外延多层的步骤之后在外延区域中形成多个掺杂区域。

技术研发人员:R·德彼得罗

受保护的技术使用者:意法半导体国际公司

技术研发日:

技术公布日:2025/2/10

- 还没有人留言评论。精彩留言会获得点赞!