集成电路结构及其制造方法与流程

本申请的实施例涉及集成电路结构及其制造方法。

背景技术:

1、电子行业对更小、更快的电子器件的需求不断增长,这些电子器件能够同时支持更多越来越复杂和精密的功能。为了满足这些需求,集成电路(ic)行业中存在制造低成本、高性能和低功耗ic的持续趋势。到目前为止,这些目标在很大程度上是通过按比例缩小ic尺寸(例如,最小ic部件尺寸)来实现的,从而提高了生产效率并降低了相关成本。然而,这种按比例缩小也增加了ic制造过程的复杂性。因此,实现ic器件及其性能的持续进步需要ic制造工艺和技术的类似进步。

2、最近,引入了多栅极器件来改进栅极控制。已经观察到多栅极器件增加了栅极-沟道耦合、减少关态电流、和/或减少短沟道效应(sce)。一种这样的多栅极器件是全环栅(gaa)器件,其栅极结构可以部分地或完全地围绕沟道区延伸以在至少两侧提供对沟道区的接入。gaa器件能够积极按比例缩小ic技术,保持栅极控制并减轻sce,同时与传统ic制造工艺无缝集成。随着gaa器件的不断扩展,一些领域出现了挑战,例如器件封装密度降低和电流泄漏问题,尤其是静态随机存取存储器(sram)器件。因此,尽管现有的gaa sram器件和制造这种器件的方法对于其预期目的来说通常是足够的,但它们不是在所有方面都完全令人满意。

技术实现思路

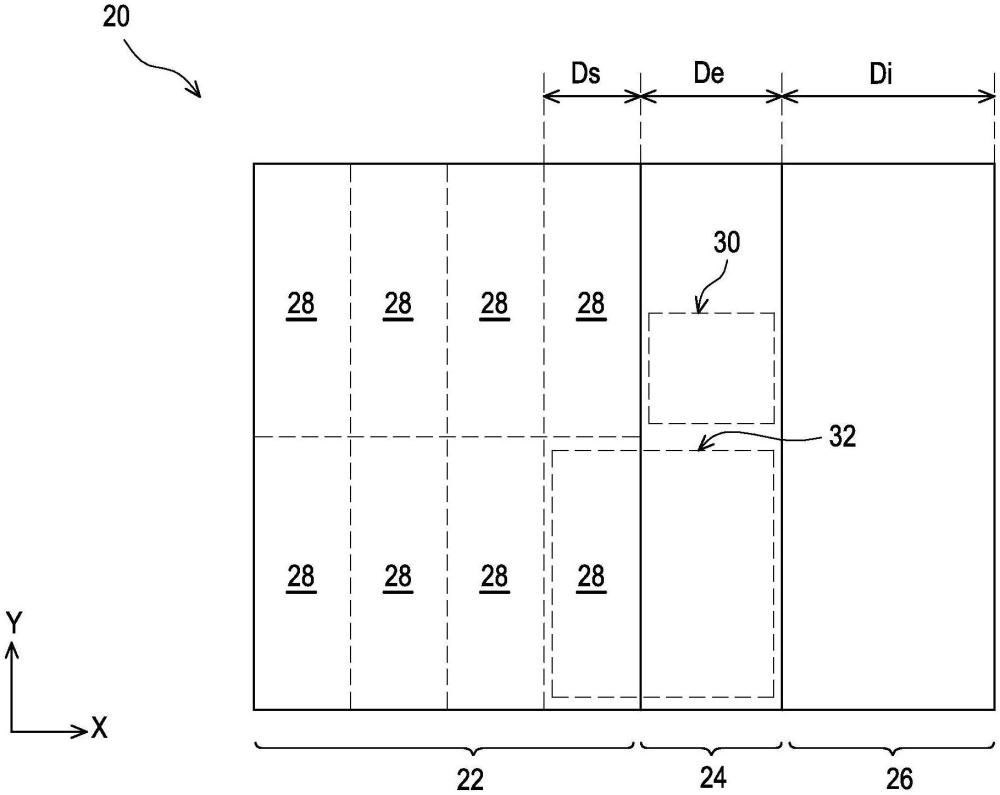

1、根据本申请的实施例的一个方面,提供了一种集成电路(ic)结构,包括:半导体衬底,具有静态随机存取存储器(sram)区、输入/输出及外围(iop)区以及跨越sram区和iop区之间的边缘区;浅沟槽隔离(sti)结构,形成在半导体衬底上并限定有源区;sram单元,形成在sram区内;以及背侧介电层,设置在半导体衬底的背侧上并且着落在sti结构的底表面上,其中,有源区沿着第一方向纵向定向,多个栅极形成在半导体衬底上并且沿着垂直于第一方向的第二方向纵向定向,栅极沿着第一方向以节距p均匀分布,sram单元沿着第一方向跨越第一尺寸ds,边缘区沿着第一方向跨越第二尺寸de,并且比率de/ds等于2或小于2。

2、根据本申请的实施例的另一个方面,提供了一种集成电路结构,包括:半导体衬底,具有静态随机存取存储器(sram)区、输入/输出及外围(iop)区以及跨越sram区和iop区之间的边缘区;n型掺杂阱,沿着第一方向连续延伸穿过sram区和边缘区;p型掺杂阱,沿着第一方向连续延伸穿过sram区和边缘区;浅沟槽隔离(sti)结构,形成在半导体衬底上并限定沿着第一方向纵向定向的第一有源区、第二有源区和第三有源区;多个栅极,沿着垂直于第一方向的第二方向纵向定向,其中,栅极以周期性节距p均匀分布在sram区和边缘区中;以及背侧介电层,接触半导体衬底的底表面和sti结构的底表面,其中sram区包括sram单元,sram单元各自沿着第一方向跨越第一尺寸ds,边缘区沿着第一方向跨越第二尺寸de,并且比率de/ds等于2或小于2。

3、根据本申请的实施例的又一个方面,提供了一种制造集成电路(ic)结构的方法,包括:接收具有前侧和背侧的半导体衬底,其中,半导体衬底包括静态随机存取存储器(sram)区、输入/输出及外围(iop)区、以及跨越sram区和iop区之间的边缘区;在半导体衬底的前侧上的sram区中形成具有sram单元的sram结构;在sram结构上方形成互连结构;从背侧减薄半导体衬底,使得浅沟槽隔离(sti)结构从背侧暴露;以及直接在sti结构的底表面和半导体衬底的底表面上形成背侧介电层。

技术特征:

1.一种集成电路结构,包括:

2.根据权利要求1所述的集成电路结构,其中,所述浅沟槽隔离结构的底表面和所述半导体衬底的底表面共面。

3.根据权利要求1所述的集成电路结构,其中

4.根据权利要求3所述的集成电路结构,还包括背侧通孔,所述背侧通孔形成在所述半导体衬底的所述背侧上并且着落在所述源极和所述漏极中的一个上,其中

5.根据权利要求4所述的集成电路结构,还包括形成在所述半导体衬底的所述背侧上的背侧介电通孔,其中,所述背侧介电通孔由所述半导体衬底包围并且横向接触所述背侧介电层。

6.一种集成电路结构,包括:

7.根据权利要求6所述的集成电路结构,其中

8.根据权利要求7所述的集成电路结构,其中

9.一种制造集成电路结构的方法,包括:

10.根据权利要求9所述的方法,其中,形成具有静态随机存取存储器单元的静态随机存取存储器结构还包括:

技术总结

本公开提供了一种集成电路(IC)结构及其制造方法,该IC结构包括:半导体衬底,具有静态随机存取存储器(SRAM)区、输入/输出及外围(IOP)区域以及跨越SRAM区和IOP区之间的边缘区;浅沟槽隔离(STI)结构,形成在半导体衬底上并限定有源区;SRAM单元,形成在SRAM区内;以及背侧介电层,设置在半导体衬底的背侧上并且着落在STI结构的底表面上,其中有源区沿着第一方向纵向定向,多个栅极形成在半导体衬底上并且沿着垂直于第一方向的第二方向纵向定向,栅极沿着第一方向以节距P均匀分布,SRAM单元沿着第一方向跨越第一尺寸Ds,边缘区沿着第一方向跨越第二尺寸De,并且比率De/Ds等于2或小于2。

技术研发人员:陈瑞麟,张峰铭,王屏薇,吴于贝

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/11/28

- 还没有人留言评论。精彩留言会获得点赞!