一种高速发送器及串行数据发送器电路的制作方法

本申请涉及信号传输电路设计的,尤其涉及一种高速发送器及串行数据发送器电路。

背景技术:

1、hstx(high speed transmitter)即高速发送器,是一种在通信、数据传输等领域中广泛应用的重要设备,具有高速度、高稳定性、多功能性等特点。

2、相关技术中提供的高速发送器,通过接收来自数字系统的并行数据。这些数据在高速发送器内部通过一系列处理,被转换为串行数据流,以便在高速串行链路上进行传输。通常使用串行化器(serializer)来实现这一转换。串行化器由多个移位寄存器组成,每个移位寄存器对应一个数据位。在时钟信号的控制下,移位寄存器将数据按位依次输出,形成串行数据流。

3、但在上述相关技术中,基于高速串行链路对串行数据流进行传输时,由于高速串行链路各个传输单元的供电端较为分散,导致高速串行链路在电压供应时的线上压降会增加,以至于无法正常满足高速串行链路传输时的正常供压需求。

技术实现思路

1、为解决上述技术问题,本申请的实施例提供了一种高速发送器及串行数据发送器电路。

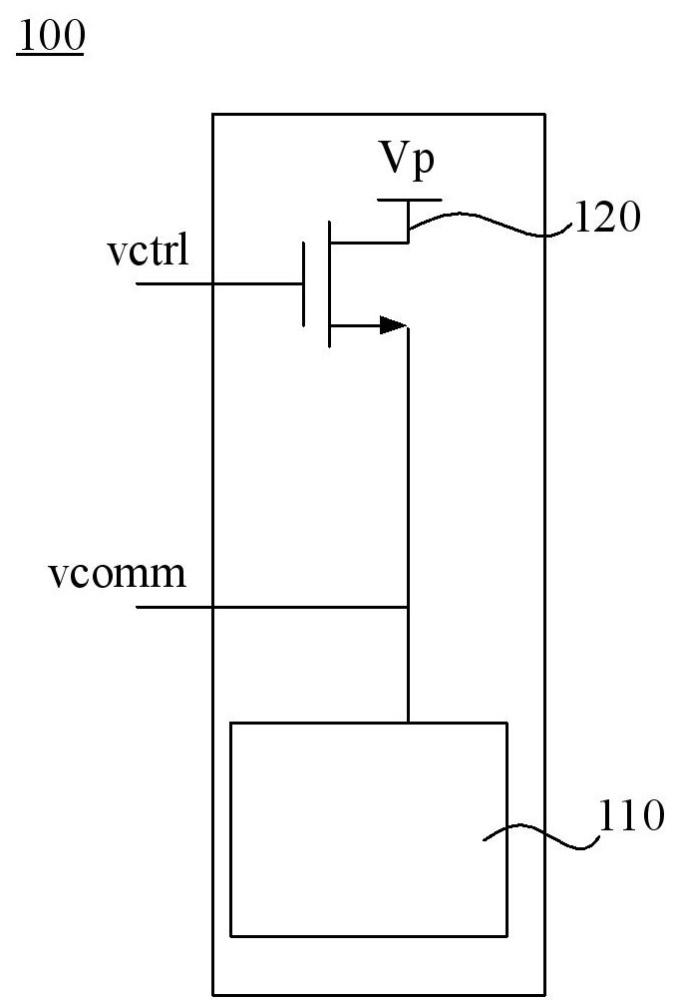

2、根据本申请实施例的一个方面,提供了一种高速发送器,包括信号传输单元,所述信号传输单元包括:信号收发模块,用于对输入的目标信号进行传输;第一功率管,其输入端用于接收输入的目标电压,其输出端与所述信号收发模块的供电端连接。

3、在本申请的一些实施例中,基于以上技术方案,所述信号传输单元有多个,多个所述信号传输单元串行连接形成传输链路。

4、在本申请的一些实施例中,基于以上技术方案,所述高速发送器还包括第一运放电路和第二功率管;所述第一运放电路的输出端分别与所述第二功率管的输入端和所述第一功率管的输入端连接,所述第二功率管的输出端与所述第一功率管的输出端连接;所述第一运放电路的输入端用于接收输入的基准电压,以对所述基准电压转换得到所述目标电压。

5、在本申请的一些实施例中,基于以上技术方案,所述第一运放电路包括第一放大器,所述第一放大器包括正相输入端和反相输入端;所述第一放大器的正相输入端用于接收所述基准电压;所述第一放大器的反相输入端与所述第二功率管的输出端连接。

6、在本申请的一些实施例中,基于以上技术方案,所述高速发送器还包括第一稳压电容;所述第一稳压电容的一端与所述第一运放电路的输出端连接,所述第一稳压电容的另一端接地。

7、在本申请的一些实施例中,基于以上技术方案,所述高速发送器还包括第一稳压电阻;所述第一稳压电阻的一端与所述第二功率管的输出端连接,所述第一稳压电阻的另一端接地。

8、在本申请的一些实施例中,基于以上技术方案,所述信号传输单元还包括第二运放电路;所述第二运放电路的输出端与所述第一功率管的输入端连接;所述第二运放电路的输入端用于接收输入的基准电压,以对所述基准电压转换得到所述目标电压。

9、在本申请的一些实施例中,基于以上技术方案,所述第二运放电路包括第二放大器,所述第二放大器包括正相输入端和反相输入端;所述第二放大器的正相输入端用于接收所述基准电压;所述第二放大器的反相输入端与所述第一功率管的输出端连接。

10、在本申请的一些实施例中,基于以上技术方案,所述信号传输单元还包括第二稳压电容;所述第二稳压电容的一端与所述第二运放电路的输出端连接,所述第二稳压电容的另一端接地。

11、根据本申请实施例的另一个方面,提供了一种串行数据发送器电路,包括上述实施例记载的高速发送器。

12、本申请实施例的技术方案中,通过上述

技术实现要素:

至少可以带来如下有益效果:

13、通过在信号传输单元中设置第一功率管,并根据第一功率管的输入端输入的目标电压控制第一功率管对信号收发模块执行供电,同时结合功率管具有较低导通电阻的特性,以使得设置第一功率管可以减小信号收发模块的供电端的压降,从而能够满足高速串行链路传输时的正常供压需求。

技术特征:

1.一种高速发送器,其特征在于,包括信号传输单元,所述信号传输单元包括:

2.根据权利要求1所述的高速发送器,其特征在于,所述信号传输单元有多个,多个所述信号传输单元串行连接形成传输链路。

3.根据权利要求2所述的高速发送器,其特征在于,所述高速发送器还包括第一运放电路和第二功率管;

4.根据权利要求3所述的高速发送器,其特征在于,所述第一运放电路包括第一放大器,所述第一放大器包括正相输入端和反相输入端;

5.根据权利要求3所述的高速发送器,其特征在于,所述高速发送器还包括第一稳压电容;

6.根据权利要求3所述的高速发送器,其特征在于,所述高速发送器还包括第一稳压电阻;

7.根据权利要求2所述的高速发送器,其特征在于,所述信号传输单元还包括第二运放电路;

8.根据权利要求7所述的高速发送器,其特征在于,所述第二运放电路包括第二放大器,所述第二放大器包括正相输入端和反相输入端;

9.根据权利要求7所述的高速发送器,其特征在于,所述信号传输单元还包括第二稳压电容;

10.一种串行数据发送器电路,其特征在于,包括如权利要求1-9中任一项所述的高速发送器。

技术总结

本申请公开了一种高速发送器及串行数据发送器电路,涉及信号传输电路设计的技术领域,其中,该高速发送器包括信号传输单元,所述信号传输单元包括:信号收发模块,用于对输入的目标信号进行传输;第一功率管,其输入端用于接收输入的目标电压,其输出端与所述信号收发模块的供电端连接。本申请的技术方案通过在信号传输单元中设置第一功率管,并根据第一功率管的输入端输入的目标电压控制第一功率管对信号收发模块执行供电,同时结合功率管具有较低导通电阻的特性,以使得设置第一功率管可以减小信号收发模块的供电端的压降,从而能够满足高速串行链路传输时的正常供压需求。

技术研发人员:栾昌海,袁尚琪

受保护的技术使用者:牛芯半导体(深圳)有限公司

技术研发日:

技术公布日:2024/9/12

- 还没有人留言评论。精彩留言会获得点赞!