一种支持SSC的SerDesCDR电路的制作方法

本申请属于通信,特别涉及一种支持ssc的serdes cdr电路。

背景技术:

1、计算机技术的广泛应用和高性能计算需求的不断增加,推动了高速数据传输技术的快速发展。pcie协议(peripheral component interface express,总线和接口标准)是计算机技术中最为关键的接口协议之一,随着高速数据传输技术的不断发展,pcie也在持续地不断演进。

2、而随着pcie协议速率的提升,ssc功能的实现难度也越来越大,从某种程度上说,也成为了pcie协议电路设计的一个重要的瓶颈。

技术实现思路

1、本申请的目的在于提供一种支持ssc的serdes cdr电路,旨在解决降低环路的设计难度,提高环路的跟踪性能。

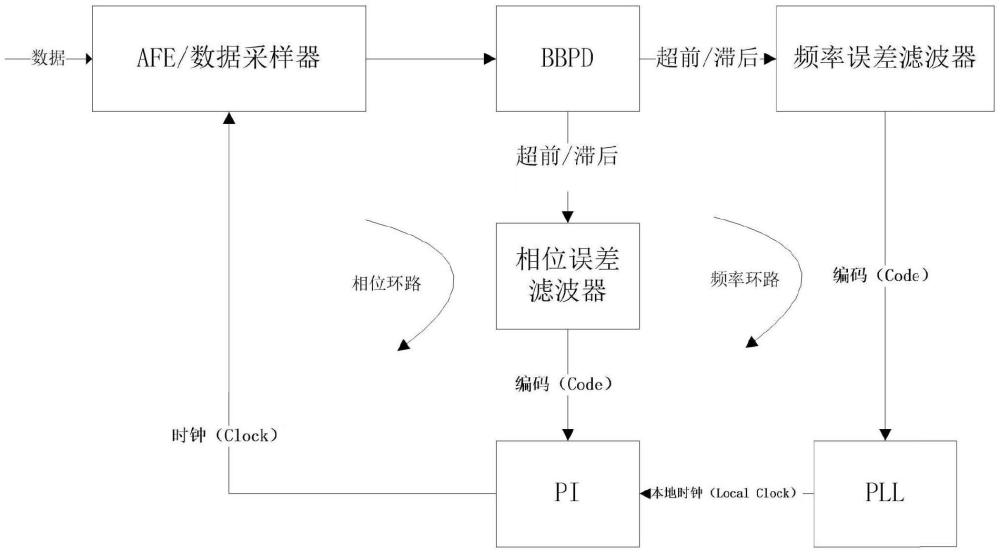

2、本申请提供了一种支持ssc的serdes cdr电路,包括数据采样器、相位检测器、频率误差滤波器、相位误差滤波器、相位内插器和锁相环,其中,所述数据采样器用于对输入数据进行afe(aanlog front end,模拟前端)补偿和数据采样;

3、所述相位检测器与所述频率误差滤波器、所述锁相环连接组成一频率环路;

4、所述相位检测器与所述相位误差滤波器、所述相位内插器连接组成一相位环路。

5、在可选的实施方式中,所述频率误差滤波器通过输出编码用来控制所述锁相环的工作频率。

6、在可选的实施方式中,所述相位误差滤波器通过输出编码用来控制相位内插器输出的采样时钟的相位。

7、在可选的实施方式中,所述频率环路和所述相位环路具备不同的环路带宽,所述频率环路和所述相位环路的环路带宽相差1~2数量级。

8、在可选的实施方式中,所述频率误差滤波器为二阶pi数字滤波器,所述相位误差滤波器为一阶数字滤波器。

9、在可选的实施方式中,所述频率环路用于跟踪所述输入数据中的30~33k的ssc扩频信息。

10、在可选的实施方式中,所述相位环路用于跟踪所述输入数据中的相位信息。

11、在可选的实施方式中,所述频率误差滤波器控制所述锁相环输出的local时钟频率动态跟踪pcie协议定义的ssc扩频频偏,实现所述频率环路跟踪。

12、在可选的实施方式中,所述锁相环输出的local时钟频率输入到所述相位内插器,所述相位内插器输出时钟频率到数据采样器中实现所述数据的环路跟踪。

13、在可选的实施方式中,所述相位检测器与所述数据采样器连接,用于对输入数据进行鉴相后产生当前采样相位超前/滞后的指示信号后分别输入到所述频率误差滤波器和所述相位误差滤波器。

14、相比于相关技术,本申请的技术方案至少具备以下优点:

15、本申请中的频率环路可以直接实现频率跟踪控制,从而降低了对过滤器工作频率的设计要求。同时,由于频率环路解决了频率跟踪的问题,相位环路只需要能够跟踪残余的相位误差,这样可以把pi(phase interpolator,相位内插器)的step步进设计得小,从而使得环路跟踪时动态抖动(jitter)更小,这样就能获得更好的cdr的特性。

16、本申请的其它特征和优点将在随后的说明书中阐述,并且部分地从说明书中变得显而易见,或者通过实施本申请而了解。本申请的目的和其他优点可以通过在说明书以及附图中所指出的结构和流程来实现和获取。

技术特征:

1.一种支持ssc的serdes cdr电路,其特征在于,包括数据采样器、相位检测器、频率误差滤波器、相位误差滤波器、相位内插器和锁相环,其中,

2.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,所述频率误差滤波器通过输出编码用来控制所述锁相环的工作频率。

3.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,所述相位误差滤波器通过输出编码用来控制相位内插器输出的采样时钟的相位。

4.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,所述频率环路和所述相位环路具备不同的环路带宽,所述频率环路和所述相位环路的环路带宽相差1~2数量级。

5.如权利要求4所述的支持ssc的serdes cdr电路,其特征在于,所述频率误差滤波器为二阶pi数字滤波器,所述相位误差滤波器为一阶数字滤波器。

6.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,所述频率环路用于跟踪所述输入数据中的30~33k的ssc扩频信息。

7.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,所述相位环路用于跟踪所述输入数据中的相位信息。

8.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,所述频率误差滤波器控制所述锁相环输出的local时钟频率动态跟踪pcie协议定义的ssc扩频频偏,实现所述频率环路跟踪。

9.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,

10.如权利要求1所述的支持ssc的serdes cdr电路,其特征在于,所述相位检测器与所述数据采样器连接,用于对输入数据进行鉴相后产生当前采样相位超前/滞后的指示信号后分别输入到所述频率误差滤波器和所述相位误差滤波器。

技术总结

本申请提供了一种支持SSC的SerDes CDR电路,该电路包括数据采样器、相位检测器、频率误差滤波器、相位误差滤波器、相位内插器和锁相环,相位检测器与频率误差滤波器、锁相环连接组成一频率环路,频率误差滤波器通过输出编码用来控制锁相环的工作频率;相位检测器与相位误差滤波器、相位内插器连接组成一相位环路,相位误差滤波器通过输出编码用来控制相位内插器输出的采样时钟的相位。本申请将频率跟踪和相位跟踪分为不同的环路来实现,使得频率跟踪和相位跟踪分离,可以降低环路的设计难度,提高环路的跟踪性能。

技术研发人员:刘志惠,刘磊,李凯,刘少华,陈兴生

受保护的技术使用者:无锡众星微系统技术有限公司

技术研发日:

技术公布日:2024/11/18

- 还没有人留言评论。精彩留言会获得点赞!