半导体存储器装置及其形成方法与流程

本申请涉及一种半导体存储器装置及其形成方法。

背景技术:

1、近来,在例如动态随机存取存储器的半导体存储器装置中,期望增加存储器容量,但是由于更精细的处理尺寸而难以增加存储器容量。因此,已经提出了通过存储器单元中的存取晶体管的竖直结构来实现存储器单元的平面面积的减小以及存储器容量的增加的技术。

技术实现思路

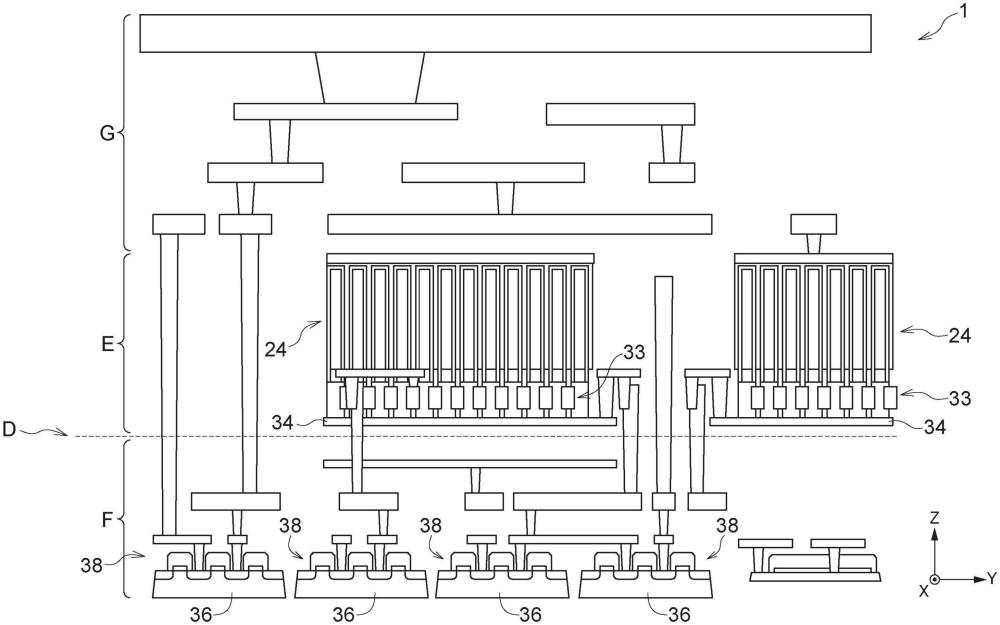

1、在一个方面,本申请提供一种半导体存储器装置,其包括:存取晶体管,其配置为包括沟道部分和一对源极/漏极区的竖直晶体管;存储电容器,其连接到所述一对源极/漏极区中的一者;位线,其连接到所述一对源极/漏极区中的另一者;以及第一半导体层,其设置在所述源极/漏极区中,所述位线连接到所述第一半导体层。

2、在另一方面,本申请进一步提供一种制造半导体存储器装置的方法,所述半导体存储器装置包括一对源极/漏极区、安置在所述源极/漏极区之间且被绝缘体包围的沟道部分、包括经由栅极绝缘膜与所述沟道部分相对的栅极电极的竖直晶体管、以及连接到所述源极/漏极区中的一者的存储电容器,所述方法包括:形成在半导体衬底上沿垂直于所述半导体衬底的第一方向延伸的多个柱结构,每个柱结构包括作为堆叠结构的包括源极/漏极区中的一者的第一半导体层、包括所述沟道部分的第二半导体层,以及第一绝缘体层;去除所述第一绝缘体层以暴露所述第二半导体层;通过用杂质掺杂暴露的第二半导体层来形成所述源极/漏极区中的另一者;形成连接到所述源极/漏极区中的另一者并沿所述第一方向延伸的存储电容器;通过使用所述第一半导体层作为蚀刻停止剂进行蚀刻来去除所述半导体衬底,以暴露所述第一半导体层;以及形成与所述第二半导体层的侧表面接触的栅极绝缘膜和栅极电极。

3、在又一方面,本申请进一步提供一种制造半导体存储器装置的方法,其包括:形成在半导体衬底上沿垂直于所述半导体衬底的第一方向延伸的多个柱结构,每个柱结构包括作为堆叠结构的第一半导体层、第二半导体层和第一绝缘体层;在所述柱结构之间形成第二绝缘体层和屏蔽板;去除所述第一绝缘体层以暴露所述第二半导体层;用杂质掺杂所述第二半导体层以形成掺杂部分;形成连接到暴露的第二半导体层并沿所述第一方向延伸的存储电容器;通过蚀刻去除所述半导体衬底以暴露所述第一半导体层;在所述第二半导体层中的每一者与所述屏蔽板之间形成从所述第一半导体层侧到达所述掺杂部分的沟槽;在所述沟槽中形成栅极绝缘膜和栅极电极;以及形成连接到所述第一半导体层的位线。

技术特征:

1.一种半导体装置,其包括:

2.根据权利要求1所述的半导体装置,其中所述第一半导体层包括硅锗(sige)。

3.根据权利要求1所述的半导体装置,其中所述晶体管进一步包括栅极电极,所述栅极电极通过栅极绝缘膜与所述沟道部分的侧表面接触。

4.根据权利要求1所述的半导体装置,其中所述第二掺杂部分和所述沟道部分彼此接触。

5.根据权利要求4所述的半导体装置,其中所述晶体管进一步包括位于所述第二掺杂部分的一部分与所述沟道部分的一部分之间的延伸的掺杂部分。

6.根据权利要求5所述的半导体装置,其中:

7.根据权利要求1所述的半导体装置,其进一步包括在所述晶体管与相邻于所述晶体管的其他晶体管之间的屏蔽板。

8.根据权利要求7所述的半导体装置,其中所述屏蔽板位于所述晶体管的所述沟道部分与另一晶体管的栅极电极之间。

9.根据权利要求7所述的半导体装置,其中所述第一掺杂部分、所述第二掺杂部分和所述屏蔽板包括磷(p)。

10.一种制造半导体存储器装置的方法,所述半导体存储器装置包括晶体管,所述方法包括:

11.根据权利要求10所述的方法,其中:

12.根据权利要求10所述的方法,其进一步包括在所述间隙中形成第二绝缘层和所述第二绝缘层中的屏蔽板。

13.根据权利要求12所述的方法,其进一步包括使用杂质对通过所述蚀刻暴露的所述第一半导体层掺杂,以形成所述第一半导体层的掺杂部分。

14.根据权利要求13所述的方法,其进一步包括:

15.根据权利要求14所述的方法,其中使用光刻和干蚀刻来执行形成所述沟槽。

16.根据权利要求14所述的方法,其中通过离子注入使用所述杂质来执行掺杂所暴露的第一半导体层、所暴露的第二半导体层和所述第二半导体层的所述所暴露的掺杂部分。

17.根据权利要求14所述的方法,其中所暴露的第一半导体层、所暴露的第二半导体层、所述所暴露的掺杂部分和所述屏蔽板的所述杂质是磷。

18.根据权利要求14所述的方法,其进一步包括在所述沟槽中形成栅极绝缘膜和栅极电极。

19.根据权利要求18所述的方法,其中通过化学气相沉积(cvd)执行形成所述栅极绝缘膜和所述栅极电极。

20.一种半导体装置,其包括:

21.根据权利要求20所述的半导体装置,其中所述位线包括包含硅化钨(wsi)、氮化钨(wn)或钨(w)中至少一者的任何一种导电材料。

技术总结

本申请涉及一种半导体存储器装置及其形成方法。一种半导体存储器装置,其包含:存取晶体管,其配置为包括沟道部分和一对源极/漏极区的竖直晶体管;存储电容器,其连接到所述一对源极/漏极区中的一者;位线,其连接到所述一对源极/漏极区中的另一者;第一半导体层,其设置在所述源极/漏极区中,所述位线连接到所述第一半导体层。优选地,所述第一半导体层包括SiGe。

技术研发人员:祐川光成

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/12/17

- 还没有人留言评论。精彩留言会获得点赞!