电子器件的制作方法

本公开一般而言涉及电子器件,并且更特别地涉及包括晶体管的电子器件。

背景技术:

1、许多电子器件包括晶体管,并且更特别地包括共栅极晶体管(common-gatedtransistor)。共栅极晶体管是指其栅极耦合(优选地,连接)在一起的晶体管,使得晶体管由相同的控制电压控制。例如,这种晶体管可以是基本晶体管,即,所有都具有相同尺寸、耦合在一起以形成更大尺寸的晶体管的等效物的小晶体管。由此,基本晶体管的栅极耦合(优选地,连接)在一起,基本晶体管的漏极耦合(优选地,连接)在一起,以及基本晶体管的源极耦合(优选地,连接)在一起。

2、确保晶体管接收相同的控制电压并且同时接收所述控制电压将是有益的。

技术实现思路

1、一个实施例提供了一种包括沟槽的器件,沟槽各自包括导电元件,该导电元件被配置用于将位于第一层的第一侧上的晶体管栅极的指状物电耦合到在第一层的第二面侧上延伸的第二层。

2、另一个实施例提供了一种制造器件的方法,包括形成沟槽,沟槽各自包括导电元件,该导电元件被配置用于将位于第一层的第一侧上的晶体管栅极的指状物电耦合到在第一层的第二侧上延伸的第二层。

3、根据实施例,第二层被配置用于被偏置到晶体管的控制电压。

4、根据实施例,晶体管按行布置,同一行的晶体管通过同一指状物通过它们的栅极耦合在一起,各行按列布置,各列通过沟槽两两分离开,每个沟槽的导电元件将两列分离开,耦合到所述两列的指状物中的每个指状物的一端。

5、根据实施例,每列位于两个沟槽之间,每个指状物在一端处耦合到所述两个沟槽中的一个沟槽的导电元件,以及在另一端处耦合到所述两个沟槽中的另一个沟槽的导电元件。

6、根据实施例,第一层由gan、aln或algan制成。

7、根据实施例,该器件包括位于第一层的第二侧上的半导体基板,该基板形成第二层。

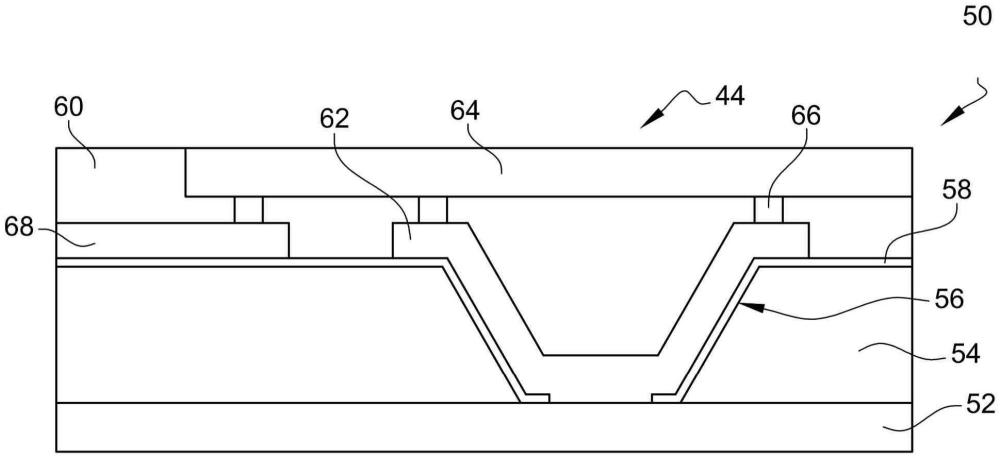

8、根据实施例,每个沟槽包括延伸穿过第一层的腔体,腔体的底部包括基板,导电元件包括在腔体的壁和底部之上延伸的第三导电层。

9、根据实施例,该器件包括位于第一层的第二侧上的半导体基板,该基板的距离第一层最远的面覆盖有第四导电层,该第四层形成第二层。

10、根据实施例,第三层由金属制成。

11、根据实施例,每个沟槽包括延伸穿过第一层的腔体,腔体的底部位于基板的最靠近第一层的面处,导电元件包括在腔体的壁和底部之上延伸的第三导电层以及位于基板中、与第三层接触并与第四层接触的部分。

12、根据实施例,第三层通过第五绝缘层与第一层分离开。

13、根据实施例,基板由硅制成或由碳化硅制成。

14、根据实施例,每个导电元件通过互连网络的轨道和通孔耦合到指状物。

15、根据实施例,一种器件包括具有第一面和第二面的第一层,以及位于第一层下方且耦合到第一层的第二面的第二层。该器件包括位于第一层的第一侧上的多个指状物,每个指状物与多个晶体管的栅极对应,位于第一层中的多个沟槽各自包括将指状物电耦合到第二层的导电元件。

16、根据实施例,一种制造器件的方法包括在第二层上形成第一层,以及在第一层的第一侧上形成多个指状物,每个指状物与多个晶体管的集合栅极对应。该方法包括形成从第一层的第一侧延伸到第一层的第二侧的多个沟槽,以及在每个沟槽中形成将多个指状物电耦合到第二层的相应导电元件。

17、根据实施例,一种器件包括半导体基板、半导体基板上的半导体层和第一晶体管组。该器件包括在半导体层上在第一方向上延伸并与第一晶体管组的集合栅极对应的第一指状物、第二晶体管组和在半导体层上在第一方向上延伸并与第二晶体管组的集合栅极对应的第二指状物。该器件包括第一指状物与第二指状物之间的半导体层中的沟槽以及在沟槽中与半导体基板接触并将第一指状物和第二指状物电耦合到半导体基板的导电元件。

技术特征:

1.一种器件,包括:

2.根据权利要求1所述的器件,其中第二层被配置为被偏置到晶体管的控制电压。

3.根据权利要求1所述的器件,其中晶体管按行布置,同一行的晶体管具有与同一指状物对应的集体栅极,各行按列布置,各列由沟槽两两分离开,每个沟槽的导电元件将两列分离开以及耦合到所述两列的指状物中的每个指状物的一端。

4.根据权利要求3所述的器件,其中每列位于两个沟槽之间,每个指状物在一端处耦合到所述两个沟槽中的一个沟槽的导电元件,以及在另一端处耦合到所述两个沟槽中的另一个沟槽的导电元件。

5.根据权利要求1所述的器件,其中第一层为gan、aln或algan。

6.根据权利要求1所述的器件,其中第二层为半导体基板。

7.根据权利要求6所述的器件,其中每个沟槽包括延伸穿过第一层的腔体,腔体的底部暴露基板,以及导电元件包括在腔体的壁和腔体的底部之上延伸的第三导电层。

8.根据权利要求1所述的器件,包括位于第二层的底部上以及通过第二层与第一层分离开的第四导电层,其中第二层为半导体基板。

9.根据权利要求8所述的器件,其中第三层是金属。

10.根据权利要求8所述的器件,其中每个沟槽包括延伸穿过第一层的腔体,腔体的底部位于基板的最靠近第一层的面处,导电元件包括在腔体的壁和底部之上延伸的第三导电层以及位于基板中、与第三层接触并与第四层接触的部分。

11.根据权利要求8所述的器件,其中第三层通过绝缘材料的第五层与第一层分离开。

12.根据权利要求6所述的器件,其中半导体基板为硅或者由碳化硅制成。

13.根据权利要求1所述的器件,其中每个导电元件通过互连网络的轨道和通孔耦合到指状物。

14.一种制造器件的方法,包括:

15.根据权利要求14所述的方法,其中第二层被配置为被偏置到晶体管的控制电压。

16.根据权利要求15所述的方法,包括形成将每个指状物电耦合到导电元件中的至少一个导电元件的金属互连结构。

17.根据权利要求14所述的方法,其中晶体管按行布置,同一行的晶体管具有与同一指状物对应的集体栅极,各行按列布置,各列通过沟槽两两分离开,每个沟槽的导电元件将两列分离开以及耦合到所述两列的指状物中的每个指状物的一端。

18.一种器件,包括:

19.如权利要求18所述的器件,包括位于半导体基板下方以及与半导体基板接触的导电层。

20.如权利要求19所述的器件,包括延伸穿过半导体层、半导体基板以及接触导电层的电接触件。

技术总结

本公开涉及一种电子器件。一种器件包括沟槽。沟槽各自包括导电元件,该导电元件被配置为将位于第一层的第一侧上的晶体管栅极的耦合指状物电耦合到在第一层的第二面侧上延伸的第二层。

技术研发人员:T·欧黑克斯,M·农盖拉德

受保护的技术使用者:意法半导体国际公司

技术研发日:

技术公布日:2025/3/13

- 还没有人留言评论。精彩留言会获得点赞!