一种具有快速响应速度的铪基铁电叠层结构及其制备方法

本发明涉及铁电存储器制造工艺,具体涉及一种具有快速响应速度的铪基铁电叠层结构及其制备方法。

背景技术:

1、作为与cmos工艺兼容的材料,基于氧化铪(hfo2)的铁电器件展现出出色的scaling能力和与现有超大规模集成(vlsi)技术高度兼容的特点。这些特点推动了铁电(fe)器件成为未来电子产品的潜在候选者。研究人员已成功展示了多种基于铪-锆-氧化物(hzo)的铁电(fe)器件,包括铁电电容器、铁电场效应晶体管(fefets)和铁电隧道结(ftjs)。这些器件被视为各种新兴和需求量大的应用(如非挥发性存储器、电子突触和神经元)的有前景候选者。

2、铁电随机存取存储器和铁电隧穿结器件为典型的金属-绝缘体-金属(mim)电容结构。但是由于器件较高的翻转电场,导致在相同工作电压下,降低器件响应速度,且无法在较低的电压下提供较大的极化强度值,这限制了器件在实现超高速和低功耗方面的性能。

技术实现思路

1、本发明公开一种具有快速响应速度的铪基铁电叠层结构,包括:衬底;底电极,形成在所述衬底上,沿第一方向间隔排列;铁电功能叠层,形成在所述底电极上,由不同掺杂比例的多层铪基铁电薄膜构成;顶电极,形成在所述铁电功能叠层上,沿第二方向间隔排列,与第一方向垂直。

2、本发明的具有快速响应速度的铪基铁电叠层结构中,优选为,所述铪基铁电薄膜的掺杂元素为zr,al,la,y或si。

3、本发明的具有快速响应速度的铪基铁电叠层结构中,优选为,各层铪基铁电薄膜的zr:hf掺杂比例范围为1:1至2:8。

4、本发明的具有快速响应速度的铪基铁电叠层结构中,优选为,各层铪基铁电薄膜的厚度总和小于15nm。

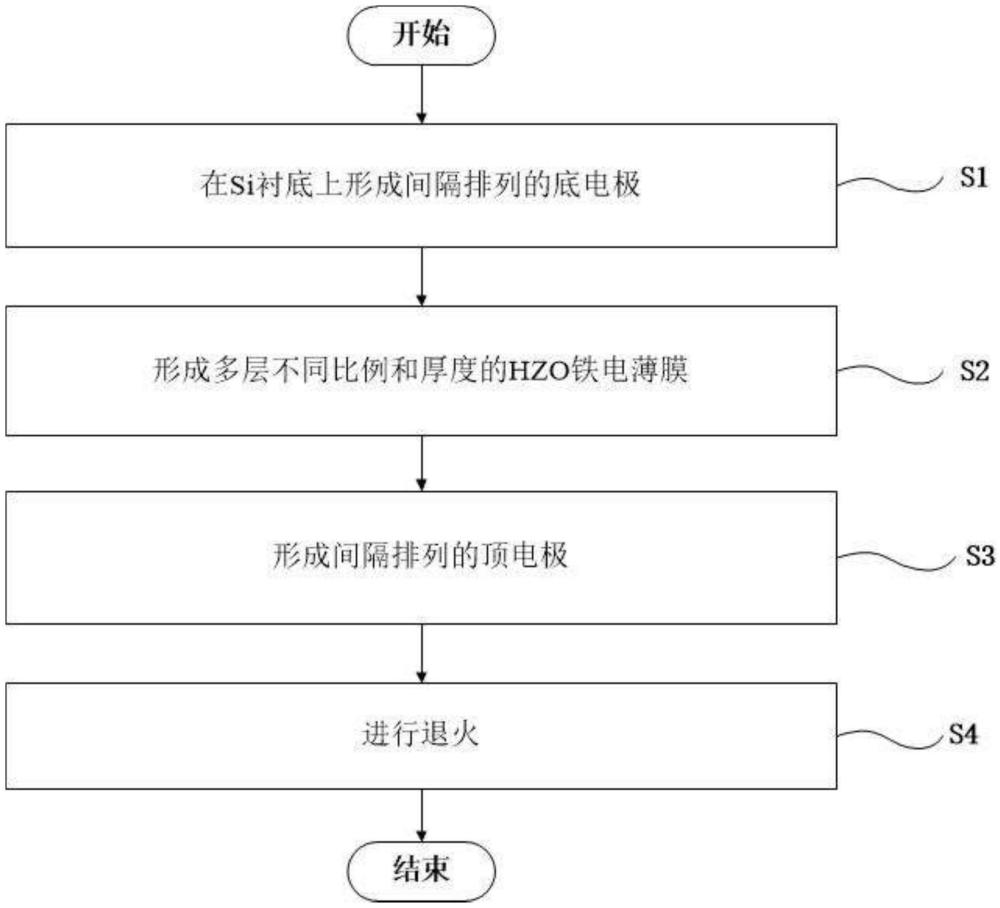

5、本发明还公开一种具有快速响应速度的铪基铁电叠层结构制备方法,包括以下步骤:在衬底上形成沿第一方向间隔排列的底电极;在所述底电极上形成不同掺杂比例和厚度的多层铪基铁电薄膜作为铁电功能叠层;在所述铁电功能叠层上形成沿第二方向间隔排列的顶电极,与第一方向垂直;进行快速热退火。

6、本发明的具有快速响应速度的铪基铁电叠层结构制备方法中,优选为,所述铪基铁电薄膜的掺杂元素为zr,al,la,y或si。

7、本发明的具有快速响应速度的铪基铁电叠层结构制备方法中,优选为,各层铪基铁电薄膜的zr:hf掺杂比例范围为1:1至2:8。

8、本发明的具有快速响应速度的铪基铁电叠层结构制备方法中,优选为,各层铪基铁电薄膜的厚度总和小于15nm。

9、有益效果:

10、采用等离子体增强原子层沉积(peald),通过精确调节hf和zr元素的生长比例,制备不同比例的hf和zr的混合氧化物(hfxzr1-xo)铁电薄膜,并将它们组合成叠层结构,从而降低翻转电场,无需引入其他元素掺杂,避免产生污染和漏电问题。

11、通过调节生长过程中的薄膜周期数和元素比例,可以轻松地控制叠层的厚度,以及叠层中不同层次的薄膜元素比例,从而探索不同结构对于提高hf基铁电薄膜速度和在低电场下获得更大极化强度的影响。这种精准的调控方法为优化铁电薄膜性能提供了有效途径,同时确保了材料的纯净性和电学特性的稳定性。

技术特征:

1.一种具有快速响应速度的铪基铁电叠层结构,其特征在于,

2.根据权利要求1所述的具有快速响应速度的铪基铁电叠层结构,其特征在于,

3.根据权利要求1所述的具有快速响应速度的铪基铁电叠层结构,其特征在于,

4.根据权利要求1所述的具有快速响应速度的铪基铁电叠层结构,其特征在于,

5.一种具有快速响应速度的铪基铁电叠层结构制备方法,其特征在于,

6.根据权利要求5所述的具有快速响应速度的铪基铁电叠层结构制备方法,其特征在于,

7.根据权利要求5所述的具有快速响应速度的铪基铁电叠层结构制备方法,其特征在于,

8.根据权利要求5所述的具有快速响应速度的铪基铁电叠层结构制备方法,其特征在于,

技术总结

本发明公开一种具有快速响应速度的铪基铁电叠层结构及其制备方法。该铪基铁电叠层结构,包括:衬底;底电极,形成在所述衬底上,沿第一方向间隔排列;铁电功能叠层,形成在所述底电极上,由不同掺杂比例的多层铪基铁电薄膜构成;顶电极,形成在所述铁电功能叠层上,沿第二方向间隔排列,与第一方向垂直。

技术研发人员:陈琳,宋逸凡,于佳杰,王晨,孙清清,张卫

受保护的技术使用者:复旦大学

技术研发日:

技术公布日:2024/12/30

- 还没有人留言评论。精彩留言会获得点赞!