用于供应时钟信号的电路的制作方法

本公开一般而言涉及用于供应时钟信号的电路以及相关联的方法。

背景技术:

1、大多数数字电路使用多个时钟信号来控制其操作的同步性。在使用这些电路时,从一个时钟信号到另一个时钟信号选择和传递需要特别注意产生毛刺(glitches)的风险。目前用于时钟信号选择的方案非常耗能并且较占用芯片表面面积。

技术实现思路

1、需要限制选择时钟信号期间产生毛刺,同时限制功耗和必要的芯片表面面积。

2、实施例克服了已知电子电路的全部或部分缺点。

3、实施例提供了一种用于供应时钟信号的电路,包括:

4、从多个时钟信号中选择一个信号的选择器;

5、选择器与用于输出所选择的时钟信号的节点之间的开关,

6、该电路被配置为使得施加用于选择时钟信号之一的控制信号依次导致关断开关、经由选择器选择信号、以及接通开关。

7、实施例提供了一种用于供应时钟信号的电路的操作方法,该方法包括作为施加用于选择信号的控制信号的结果的以下连续步骤:

8、-关断开关,该开关耦接从多个时钟信号中选择一个时钟信号的选择器和输出节点;

9、-经由选择器选择信号;以及

10、-接通开关。

11、在实施例中,该电路被配置为当检测到选择控制信号的变化时关断开关。

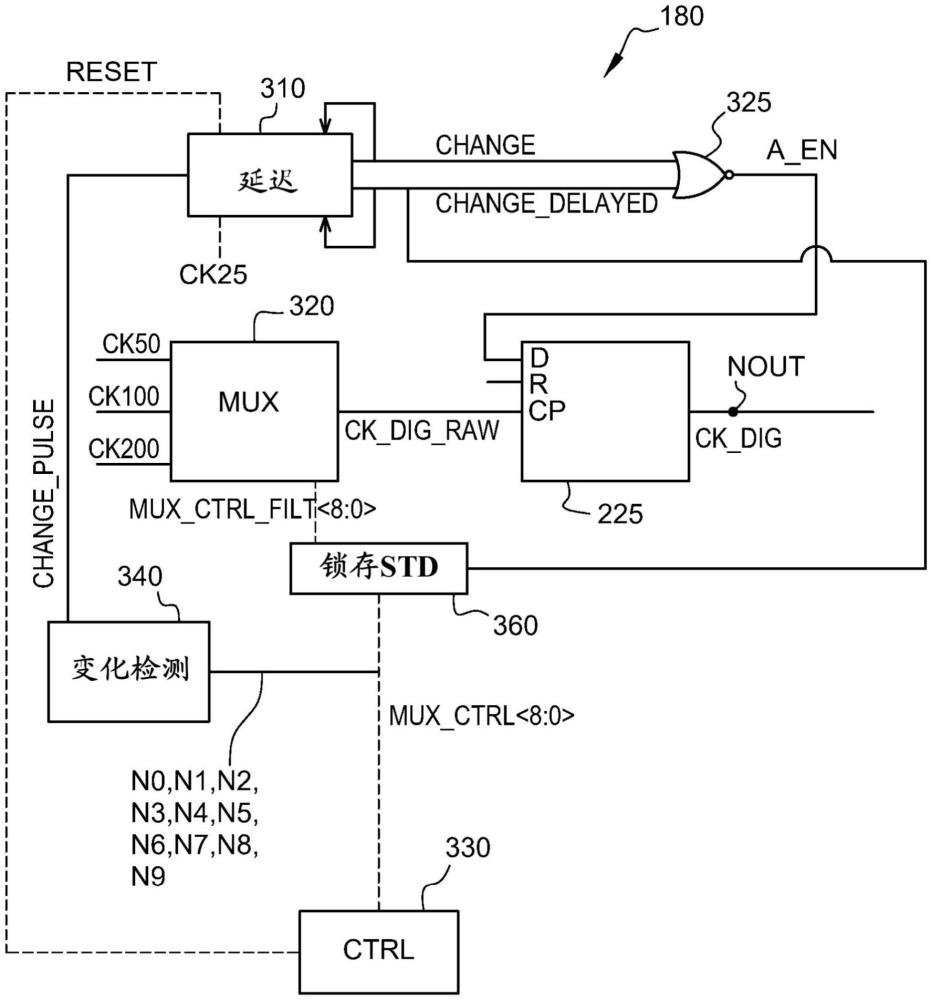

12、在实施例中,该电路被配置为在检测到变化后,在移位信号的至少两个上升沿的第一延迟之后选择信号。

13、在实施例中,该电路被配置为在选择后,在移位信号的至少两个上升沿的第二延迟之后接通开关。

14、在实施例中,电子电路被配置为当检测到变化时,使用第一电路生成第一信号。

15、在实施例中,该电路被配置为使用第二电路生成第二信号,第二信号源自第一信号并且在时间上移位第一延迟。

16、在实施例中,第二电路包括sr型锁存器,该sr型锁存器的输出端耦接到反相器,该反相器与包括至少两个级和/或延迟单元(cell)的移位寄存器的输入端串联;

17、第二信号在移位寄存器的输出端上生成;

18、sr型锁存器的第一输入端被配置为接收第一信号,并且sr型锁存器的第二输入端被配置为接收第二信号。

19、在实施例中,该电路包括第三电路,第三电路被配置为根据第一逻辑块的输出授权将选择控制信号传播到信号选择器,第一逻辑块能够基于反相器的输出端处存在的信号和第二信号执行nor功能。

20、在实施例中,第三电路包括形成选择控制信号的每个控制信号一个锁存器,每个锁存器具有:

21、耦接到第一逻辑块的输出端的门输入端,

22、被配置为接收对应控制信号的数据输入端,以及

23、耦接到信号选择器的输出端。

24、在实施例中,移位信号是频率小于或等于多个时钟信号中具有最小频率的信号的频率的时钟信号。

25、在实施例中,开关包括第一块,第一块具有:

26、耦接到选择器的时钟输入端,

27、耦接到第一逻辑块的输出端的第一使能输入端;以及

28、耦接到开关的第二块的第二使能输入端的输出端;并且

29、开关的第二块的输出端耦接到输出节点,并且第二块的时钟输入端耦接到选择器的输出端。

30、在实施例中,当第一逻辑块的输出处于低电平时,开关被配置为关断。

31、在实施例中,当第一逻辑块的输出处于高电平时,开关被配置为接通,然后所选择的时钟信号在输出节点上。

32、在实施例中,开关的第一块包括串联的第一触发器和第二触发器,第一块的时钟输入端是第一触发器的时钟输入端,并且第二触发器的输出端耦接到第二块的第二使能输入端。

33、实施例提供了一种微控制器,其包括用于供应诸如上文所述的时钟信号的电路。

技术特征:

1.一种用于供应时钟信号的电路,包括:

2.如权利要求1所述的电路,其中所述电路还被配置为在检测到选择控制信号的变化时关断开关。

3.如权利要求2所述的电路,其中所述电路还被配置为在检测到变化后,在移位信号的至少两个上升沿的第一延迟之后选择信号。

4.如权利要求3所述的电路,其中所述电路还被配置为在所述选择后,在移位信号的至少两个上升沿的第二延迟之后接通开关。

5.如权利要求2所述的电路,其中所述电路还被配置为当检测到变化时,使用第一电路生成第一信号。

6.如权利要求3所述的电路,其中所述电路还被配置为使用第二电路生成第二信号,第二信号源自第一信号,并且被时间移位了第一延迟。

7.如权利要求6所述的电路,其中第二电路包括:

8.如权利要求1所述的电路,所述电路包括第三电路,第三电路被配置为根据第一逻辑块的输出授权将选择控制信号传播到信号选择器,第一逻辑块能够基于反相器的输出端处存在的信号和第二信号执行nor功能。

9.如权利要求8所述的电路,第三电路包括形成选择控制信号的每个控制信号一个锁存器,每个锁存器具有:

10.如权利要求3所述的电路,其中所述移位信号是频率小于或等于所述多个时钟信号中具有最小频率的信号的频率的时钟信号。

11.如权利要求8所述的电路,其中所述开关包括第一块,所述第一块包括:

12.如权利要求8所述的电路,其中当第一逻辑块的输出处于低电平时,所述开关被配置为关断。

13.如权利要求1所述的电路,其中当第一逻辑块的输出处于高电平时,所述开关被配置为接通,所选择的时钟信号然后也出现在输出节点上。

14.如权利要求11所述的电路,其中所述开关的第一块包括串联的第一触发器和第二触发器,第一块的时钟输入是第一触发器的时钟输入,并且第二触发器的输出端耦接到第二块的第二使能输入端。

15.一种用于供应时钟信号的电路的操作方法,所述方法包括作为施加用于选择信号的选择控制信号的结果相继进行以下:

16.如权利要求15所述的方法,还包括当检测到选择控制信号的变化时关断开关。

17.如权利要求16所述的方法,还包括在检测到变化后,在移位信号的至少两个上升沿的第一延迟之后选择信号。

18.如权利要求17所述的方法,还包括在经由选择器选择信号之后,在移位信号的至少两个上升沿的第二延迟之后接通开关。

19.如权利要求16所述的方法,还包括当检测到变化时,使用第一电路生成第一信号。

20.一种微控制器,包括根据权利要求1所述的用于供应时钟信号的电路。

技术总结

本公开提供了用于供应时钟信号的电路。用于供应时钟信号的示例电路包括:从多个时钟信号中选择一个信号的选择器;选择器与用于输出所选择的时钟信号的节点之间的开关,该电路被配置为使得施加用于选择时钟信号之一的控制信号依次导致开关关断、经由选择器选择信号、以及接通开关。

技术研发人员:T·茹阿诺,L·S·F·英格尔

受保护的技术使用者:意法半导体国际公司

技术研发日:

技术公布日:2025/3/27

- 还没有人留言评论。精彩留言会获得点赞!