一种基于锁相环的模数转换实现方法

本发明属于cmos集成电路,具体涉及一种基于锁相环的模数转换实现方法。

背景技术:

1、如今随着cmos工艺尺寸的不断缩小,模拟电路的电压裕度不断减小,电压增益也逐渐降低,为了弥补这些损失而增大mos管的宽长比或者增加模拟电路的级数都将导致电路面积和功耗的大幅增加,给电路整体性能优化带来了困难。而数字电路在面对不断减小的cmos工艺尺寸时,具有更快的开关速度、更小的面积、更小的功耗,因此具有极大的优势。

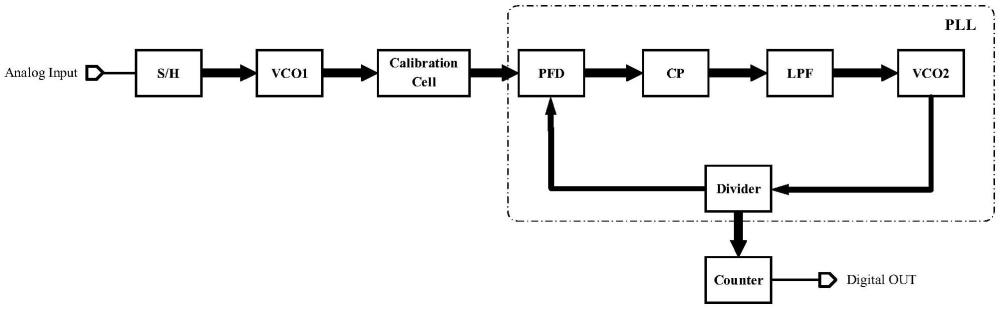

2、在模数转换器(analog digital converter,adc)技术领域,很多架构都需要模拟电路模块,例如比较器电路和数模转换电路,尤其是在高精度adc领域,对这些模拟电路提出了很高的要求,随着cmos尺寸不断减小,这些模拟电路需要不断迭代且设计难度越来越大。其中一个解决方法是降低adc中模拟电路模块的数量,一种基于压控振荡器(voltage-controlled oscillator,vco)的模数转换器如图1所示,它使用压控振荡器将输入信号的幅度信息转换为频率信息,然后使用计数器将频率信息转换为时间信息,时间信息用数字的二进制码表示即为数字信息,因此实现了从模拟信号到数字信号的模数转换。其中压控振荡器和计数器都可以用简单的数字模块构成。但这种结构存在一些问题:压控振荡器的输出连接一个大的计数器,其负载很大且会随着时间发生波动,因此压控振荡器的输出频率将不再是一个线性相关于输入信号幅度的常数,这将带来很大的非线性;此外,通常压控振荡器的输入输出呈近似线性变化的范围比较窄,而若需设计模数转换器,仅此线性区间可以利用,导致输入幅度范围较小;同时,由于压控振荡器的输入端直接连接输入模拟信号,因此不易判断压控振荡器输出信号频率达到稳定的时间节点,给后续计数器控制时钟的设计带来困难。

技术实现思路

1、针对以上问题,本发明提出了一种基于锁相环的模数转换实现方法。

2、本发明的技术方案如下:

3、一种基于锁相环的模数转换实现方法,其步骤包括:

4、1)将模拟信号analog input输入采样保持电路模块s/h,模拟信号analog input的幅度为αv,所述采样保持电路模块s/h的输出端与一压控振荡器vco1的输入端相连,所述压控振荡器vco1的输出信号频率与输入信号幅度呈正的线性关系,输出一固定频率信号;

5、2)所述压控振荡器vco1的输出端与校正单元calibration cell的输出端相连,将压控振荡器vco1的输出信号的频率固定为βhz,β=kvcoα,其中kvco=25mhz/v;

6、3)所述校正单元calibration cell的输出端与锁相环电路模块pll的输入端相连,利用锁相环电路模块pll将输出信号的频率βhz频率锁定为β·γhz,γ是一个定值;

7、4)所述锁相环电路模块pll的输出端与计数器模块counter的输入端相连,计数器模块counter在单位时间t内唯一对应输出一个二进制计数δ,作为数字输出digitaloutput。

8、进一步,所述αv的范围为0.5v至2.5v之间。

9、进一步,输入模拟信号analog input为正弦波形信号或斜坡模拟信号。

10、进一步,所述锁相环电路模块pll包括鉴频鉴相器模块pfd、电荷泵模块cp、低通滤波器模块lpf、压控振荡器模块vco2和分频器模块divider,其中,所述鉴频鉴相器模块pfd的第一输入端作为所述锁相环电路模块pll的输入端,所述鉴频鉴相器模块pfd的输出端与所述电荷泵模块cp的输入端相连,所述电荷泵模块cp的输出端与所述低通滤波器模块lpf的输入端相连,所述低通滤波器模块lpf的输出端与所述压控振荡器模块vco2的输入端相连,所述分频器模块divider的输入端与所述压控振荡器模块vco2的输出端相连,所述鉴频鉴相器模块pfd的第二输入端与所述分频器模块divider的输出端相连,所述分频器模块divider的输出端作为所述锁相环电路模块pll的输出端。

11、进一步,所述γ值与所述分频器divider的分频数相同。

12、进一步,所述锁相环模块为电荷泵锁相环或其他类型锁相环。

13、进一步,所述vco2使用loop-vco的结构,产生频率一致、相位不同的多个phase,然后通过分频器模块divider输出其中一或多个phase至等量的计数器模块counter,最后将一或多个计数器模块counter在单位时间t内的计数值全部累加,得到最终的计数输出。

14、本发明的技术效果在于:

15、第一,与传统的模数转换方法相比,本发明在电路中增加锁相环,通过合理调节输入输出关系,以及在压控振荡器和锁相环电路之间对信号进行校正,可以在较大输入范围内保证整体电路的线性度,具有更高的稳定性;

16、第二,现有基于压控振荡器的模数转换器通常需要较大的计数器,而本发明借助锁相环中的分频器缓解了后续计数器的压力,得到更数字化的电路;

17、第三,本发明在电路中增加了锁相环之后,可以通过查看锁相环中压控振荡器的输入信号电压变化来准确判断输出信号频率达到稳定的时间,再控制计数器开始工作;模数转换的分辨率理论上仅取决于计数器的时钟频率,时钟频率越高,分辨率越高,比较容易控制和估计。

技术特征:

1.一种基于锁相环的模数转换实现方法,其步骤包括:

2.如权利要求1所述的基于锁相环的模数转换实现方法,其特征在于,所述αv的范围为0.5v至2.5v之间。

3.如权利要求1所述的基于锁相环的模数转换实现方法,其特征在于,所述输入模拟信号analog input为正弦波形信号或斜坡模拟信号。

4.如权利要求1所述的基于锁相环的模数转换实现方法,其特征在于,所述锁相环电路模块pll包括鉴频鉴相器模块pfd、电荷泵模块cp、低通滤波器模块lpf、压控振荡器模块vco2和分频器模块divider,其中,所述鉴频鉴相器模块pfd的第一输入端作为所述锁相环电路模块pll的输入端,所述鉴频鉴相器模块pfd的输出端与所述电荷泵模块cp的输入端相连,所述电荷泵模块cp的输出端与所述低通滤波器模块lpf的输入端相连,所述低通滤波器模块lpf的输出端与所述压控振荡器模块vco2的输入端相连,所述分频器模块divider的输入端与所述压控振荡器模块vco2的输出端相连,所述鉴频鉴相器模块pfd的第二输入端与所述分频器模块divider的输出端相连,所述分频器模块divider的输出端作为所述锁相环电路模块pll的输出端。

5.如权利要求4所述的基于锁相环的模数转换实现方法,其特征在于,所述γ值与所述分频器divider的分频数相同。

6.如权利要求4所述的基于锁相环的模数转换实现方法,其特征在于,所述锁相环模块为电荷泵锁相环或其他类型锁相环。

7.如权利要求4所述的基于锁相环的模数转换实现方法,其特征在于,所述vco2使用loop-vco的结构,产生频率一致、相位不同的多个phase,然后通过分频器模块divider输出其中一或多个phase至等量的计数器模块counter,最后将一或多个计数器模块counter在单位时间t内的计数值全部累加,得到最终的计数输出。

技术总结

本发明公开了一种基于锁相环的模数转换实现方法,属于CMOS集成电路技术领域。本发明利用在电路中增加的锁相环,通过合理调节输入输出关系,以及在压控振荡器和锁相环电路之间对信号进行校正,可以在较大输入范围内保证整体电路的线性度,具有更高的稳定性;同时借助锁相环中的分频器缓解后续计数器的压力,得到更数字化的电路。且采用本发明可以通过查看锁相环中压控振荡器的输入信号电压变化来准确判断输出信号频率达到稳定的时间。

技术研发人员:蔡一茂,项文灏,胡伟,陈卓雅,王宗巍,王宇飞,赵仕耿,宋晨静

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2025/1/28

- 还没有人留言评论。精彩留言会获得点赞!