一种半导体器件的制作方法

本申请涉及半导体,尤其涉及一种半导体器件。

背景技术:

1、芯片常常指半导体分立器件芯片和集成电路芯片。其中,半导体分立器件包括半导体器件,而集成电路是指由多个半导体器件(如晶体管、电阻器、电容器等)及其连线按一定的电路形式制作在一块或几块半导体基片上,并具有一定功能的完整电路。

2、半导体器件包括二极管、三极管、非易失性存储器、晶闸管、光子器件、电阻和电容器件等。集成电路是由多个半导体器件及其连线按一定的电路形式制作在一块或几块半导体基片上形成。按集成电路中有源器件的结构类型和工艺技术分类,可将集成电路分为双极集成电路、mos集成电路和bi-mos(双极-mos混合型)集成电路等。其中,mos集成电路中,用来制作mos管的栅极是通过向多晶硅材料层中扩散(或注入)掺杂元素而形成的。

3、现有技术中,是在栅极氧化层薄膜制备完成之后进行多晶硅或者非晶硅沉积以制备多晶硅栅极。然后对多晶硅栅极扩散(或注入)掺杂元素b以制备pmos晶体管;掺杂元素注入掺杂后,沿着栅极多晶硅晶界进行扩散。掺杂元素沿着晶界持续扩散穿透栅极氧化层进入沟道区,这就使得半导体器件电性能发生很大的正向偏移,使得半导体器件的性能降低。

技术实现思路

1、本申请主要解决的技术问题是提供一种半导体器件,解决掺杂元素沿着晶界持续扩散穿透栅极氧化层进入有源区,使得半导体器件的性能降低的问题。

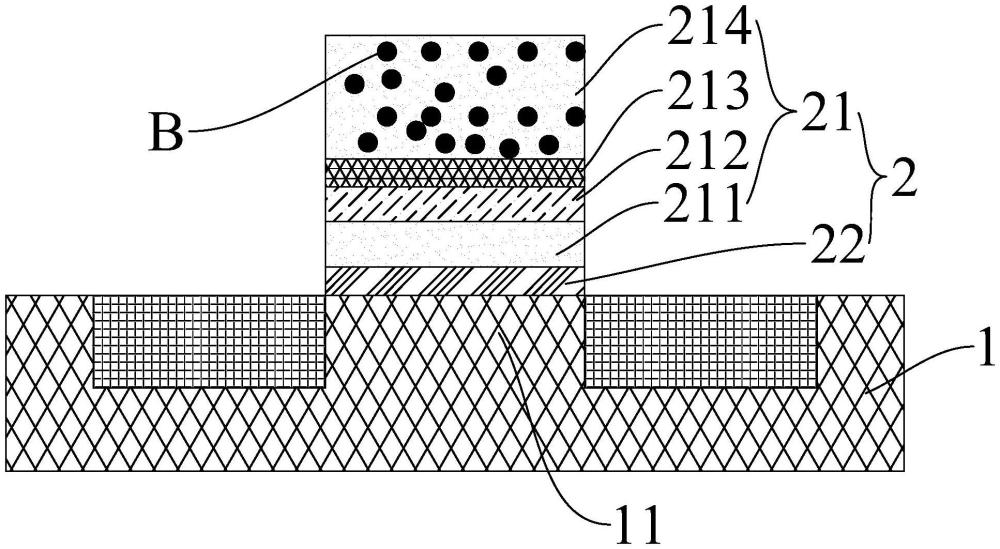

2、为解决上述技术问题,本申请采用的一个技术方案是提供一种半导体器件,包括有源区和设置于有源区上的电极结构层,电极结构层包括栅电极,栅电极包括在远离有源区的方向上依次堆叠的非晶隔离层和第一多晶层,非晶隔离层包括金属元素、iva族元素和氮元素的化合物,金属元素包括ti、co和ni中的一种或多种。

3、在一些实施例中,栅电极还包括:位于非晶隔离层与有源区之间的第二多晶层。

4、在一些实施例中,第一多晶层中掺杂有硼元素。

5、在一些实施例中,半导体器件为pmos晶体管,有源区包括沟道区,电极结构层还包括位于栅电极与沟道区之间的栅极绝缘层。

6、在一些实施例中,半导体器件为jfet晶体管,有源区包括栅极区,栅电极与栅极区之间形成欧姆接触。

7、在一些实施例中,iva族元素包括si元素。

8、在一些实施例中,非晶隔离层的厚度为100-300埃。

9、在一些实施例中,非晶隔离层的材料为axsiynz,a为金属元素,x+y+z=1,0.5<y<0.9。

10、在一些实施例中,第一多晶层在栅电极中厚度占比大于或等于70%。

11、在一些实施例中,第一多晶层中掺杂有c元素。

12、在一些实施例中,第二多晶层在栅电极中厚度占比小于或等于30%。

13、在一些实施例中,第二多晶层中掺杂有c元素。

14、在一些实施例中,栅电极还包括位于非晶隔离层与第二多晶层之间的氧化硅层。

15、本申请的有益效果是:本申请中,在有源区和第一多晶层之间设置非晶隔离层,通过非晶隔离层的非晶特性,阻碍第一多晶层中掺杂元素沿第一多晶层的晶界的扩散,实现对掺杂元素扩散阻碍的功能,避免因为掺杂元素沿着晶界持续扩散到达有源区,而导致半导体器件性能损失。

技术特征:

1.一种半导体器件,其特征在于,包括有源区和设置于所述有源区上的电极结构层,所述电极结构层包括栅电极,所述栅电极包括在远离所述有源区的方向上依次堆叠的非晶隔离层和第一多晶层,所述非晶隔离层包括金属元素、iva族元素和氮元素的化合物,所述金属元素包括ti、co和ni中的一种或多种。

2.如权利要求1所述的半导体器件,其特征在于,所述栅电极还包括:位于所述非晶隔离层与所述有源区之间的第二多晶层。

3.如权利要求1所述的半导体器件,其特征在于,所述第一多晶层中掺杂有硼元素。

4.如权利要求1-3之一所述的半导体器件,其特征在于,所述半导体器件为pmos晶体管,所述有源区包括沟道区,所述电极结构层还包括位于所述栅电极与所述沟道区之间的栅极绝缘层。

5.如权利要求1-3之一所述的半导体器件,其特征在于,所述半导体器件为jfet晶体管,所述有源区包括栅极区,所述栅电极与所述栅极区之间形成欧姆接触。

6.如权利要求1所述的半导体器件,其特征在于,所述iva族元素包括si元素。

7.如权利要求1所述的半导体器件,其特征在于,所述非晶隔离层的厚度为100-300埃。

8.如权利要求1所述的半导体器件,其特征在于,所述非晶隔离层的材料为axsiynz,a为所述金属元素,x+y+z=1,0.5<y<0.9。

9.如权利要求1所述的半导体器件,其特征在于,所述第一多晶层在所述栅电极中厚度占比大于或等于70%。

10.如权利要求1所述的半导体器件,其特征在于,所述第一多晶层中掺杂有c元素。

11.如权利要求2所述的半导体器件,其特征在于,所述第二多晶层在所述栅电极中厚度占比小于或等于30%。

12.如权利要求2所述的半导体器件,其特征在于,所述第二多晶层中掺杂有c元素。

13.如权利要求2所述的半导体器件,其特征在于,所述栅电极还包括位于所述非晶隔离层与所述第二多晶层之间的氧化硅层。

技术总结

本申请公开了一种半导体器件;包括有源区和设置于有源区上的电极结构层,电极结构层包括栅电极,栅电极包括在远离有源区的方向上依次堆叠的非晶隔离层和第一多晶层,非晶隔离层包括金属元素、IVA族元素和氮元素的化合物,金属元素包括Ti、Co和Ni中的一种或多种。本申请中,在有源区和第一多晶层之间设置非晶隔离层,通过非晶隔离层的非晶特性,阻碍第一多晶层中掺杂元素沿第一多晶层的晶界的扩散,实现对掺杂元素扩散阻碍的功能,避免因为掺杂元素沿着晶界持续扩散到达有源区,而导致半导体器件性能损失。

技术研发人员:张强

受保护的技术使用者:深圳市昇维旭技术有限公司

技术研发日:

技术公布日:2025/3/3

- 还没有人留言评论。精彩留言会获得点赞!