一种半导体放电管及其制作方法、过电压保护装置与流程

本发明涉及半导体,尤其涉及一种半导体放电管及其制作方法、过电压保护装置。

背景技术:

1、半导体放电管(thyristor surge suppressor,tss)是利用晶闸管原理制成的开关型保护器件。作为一种重要的保护器件,tss不仅可以吸收闪电、电源通断所产生的感应电压,还可以吸收由于高压线路与信号线路之间的意外接触或者错误操作所造成的过电压。

2、然而,现有的半导体放电管存在整体耐压性能低等问题。

技术实现思路

1、本发明提供了一种半导体放电管及其制作方法、过电压保护装置,可以提高半导体放电管的耐压性能,也可以扩大半导体放电管的锁定电压的范围。

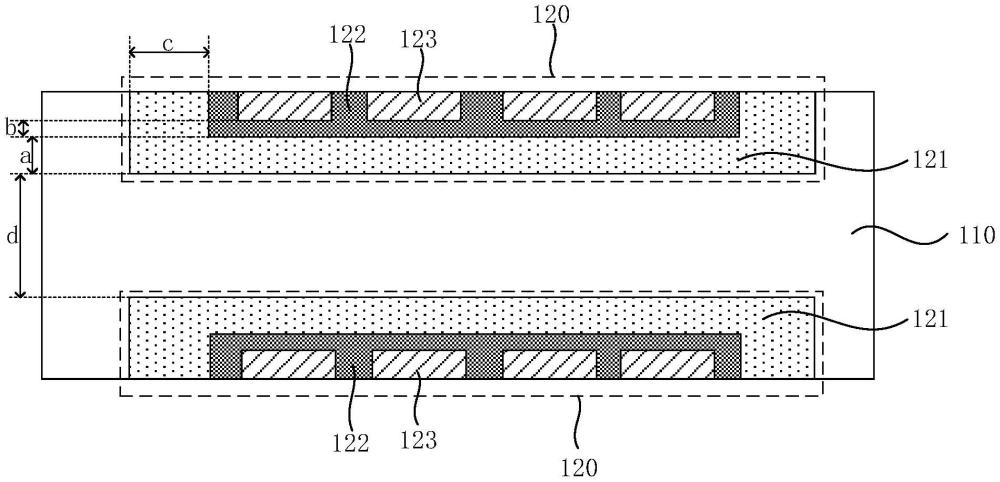

2、根据本发明的一方面,提供了一种半导体放电管,该半导体放电管包括:两个掺杂结构和具有第一导电类型的衬底;

3、所述衬底的第一侧与所述衬底的第二侧分别设置一所述掺杂结构;其中,所述衬底的第一侧与所述衬底的第二侧相对设置;

4、所述掺杂结构包括具有第二导电类型的第一掺杂区、具有第二导电类型的第二掺杂区以及至少一个具有所述第一导电类型的第三掺杂区;

5、所述第二掺杂区位于所述第一掺杂区内,所述第二掺杂区内的掺杂离子的浓度远大于所述第一掺杂区内的掺杂离子的浓度;

6、所述第三掺杂区位于所述第二掺杂区内。

7、可选的,所述衬底的厚度范围为150μm~450μm;

8、第一距离的范围为20μm~30μm;第二距离的范围为15μm~25μm,且第二距离小于第一距离;第三距离的范围为30μm~50μm;其中,所述第一距离为同一所述掺杂结构中所述第一掺杂区中靠近所述衬底的面距所述第二掺杂区中靠近所述衬底的面的距离;所述第二距离为同一所述掺杂结构中所述第二掺杂区中靠近所述衬底的面距所述第三掺杂区中靠近所述衬底的面的距离;所述第三距离为同一所述掺杂结构中所述第一掺杂区在所述衬底上的垂直投影的边界距所述第二掺杂区在所述衬底上的垂直投影的边界的距离。

9、可选的,所述掺杂结构还包括具有第一导电类型的掺杂环;

10、所述掺杂环环绕所述第一掺杂区;

11、所述第一掺杂区在所述衬底上的垂直投影覆盖所述掺杂环在所述衬底上的垂直投影的内边界,其中,所述掺杂环在所述衬底上的垂直投影的内边界为所述掺杂环在所述衬底上的垂直投影的所有边界中最靠近所述第二掺杂区的边界。

12、可选的,所述掺杂环内的掺杂离子的浓度的范围为1ω*cm~3ω*cm。

13、可选的,本实施例提供的半导体放电管还包括两层钝化层;

14、两个所述掺杂环远离所述衬底的一侧均设置一所述钝化层;

15、各所述钝化层均包括第一钝化子层、第二钝化子层和第三钝化子层;所述第一钝化子层位于所述掺杂环远离所述衬底的一侧;所述第二钝化子层位于所述第一钝化子层远离所述衬底的一侧;所述第三钝化子层位于所述第二钝化子层远离所述第一钝化子层的一侧;

16、所述第一钝化子层的材料包括四乙氧基硅烷,所述第二钝化子层的材料包括半绝缘多晶硅;所述第三钝化子层的材料包括二氧化硅。

17、可选的,所述掺杂结构包括至少三个间隔分布的所述第三掺杂区。

18、可选的,本实施例提供的半导体放电管还包括两层金属层;两个所述掺杂结构中的第三掺杂区远离所述衬底的一侧均设置有金属层。

19、可选的,所述第一导电类型为n型,所述第二导电类型为p型;或者,所述第一导电类型为p型,所述第二导电类型为n型。

20、根据本发明的另一方面,提供了一种半导体放电管的制作方法,该制作方法包括:

21、形成具有第一导电类型的衬底;

22、在所述衬底的第一侧与所述衬底的第二侧分别形成一掺杂结构;其中,所述衬底的第一侧与所述衬底的第二侧相对设置;所述掺杂结构包括具有第二导电类型的第一掺杂区、具有第二导电类型的第二掺杂区以及至少一个具有所述第一导电类型的第三掺杂区;所述第二掺杂区位于所述第一掺杂区内,所述第二掺杂区内的掺杂离子的浓度远大于所述第一掺杂区内的掺杂离子的浓度;所述第三掺杂区位于所述第二掺杂区内。

23、根据本发明的另一方面,提供了一种过电压保护装置,该过电压保护装置包括本发明任意实施例提供的半导体放电管。

24、本发明实施例提供了一种半导体放电管,该半导体放电管包括两层掺杂结构和具有第一导电类型的衬底。衬底的第一侧与衬底的第二侧均设置一掺杂结构。掺杂结构包括具有第二导电类型的第一掺杂区、具有第二导电类型的第二掺杂区以及至少一个具有第一导电类型的第三掺杂区。第二掺杂区位于第一掺杂区内,第三掺杂区位于第二掺杂区内。本实施例还设置了第二掺杂区内的掺杂离子的浓度远大于第一掺杂区内的掺杂离子的浓度,这样设置提高了短基区内的离子浓度,使得半导体放电管的抗雷击能力增强,也扩大了锁定电压的范围。综上,本实施例提供的半导体放电管,可以提高半导体放电管的耐压性能,也可以扩大半导体放电管的锁定电压的范围。

25、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种半导体放电管,其特征在于,包括:两个掺杂结构和具有第一导电类型的衬底;

2.根据权利要求1所述的半导体放电管,其特征在于,所述衬底的厚度范围为150μm~450μm;

3.根据权利要求1所述的半导体放电管,其特征在于,所述掺杂结构还包括具有第一导电类型的掺杂环;

4.根据权利要求3所述的半导体放电管,其特征在于,所述掺杂环内的掺杂离子的浓度的范围为1ω*cm~3ω*cm。

5.根据权利要求3所述的半导体放电管,其特征在于,还包括两层钝化层;

6.根据权利要求1所述的半导体放电管,其特征在于,所述掺杂结构包括至少三个间隔分布的所述第三掺杂区。

7.根据权利要求1所述的半导体放电管,其特征在于,还包括两层金属层;两个所述掺杂结构中的第三掺杂区远离所述衬底的一侧均设置有金属层。

8.根据权利要求1-7任一项所述的半导体放电管,其特征在于,所述第一导电类型为n型,所述第二导电类型为p型;或者,所述第一导电类型为p型,所述第二导电类型为n型。

9.一种半导体放电管的制作方法,其特征在于,包括:

10.一种过电压保护装置,其特征在于,包括权利要求1-8任一项所述的半导体放电管。

技术总结

本发明公开了一种半导体放电管及其制作方法、过电压保护装置。该半导体放电管包括:两个掺杂结构和具有第一导电类型的衬底;衬底的第一侧与衬底的第二侧分别设置一掺杂结构;其中,衬底的第一侧与衬底的第二侧相对设置;掺杂结构包括具有第二导电类型的第一掺杂区、具有第二导电类型的第二掺杂区以及至少一个具有第一导电类型的第三掺杂区;第二掺杂区位于第一掺杂区内,第二掺杂区内的掺杂离子的浓度远大于第一掺杂区内的掺杂离子的浓度;第三掺杂区位于第二掺杂区内。本发明提供了一种半导体放电管及其制作方法、过电压保护装置,可以提高半导体放电管的耐压性能,也可以扩大半导体放电管的锁定电压的范围。

技术研发人员:曹善通,管国栋,张常军,曾令珂

受保护的技术使用者:马鞍山市槟城电子有限公司

技术研发日:

技术公布日:2025/3/16

- 还没有人留言评论。精彩留言会获得点赞!